Inden for elektronik er det mest afgørende koncept, som hver komponent arbejder på, “ Logiske porte “. Da begrebet logiske porte er implementeret i enhver funktionalitet, såsom i integrerede kredsløb, sensorer, skifteformål, mikrokontrollere og processorer, kryptering og dekryptering og andre. Ud over disse er der brede anvendelser af Logic Gates. Der er mange typer logiske porte såsom Adder, Subtractor, Full Adder , Fuld subtraktor, Halv subtraktor og mange andre. Så denne artikel giver kollektiv information om halvt subtraktorkredsløb , halvt subtraktor sandhedstabel og relaterede begreber.

Hvad er Half Subtractor?

Før vi diskuterer halvtrækkeren, skal vi kende den binære subtraktion. I binær subtraktion svarer processen til subtraktion til aritmetisk subtraktion. I aritmetisk subtraktion bruges base 2-talsystemet, mens binær tal i binær subtraktion bruges til subtraktion. De resulterende vilkår kan betegnes med forskellen og låne.

Halv subtraktor er den mest essentielle kombinationslogisk kredsløb som bruges i digital elektronik . Dybest set er dette en elektronisk enhed eller med andre ord kan vi sige det som et logisk kredsløb. Dette kredsløb bruges til at udføre to binære cifre subtraktion. I den forrige artikel har vi allerede diskuteret begreberne halv adder og et fuldt adder kredsløb der bruger binære tal til beregningen. Tilsvarende bruger subtraktorkredsløbet binære tal (0,1) til subtraktion. Halv subtraktorens kredsløb kan bygges med to logiske porte, nemlig NAND- og EX-OR-porte . Dette kredsløb giver to elementer såsom forskellen såvel som de låner.

Som i binær subtraktion er hovedcifret 1, vi kan generere lån, mens subtrahend 1 er bedre end minuend 0, og på grund af dette vil lån have brug for. Følgende eksempel giver binær subtraktion af to binære bits.

Første ciffer | Andet ciffer | Forskel | Låne |

0 | 0 | 0 | 0 |

1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

I ovenstående subtraktion kan de to cifre repræsenteres med A og B. Disse to cifre kan trækkes fra og giver de resulterende bits som forskel og lån.

Når vi observerer de første to og fjerde rækker, er forskellen mellem disse rækker, så er forskellen og lånene ens, fordi subtrahend er mindre end minuend. Tilsvarende, når vi observerer den tredje række, trækkes minuendværdien fra subtrahend. Så forskellen og lånebit er 1, fordi subtrahend-cifret er bedre end minuend-cifret.

Dette kombinationskredsløb er et vigtigt redskab til enhver form for digitalt kredsløb at kende de mulige kombinationer af input og output. For eksempel, hvis subtraktoren har to indgange, vil de resulterende udgange være fire. O / p for halvtrækkeren er nævnt i nedenstående tabel, der betyder både forskellen og lånebiten. Kredsløbets sandhedstabel forklaring kan udføres ved hjælp af logiske porte som EX-ELLER logik gate og AND gate operation efterfulgt af NOT gate.

Løsning af sandhedstabellen ved hjælp af K-Map er vist nedenfor.

halvt subtraktor k kort

Det halvt subtraktorudtryk ved hjælp af sandhedstabel og K-map kan udledes som

Forskel (D) = ( x'y + xy ')

= x ⊕ y

Lån (B) = x’y

Logisk kredsløb

Det halvt subtraktor logisk kredsløb kan forklares ved hjælp af de logiske porte:

- 1 XOR-port

- 1 IKKE port

- 1 OG port

Repræsentationen er

Halvtrækker logisk kredsløb

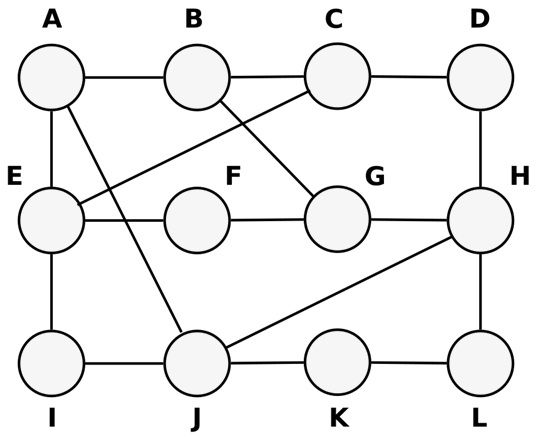

Blokdiagram for halvtrækker

Blokdiagrammet for halvtrækkeren er vist ovenfor. Det kræver to indgange samt giver to udgange. Her er input repræsenteret med A&B, og output er forskel og låntagning.

Ovenstående kredsløb kan designes med EX-OR & NAND-porte. Her kan NAND-porten bygges ved hjælp af AND og IKKE porte. Så vi kræver tre logiske porte til at lave et halvt subtraktorkredsløb, nemlig EX-OR-porten, IKKE-porten og NAND-porten.

En kombination af AND og NOT gate producerer en anden kombineret gate med navnet NAND Gate. Ex-ELLER gate-output vil være forskellen bit, og NAND Gate output vil være låne bit for de samme indgange A&B.

AND-porten

AND-gate er en type digital logisk gate med flere indgange og en enkelt udgang og baseret på inputkombinationerne vil den udføre den logiske sammenhæng. Når alle indgangene til denne port er høje, vil output være højt, ellers vil output være lavt. Logikdiagrammet for AND gate med sandhedstabel er vist nedenfor.

OG Port og sandhedstabel

IKKE port

NOT-gate er en type digital logisk gate med en enkelt indgang, og baseret på input vil output blive omvendt. For eksempel, når input til NOT gate er høj, vil output være lavt. Logikdiagrammet for NOT-gate med sandhedstabellen er vist nedenfor. Ved at bruge denne type logiske gate kan vi udføre NAND- og NOR-porte.

IKKE port og sandhedstabel

Ex-ELLER-port

Exclusive-OR eller EX-OR gate er en type digital logisk gate med 2-indgange og enkelt output. Funktionen af denne logiske port afhænger af ELLER porten. Hvis nogen af indgangene til denne port er høje, vil output fra EX-ELLER-porten være høj. Symbolet og sandhedstabellen for EX-OR er vist nedenfor.

XOR Gate and Truth Table

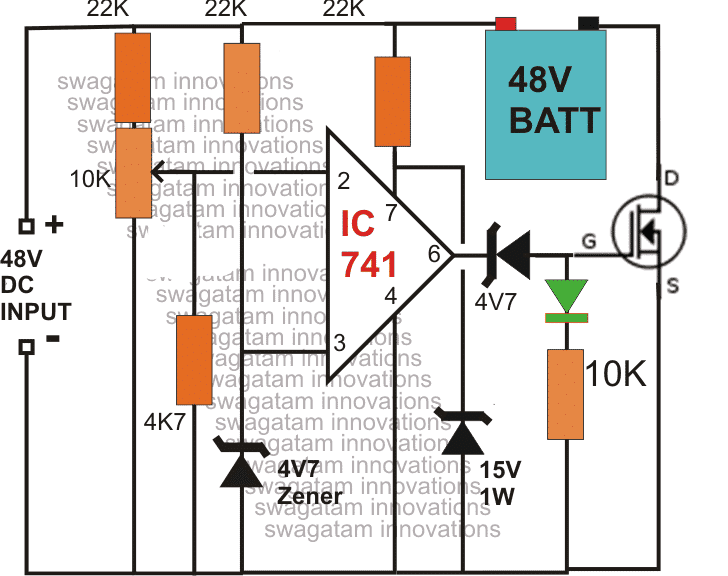

Halvtrækkerkredsløb ved hjælp af Nand Gate

Designet af subtraktoren kan udføres af ved hjælp af logiske porte ligesom NAND-porten & Ex-ELLER-porten. For at designe dette halve subtraktorkredsløb skal vi kende de to begreber, nemlig forskel og lån.

Halvtrækkerkredsløb ved hjælp af Nand Gate

Hvis vi overvåger forsigtigt, er det ret klart, at den række operationer, der udføres af dette kredsløb, der er nøjagtigt relateret til EX-ELLER gate-operationen. Derfor kan vi simpelthen bruge EX-OR-porten til at gøre forskel. På samme måde kan lånet, der produceres af halvt adderkredsløb, simpelthen opnås ved hjælp af blandingen af logiske porte som AND-gate og NOT-gate.

Denne HS kan også designes ved hjælp af NOR-porte, hvor det kræver 5 NOR-porte til konstruktionen. Kredsløbsdiagrammet halvtrækker ved hjælp af NOR-porte er vist som:

Halvtrækker med Nor Gates

Sandhedstabel

Første bit | Anden bit | Forskel (EX-ELLER ud) | Låne (NAND ud) |

0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 0 |

VHDL og testbench-kode

VHDL-koden for halvtrækker forklares som følger:

bibliotek IEEE

brug IEEE.STD_LOGIC_1164.ALL

brug IEEE.STD_LOGIC_ARITH.ALL

brug IEEE.STD_LOGIC_UNSIGNED.ALL

enhed Half_Sub1 er

Port (a: i STD_LOGIC

b: i STD_LOGIC

HS_Diff: ud STD_LOGIC

HS_Borrow: ud STD_LOGIC)

afslut Half_Sub1

arkitektur Behavioral af Half_Sub1 er

begynde

HS_Diff<=a xor b

HS_Lån<=(not a) and b

Det testbænk kode til HS forklares som nedenfor:

BIBLIOTEK IEEE

BRUG ieee.std_logic_1164.ALL

ENTITY HS_tb IS

SLUT HS_tb

ARKITEKTUR HS_tb AF HS_tb IS

KOMPONENT HS

PORT (a: IN std_logic

b: IN std_logic

HS_Diff: OUT std_logic

HS_Borrow: OUT std_logic

)

SLUTKOMPONENT

signal a: std_logic: = ‘0’

signal b: std_logic: = ‘0’

signal HS_Diff: std_logic

signal HS_Borrow: std_logic

BEGYNDE

nyt: HS PORT MAP (

a => a,

b => b,

HS_Diff => HS_Diff,

HS_borrow => HS_borrow

)

stim_proc: proces

begynde

til<= ‘0’

b<= ‘0’

vent 30 ns

til<= ‘0’

b<= ‘1’

vent 30 ns

til<= ‘1’

b<= ‘0’

vent 30 ns

til<= ‘1’

b<= ‘1’

vente

afslutte processen

ENDE

Fuld subtraktor ved hjælp af halv subtraktor

En fuld subtraktor er en kombinationsenhed, der styrer subtraktionsfunktionaliteten ved hjælp af to bits og er minuend og subtrahend. Kredsløbet betragter lånet som det foregående output, og det har tre indgange med to udgange. De tre indgange er minuend, subtrahend og input modtaget fra den tidligere output, som er lånt, og de to output er forskellen og lån.

Fuldt subtraktorlogisk diagram

Sandhedstabellen til fuld subtraktor er

| Indgange | Udgange | |||

| x | Y | Yin | FS_Diff | FS_Lån |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Med ovenstående sandhedstabel er det logiske diagram annonces kredsløbsdiagram til implementering af fuld subtraktor ved hjælp af halve subtraktorer vist nedenfor:

Fuld subtraktor ved hjælp af HS

Fordele og begrænsninger ved Half Subtractor

Fordelene ved halv subtraktor er:

- Implementeringen og konstruktionen af dette kredsløb er enkel og nem

- Dette kredsløb bruger minimal strøm i digital signalbehandling

- beregningsfunktioner kan udføres ved forbedrede hastighedshastigheder

Begrænsningerne ved dette kombinationskredsløb er:

Selvom der er omfattende anvendelser af halvtrækker i mange operationer og funktionaliteter, er der få begrænsninger, og de er:

- Halvtrækningskredsløbene accepterer ikke 'Lån-i' fra de tidligere output, hvor dette er den afgørende ulempe ved dette kredsløb

- Da mange realtidsapplikationer fungerer på subtraktion af talrige antal bits, har halve subtraktoranordninger ingen mulighed for at trække mange bits

Anvendelser af Half Subtractor

Anvendelserne af halv subtraktor inkluderer følgende.

- Halv subtraktor bruges til at reducere kraften af lyd- eller radiosignaler

- Det kan være bruges i forstærkere for at reducere lydforvrængningen

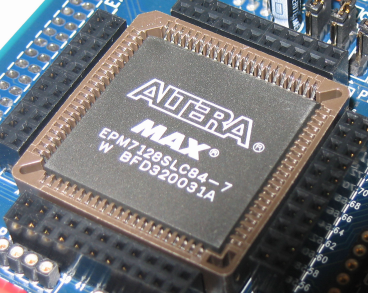

- Halv subtraktor er bruges i ALU af processoren

- Det kan bruges til at øge og formindske operatorer og beregner også adresserne

- Halv subtraktor bruges til at trække de mindst signifikante kolonnetal. Til subtraktion af flercifrede tal kan den bruges til LSB.

Derfor kan vi endelig fra ovenstående halvtrækkerteori lukke, at ved at bruge dette kredsløb kan vi trække fra en binær bit fra en anden for at give output som forskel og lån. På samme måde kan vi designe halvtrækker ved hjælp af NAND-porte kredsløb såvel som NOR-porte. De andre begreber, der skal kendes, er hvad der er halve subtraktor verilog kode og hvordan RTL-skematisk diagram kan tegnes?