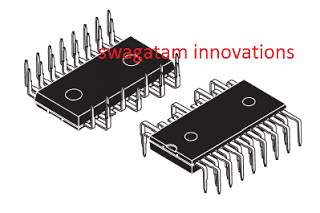

Designprocessen for digital hardware har transformeret intenst i løbet af de sidste par år. Så små digitale kredsløb kan implementeres ved hjælp af PAL'er og PLA'er. Hver enhed bruges at implementere forskellige kredsløb der ikke har brug for mere end antallet af i / ps, o / ps og produktbetingelser, der tilbydes i den specifikke chip. Disse chips er utilstrækkelige til temmelig beskedne størrelser, der normalt understøtter et gensidigt antal input og output på ikke mere end 32. Til design af disse kredsløb, der har brug for flere input og output, kan enten mange PLA'er / PAL'er anvendes eller ellers en mere klassisk type af chip kan bruges kaldet en CPLD (kompleks programmerbar logisk enhed). En CPLD-chip indeholder flere kredsløbsblokke på en enkelt chip med indvendige ledningsressourcer til at fastgøre kredsløbsblokkene. Hver kredsløbsblok kan sammenlignes med en PLA eller en PAL.

Hvad er en kompleks programmerbar logisk enhed?

Forkortelsen af CPLD er “Komplekse programmerbare logiske enheder”, det er en slags integreret kredsløb at applikationsdesignere designer for at implementere digital hardware som mobiltelefoner. Disse kan håndtere bevidst højere designs end SPLD'er (enkle programmerbare logiske enheder), men tilbyder mindre logik end FPGA'er ( feltprogrammerbare portarrays CPLD'er inkluderer adskillige logiske blokke, hver af blokke inkluderer 8-16 makroceller. Fordi hver logikblok udfører en bestemt funktion, er alle makroceller i en logikblok fuldt tilsluttet. Afhængig af brugen kan disse blokke muligvis være forbundet med hinanden.

Kompleks programmerbar logisk enhed

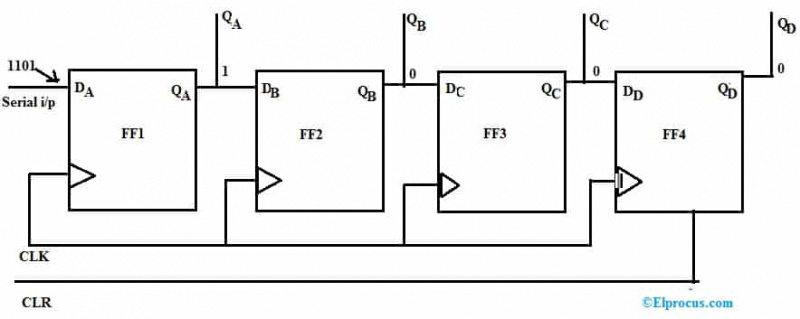

De fleste CPLD'er (komplekse programmerbare logiske enheder) har makroceller med en sum af logisk funktion og et valgfag FF (flip-flop) . Afhængigt af chippen understøtter den kombinatoriske logikfunktion fra 4 til 16 produkttermer med inklusiv fan-in. CPLD'er adskiller sig også med hensyn til skiftregistre og logiske porte. Af denne grund kan CPLD'er med et stort antal logiske porte bruges i stedet for FPGA'er. En anden CPLD-specifikation angiver antallet af produktudtryk, som en macrocell kan udrette. Produktbetingelser er produktet af digitale signaler, der udfører en bestemt logikfunktion.

CPLD'er fås i flere IC-pakkeformularer og logiske familier. CPLD'er adskiller sig også med hensyn til forsyningsspænding, driftsstrøm, standbystrøm og strømafbrydelse. Derudover kan disse opnås med forskellige mængder hukommelse og forskellige former for hukommelsesstøtte. Normalt udtrykkes hukommelse i bits / megabit. Hukommelsessupport består af ROM, RAM og dual-port RAM. Det består også af CAM (indholdsadresserbar hukommelse) samt FIFO (først ind, først ud) hukommelse og LIFO (sidste ind, sidste ud) hukommelse.

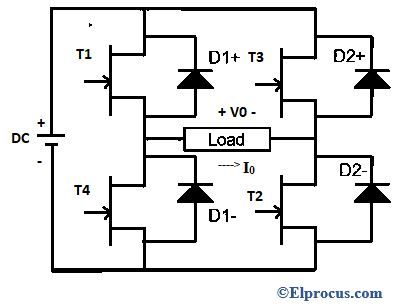

Arkitektur af komplekse programmerbare logiske enheder

En kompleks programmerbar logisk enhed består af en gruppe af programmerbare FB'er (funktionelle blokke). Indgangene og udgangene til disse funktionelle blokke er forbundet sammen med en GIM (global sammenkoblingsmatrix). Denne sammenkoblingsmatrix kan omkonfigureres, så vi kan ændre kontakterne mellem de funktionelle blokke. Der vil være nogle input- og outputblokke, der lader os forene CPLD til den eksterne verden. CPLDs arkitektur er vist nedenfor.

Generelt ser den programmerbare FB ud som vifte af logiske porte hvor en række AND-porte kan programmeres og ELLER-porte er stabile. Men hver producent har deres måde at tænke på at designe den funktionelle blok. En angivet o / p kan findes ved at betjene de feedback-signaler, der opnås fra ELLER gateudgangene.

CPLD-arkitektur

I CPLD-programmering kodes designet først på Verilog- eller VHDL-sprog, når koden er (simuleret og syntetiseret. Under syntese håndplukkes CPLD-modellen (målenheden), og der fremstilles en teknologibaseret kortlægningsliste. Denne liste kan være tæt på -tilpasning til den ægte CPLD-arkitektur ved hjælp af en sted- og ruteproces, typisk opnået af sted-og-rute-software fra CPLD Company's proprietære. Derefter foretager operatøren nogle bekræftelsesprocesser. Hvis alt er godt, bruger han CPLD, ellers han vil omarrangere det.

Arkitekturproblemer med CPLD

Når man overvejer en kompleks programmerbar logisk enhed til brug i design, er der nogle af følgende arkitekturproblemer, der kan tages i betragtning

- Programmeringsteknologien

- Funktionsblokfunktionen

- I / O-kapaciteten

Nogle af familierne fra CPLD fra forskellige detailhandlere inkluderer

- Altera MAX 7000 og MAX 9000 familier

- Atmel ATF- og ATV-familier

- Gitter isp LSI familie

- Gitter (Vantis) MACH familie

- Xilinx XC9500 familie

Familier af CPLD

Anvendelser af CPLD

Anvendelserne af CPLD'er inkluderer følgende

- Komplekse programmerbare logiske enheder er ideelle til kritiske kontrolapplikationer med høj ydeevne.

- CPLD kan bruges i digitalt design til at udføre bootloaderens funktioner

- CPLD bruges til at indlæse konfigurationsdataene for et feltprogrammerbart gate array fra ikke-flygtig hukommelse.

- Generelt bruges disse i små designapplikationer som adressekodning

- CPLD'er bruges ofte mange applikationer som i omkostningsfølsomme, batteridrevne bærbare enheder på grund af dens lave størrelse og brug af lav strøm.

Således handler alt om kompleks programmerbar logisk enhedsarkitektur og dens applikationer. Vi håber, at du har fået en bedre forståelse af dette koncept. Desuden er spørgsmål vedrørende dette koncept eller at gennemføre elektriske og elektroniske projekter , bedes du give dine værdifulde forslag ved at kommentere i kommentarfeltet nedenfor. Her er et spørgsmål til dig, hvad er forskellen mellem CPLD og FPGA?

Fotokreditter:

- CPLD wikimedia

- Arkitektur af CPLD slidesharecdn