Generelt er den fulde subtraktor en af de mest anvendte og væsentlige kombinationslogiske kredsløb . Det er en grundlæggende elektronisk enhed, der bruges til at udføre subtraktion af to binære tal. I den tidligere artikel har vi allerede givet den grundlæggende teori om halv adder & en fuld adder der bruger de binære cifre til beregningen. Ligeledes bruger fuldtrækkeren binære cifre som 0,1 til subtraktionen. Kredsløbet for dette kan bygges med logiske porte som OR, Ex-OR, NAND gate. Indgangene til denne subtraktor er A, B, Bin og output er D, Bout.

Denne artikel giver en fuld-subtraktor-teoriidee, der omfatter forudsætningerne som hvad der er en subtraktor, design med logiske porte, sandhedstabel osv. Denne artikel er nyttig for ingeniørstuderende, der kan gennemgå disse emner i HDL Practical lab.

Hvad er en subtraktor?

Subtraktion med binære cifre kan udføres ved hjælp af subtraktorkredsløbet. Dette er en slags kombinationslogisk kredsløb, der bruges til at udføre subtraktion af to binære cifre som 0s og 1s. Subtraktion af binære cifre fra 0 til 0 eller 0 til 1 ændrer ikke resultatet, subtraktion af 1 til 1 vil resultere i 0, men subtraktionen fra 1 til 0 skal lånes.

For eksempel inkluderer to-bit subtraktorkredsløbet to indgange som A & B, mens output er forskel og lån. Dette kredsløb kan bygges med tilføjere sammen med invertere, der er placeret blandt hver dataindgang samt låne (Bin) input fra den tidligere fase af FA.

Subtraktorer er klassificeret i to typer som halvt subtraktor og fuld subtraktor. Her diskuterer vi hele subtraktoren.

Hvad er en fuld subtraktor?

Det er en elektronisk enhed eller logisk kredsløb der udfører subtraktion af to binære cifre. Det er et kombinationslogisk kredsløb, der anvendes i digital elektronik. Mange kombinationskredsløb er tilgængelige i integreret kredsløbsteknologi nemlig addere, kodere, dekodere og multiplexere. I denne artikel skal vi diskutere dens konstruktion ved hjælp af en halv subtraktor og også udtryk som sandhedstabel.

Fuld subtraktor

Designet af dette kan gøres med to halve subtraktorer, som involverer tre indgange såsom minuend, subtrahend og lån, lånebit blandt inputene opnås ved subtraktion af to binære cifre og trækkes fra det næste par af højere orden af bits, output som forskel og lån.

Det fuldt subtraktorblokdiagram er vist nedenfor. Den største ulempe ved halvtrækkeren er, at vi ikke kan lave en lånebit i denne subtraktor. Mens vi i dets design faktisk kan lave en lånebit i kredsløbet og kan trække med de resterende to i / ps. Her er A minuend, B er subtrahend & Bin lånes ind. Outputene er Difference (Diff) & Bout (Borrow out). Det komplette subtraktorkredsløb kan opnås ved at bruge to halve subtraktorer med en ekstra ELLER-port.

Fuldt subtraktorkredsløbsdiagram med logiske porte

Det kredsløbsdiagram over den fulde subtraktor ved hjælp af grundport s er vist i det følgende blokdiagram. Dette kredsløb kan udføres med to halvtrækkerkredsløb.

I det indledende halv-subtraktorkredsløb er de binære indgange A og B. Som vi har diskuteret i den forrige halv-subtraktor-artikel, vil det generere to output, nemlig forskel (Diff) & Låne.

Fuld subtraktor ved hjælp af logiske porte

Forskellen o / p for den venstre subtraktor gives til venstre halv-subtraktorkredsløb. Diff-output tilvejebringes yderligere til indgangen på det højre halve subtraktorkredsløb. Vi tilbød lånet i bit på tværs af det andet i / p af det næste halvt subtraktorkredsløb . Endnu en gang vil det give Diff ud såvel som Lån lidt ud. Den endelige output for denne subtraktor er Diff-output.

På den anden side er lånet fra begge de halve subtraktorkredsløb forbundet til ELLER logikporten. Senere end at give ELLER logik for to outputbits af subtraktoren, erhverver vi den endelige Lån ud af subtraktoren. Den sidste lånte ud for at betegne MSB (en meget vigtig bit).

Hvis vi observerer det interne kredsløb i dette, kan vi se to halvtrækkere med NAND-port og XOR-port med en ekstra ELLER-port.

Fuld subtraktor sandhedstabel

Det her subtraktorkredsløb udfører en subtraktion mellem to bits, som har 3 indgange (A, B og Bin) og to udgange (D og Bout). Her angiver indgangene minuend, subtrahend & tidligere lån, mens de to output er betegnet som lån o / p og forskel. Det følgende billede viser sandhedstabellen for fuldtrækkeren.

Indgange | Udgange | |||

Minuend (A) | Subtrahend (B) | Lån (skraldespand) | Forskel (D) | Lån (Bout) |

0 | 0 | 0 | 0 | 0 |

0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

K-Map

Forenkling af fuld subtraktor K-kort for ovenstående forskel og lån er vist nedenfor.

Ligningerne for forskellen såvel som Bin er nævnt nedenfor.

Udtrykket for forskel er,

D = A'B'Bin + AB'Bin '+ A'BBin' + ABBin

Udtrykket for Lån er,

Bout = A'Bin + A'B + BBin

Cascading of Full Subtractor Circuit

Tidligere har vi diskuteret en oversigt over dette som konstruktion, kredsløbsdiagram med logiske porte. Men hvis vi ønsker at trække to ellers mere 1-bit tal, er dette subtraktorkredsløb meget nyttigt at kaskade enkelt bit tal og trækker også mere end to binære tal. I sådanne tilfælde bruges et fuldt adderende kaskadekredsløb ved hjælp af IKKE logisk gate. Konverteringen af kredsløbet fra fuld adder til fuld subtraktor kan ske ved hjælp af 2's komplementteknik.

Inverter generelt subtrahend-indgangene til den fulde adder ved hjælp af IKKE gate ellers en inverter. Ved at tilføje denne Minuend (ikke-inverteret input) & Subtrahend (Inverteret input) er LSB (bæreindgang) på FA-kredsløbet 1, hvilket betyder Logik høj, ellers trækker vi to binære cifre ved hjælp af 2's komplementteknik. FA's output er Diff bit, og hvis vi inverterer udførelsen, kan vi få MSB ellers låne bit. Faktisk kan vi designe kredsløbet, så output kan observeres.

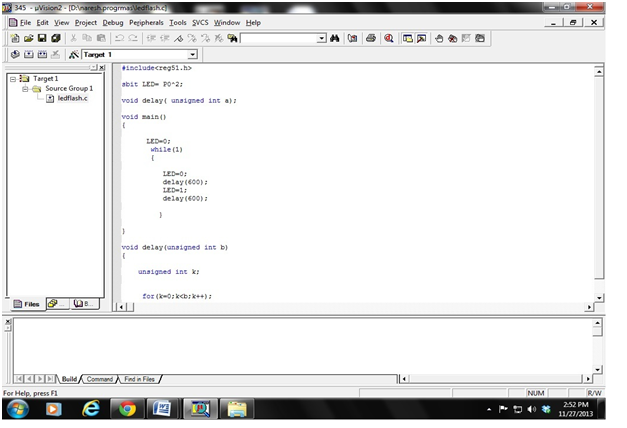

Verilog-kode

For kodningsdelen skal vi først kontrollere den strukturelle måde at modellere det logiske kredsløbsdiagram på. Logikdiagrammet for dette kan bygges ved hjælp af en AND-port, halve subtraktorkredsløb og kombinationen af logiske porte som AND, ELLER, IKKE, XOR-porte. Som i strukturel modellering forklarer vi forskellige moduler til ethvert grundlæggende elementært arrangement. I den følgende kode kan forskellige moduler defineres for hver gate.

Dette modul er til ELLER-porten.

INDGANG: a0, b0

UDGANG: c0

Endelig forener vi disse gate-nøjagtige moduler til et eneste modul. Til det her bruger vi instantiering af modulet. Nu kan denne instantiering bruges, når vi først vil replikere et nøjagtigt modul eller en funktion til forskellige indgangssæt. Først designer vi en halv subtraktor, hvorefter dette modul bruges til at implementere en fuld subtraktor. Til implementering af dette bruger vi OR-porten til at kombinere o / ps for variablen Bout. Det verilog-kode for den fulde subtraktor er vist nedenfor

modul eller_gate (a0, b0, c0)

input a0, b0

output c0

tildel c0 = a0 | b0

endmodul

modul xor_gate (a1, b1, c1)

input a1, b1

udgang c1

tildel c1 = a1 ^ b1

endmodul

modul og_gate (a2, b2, c2)

input a2, b2

udgang c2

tildel c2 = a2 & b2

endmodul

modul not_gate (a3, b3)

input a3

output b3

tildel b3 = ~ a3

endmodul

modul halvsubtraktor (a4, b4, c4, d4)

input a4, b4

output c4, d4

ledning x

xor_gate u1 (a4, b4, c4)

og_gate u2 (x, b4, d4)

not_gate u3 (a4, x)

endmodul

modul fuld_subtraktor (A, B, Bin, D, Bout)

input A, B, Bin

output D, Bout

ledning p, q, r

halv_subtraktor u4 (A, B, p, q)

halv_subtraktor u5 (p, Bin, D, r)

eller_gate u6 (q, r, Bout)

endmodul

Fuld subtraktor ved hjælp af 4X1 Multiplexer

Udførelsen af subtraktion kan ske gennem de to komplementmetode. Således kræver vi brug af en 1-XOR-port, der bruges til at invertere 1-bit og inkludere en i bærebit. Udgangen af DIFFERENCE svarer til output SUM i det fulde adderkredsløb, men BARROW o / p svarer ikke til den fulde adderes bæreoutput, men det er inverteret såvel som komplimenteret, som A - B = A + (-B) = A + to's komplement af B.

Designet af dette ved hjælp af 4X1 multiplexer er vist i det følgende logiske diagram. Dette design kan udføres ved hjælp af følgende trin.

4X1 Multiplexer

- I trin 1 er der to output som Sub og Lån. Så vi er nødt til at vælge 2 multiplexere.

- I trin 2 kan sandhedstabellen implementeres sammen med K-maps

- I trin 3 kan de to variabler vælges som din valgte linje. For eksempel er B & C i dette tilfælde.

Sandhedstabel

Det sandhedstabel over fuld subtraktor kredsløb ved hjælp af 4X1 multiplexer inkluderer følgende

TIL | B | C | Sub | Låne |

0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

1 | 1 | 1 | 1 | 1 |

Fuld subtraktor ved hjælp af dekoder

Designet af en fuld subtraktor ved hjælp af 3-8 dekodere kan udføres ved hjælp af aktive lave udgange. Lad os antage, at dekoder fungerer ved hjælp af følgende logiske diagram. Dekoderen inkluderer tre indgange i 3-8 dekodere. Baseret på sandhedstabellen kan vi skrive mintermerne for output af forskel & lån.

Fra ovenstående sandhedstabel

For de forskellige funktioner i sandhedstabellen kan mintermerne skrives som 1,2,4,7, og ligeledes for lånet kan mintermerne skrives som 1,2,3,7. 3-8 dekodere inkluderer tre indgange samt 8 udgange lik0 til 7 numre.

3 til 8 dekoder

Hvis input fra subtraktoren er 000, vil output '0' være aktivt, og hvis input er 001, vil output '1' være aktiv.

Nu kan subtraktorens output tages fra 1, 2, 4 & 7 for at forbinde den til en NAND-gate, så vil output være forskellen. Disse udgange kan forbindes til andre NAND-logiske porte, hvor output ændres til lånet.

For eksempel, hvis indgangen er 001, vil udgangen være 1, hvilket betyder, at den er aktiv. Så output er aktivt lavt, og output kan fås fra NAND gate kaldet forskel funktion som høj og låne funktion skifter også til at være høj. Derfor får vi det foretrukne output. Så endelig fungerer dekoderen som en fuld subtraktor.

Fordele og ulemper

Det fordelene ved subtraktoren inkluderer følgende.

- Designet af subtraktoren er meget enkel såvel som implementere

- Effektfradrag inden for DSP (digital signalbehandling)

- Beregningsopgaver kan udføres i høj hastighed.

Det ulemperne ved subtraktoren inkluderer følgende.

- I halvtrækkeren er der ingen betingelse for at acceptere lånelignende input fra den tidligere fase.

- Subtraktorhastigheden kan være delvis gennem forsinkelsen i kredsløbet.

Ansøgninger

Nogle af anvendelser af fuld subtraktor inkluderer følgende

- Disse bruges generelt til ALU (aritmetisk logisk enhed) i computere til at trække fra som CPU og GPU til applikationer af grafik for at mindske kredsløbsvanskeligheden.

- Subtraktorer bruges mest til at udføre aritmetiske funktioner som subtraktion i elektroniske lommeregnere såvel som digitale enheder.

- Disse gælder også for forskellige mikrokontroller til aritmetisk subtraktion, timere og programtælleren (PC)

- Subtraktorer bruges i processorer til at beregne tabeller, adresser osv.

- Det er også nyttigt til DSP og netværksbaserede systemer.

- Disse bruges hovedsageligt til ALU inden for computere til fratrækning som CPU & GPU til grafiske applikationer for at reducere kredsløbets kompleksitet.

- Disse bruges hovedsageligt til at udføre aritmetiske funktioner såsom subtraktion inden for digitale enheder, regnemaskiner osv.

- Disse subtraktorer er også egnede til forskellige mikrocontrollere til timere, pc (programtæller) og aritmetisk subtraktion

- Disse bruges til processorer til at beregne adresser, tabeller osv.

- Implementeringen af dette med logiske porte som NAND & NOR kan gøres med et hvilket som helst fuldt subtraktorlogisk kredsløb, fordi begge NOR & NAND-porte kaldes universelle porte.

Fra ovenstående information kan man ved at evaluere optælleren, fuld subtraktor ved hjælp af to halve subtraktorkredsløb og dens tabelformer bemærke, at Dout i fuldtrækkeren nøjagtigt svarer til Sout af fuldadder. Den eneste variation er, at A (inputvariabel) suppleres i fuldtrækkeren. Det er således muligt at ændre fuldadderkredsløbet til en fuldtrækker ved blot at supplere i / p A, før det gives til logiske porte for at generere den sidste lånebit-output (Bout).

Ved at bruge et hvilket som helst fuldt subtraktorlogisk kredsløb kan fuld subtraktor ved hjælp af NAND-porte og fuld subtraktor ved hjælp af nor-porte implementeres, da både NAND- og NOR-porte behandles som universale porte. Her er et spørgsmål til dig, hvad er forskellen mellem halv subtraktor og fuld subtraktor?