I kombinationskredsløbene bruges forskellige logiske porte til at designe encoder, multiplexer, dekoder & de-multiplexer. Disse kredsløb har nogle karakteristika, som output fra dette kredsløb afhænger hovedsageligt af de niveauer, der er til enhver tid på indgangsterminalerne. Dette kredsløb inkluderer ikke nogen hukommelse. Den tidligere tilstand af indgangen har ingen indflydelse på den aktuelle tilstand for dette kredsløb. Indgangene og udgangene fra et kombinationskredsløb er 'n' nr. af input & 'm' nr. af output. Nogle af kombinationskredsløbene er halv adder og fuld adder, subtraktor, encoder, dekoder, multiplexer og demultiplexer. Denne artikel diskuterer en oversigt over halv adder og full adder, og den arbejder med sandhedstabeller.

Hvad er en Adder?

En adder er en digitalt logik kredsløb i elektronik, der i vid udstrækning bruges til tilføjelse af numre. I mange computere og andre typer processorer bruges tilføjere endda til at beregne adresser og relaterede aktiviteter og beregne tabelindekser i ALU og endda bruges i andre dele af processorer. Disse kan bygges til mange numeriske repræsentationer som overskydende 3 eller binært kodet decimal. Tilføjere klassificeres grundlæggende i to typer: Half Adder og Full Adder.

Hvad er Half Adder og Full Adder Circuit?

Halvadderkredsløbet har to indgange: A og B, som tilføjer to indgangscifre og genererer en carry og en sum. Det fulde optagerkredsløb har tre indgange: A og C, som tilføjer tre indgangsnumre og genererer en bære- og sum. Denne artikel giver detaljerede oplysninger om, hvad der er formålet med en halvhugger og fuld adder i tabelform og endda i kredsløbsdiagrammer også. Det nævnes allerede, at det vigtigste og afgørende formål med tilføjere er tilføjelse. Nedenfor er de detaljerede halv adder og fuld adder teori.

Grundlæggende halvadder og fuldadder

Halvadder

Så når man kommer til scenariet med halv adderer, tilføjer det to binære cifre, hvor inputbitene betegnes som augend og addend, og resultatet bliver to output, den ene er summen og den anden er carry. For at udføre sumoperationen anvendes XOR på begge indgangene, og AND-gate anvendes på begge indgange for at producere bære.

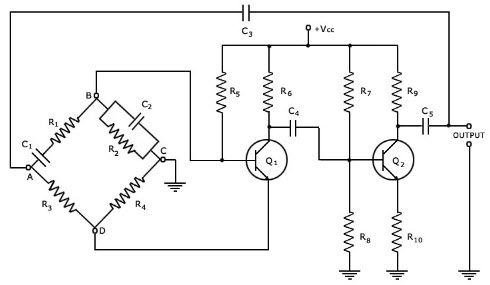

HA Funktionsdiagram

I det fulde adderkredsløb tilføjer det 3 one-bit-tal, hvor to af de tre bit kan betegnes som operander, og den anden betegnes som bit, der er indført. Det producerede output er 2-bit-output, og disse kan henvises til til som output bære og summe.

Ved at bruge en halv adderer kan du designe enkel tilføjelse ved hjælp af logiske porte.

Lad os se et eksempel på tilføjelse af to enkeltbit.

2-bit halvt adder sandhedstabel er som nedenfor:

Sandhedstabel med halv adder

0 + 0 = 0

0 + 1 = 1

1 + 0 = 1

1 + 1 = 10

Dette er de mindst mulige kombinationer med en enkelt bit. Men resultatet for 1 + 1 er 10, sumresultatet skal omskrives som en 2-bit output. Således kan ligningerne skrives som

0 + 0 = 00

0 + 1 = 01

1 + 0 = 01

1 + 1 = 10

Output '1'of' 10 'er gennemført. 'SUM' er den normale output, og 'CARRY' er gennemførelsen.

Nu er det blevet ryddet, at en 1-bit adder let kan implementeres ved hjælp af XOR Gate til output 'SUM' og en AND Gate til 'Carry'.

For eksempel, når vi har brug for at tilføje to 8-bit bytes sammen, så kan det implementeres ved hjælp af et fuldt-adder logisk kredsløb. Halvtælleren er nyttig, når du vil tilføje et binært ciffer.

En måde at udvikle to-binære cifre tilføjere på ville være at lave en sandhedstabel og reducere den. Når du vil oprette en tre-binær cifret adder, udføres den halve addertilføjelsesoperation to gange. På en lignende måde udføres operationen en gang til, når du beslutter dig for at lave en firecifret adder. Med denne teori var det klart, at implementeringen er enkel, men udvikling er en tidskrævende proces.

Det enkleste udtryk bruger den eksklusive ELLER-funktion:

Sum = A XOR B

Carry = A OG B

HA-logisk diagram

Og et ækvivalent udtryk med hensyn til grundlæggende AND, OR og NOT er:

SUM = A.B + A.B ’

VHDL-kode til halvadder

Enhed ha er

Port (a: i STD_LOGIC

b: i STD_LOGIC

sha: ude STD_LOGIC

cha: ud STD_LOGIC)

slutningen ha

Arkitektur Behavioral af ovenstående kredsløb er

begynde

sha<= a xor b

ingen<= a and b

slut Adfærdsmæssig

Halvadder IC-nummer

Implementeringen af halv adder kan ske via højhastigheds CMOS digitale logiske integrerede kredsløb som 74HCxx-serien, der inkluderer SN74HC08 (7408) & SN74HC86 (7486).

Halvadderbegrænsninger

Hovedårsagen til at kalde disse binære tilføjere som Half Adders er, at der ikke er noget område, der inkluderer bæretiden ved hjælp af en tidligere bit. Så dette er en hovedbegrænsning af HA'er, der engang blev brugt som binær adderer, især i realtidssituationer, der involverer tilføjelse af flere bits. Så denne begrænsning kan overvindes ved hjælp af de fulde tilføjere.

Fuld adder

Denne adder er vanskelig at implementere sammenlignet med half-adder.

Fuld adder funktionelt diagram

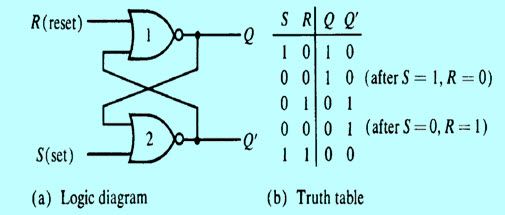

Forskellen mellem en halvadder og en fuldadder er, at fuldadderen har tre indgange og to udgange, mens halvadder kun har to indgange og to udgange. De første to indgange er A og B, og den tredje indgang er en indgangsbære som C-IN. Når en fuldadderlogik er designet, strenger du otte af dem sammen for at oprette en byte-bred adderer og kaskade bærebiten fra en adder til den næste.

FA sandhedstabel

Outputbæringen er betegnet som C-OUT, og den normale output er repræsenteret som S, som er 'SUM'.

Med ovenstående fuld adder sandhed-tabel kan implementeringen af et fuldt adder-kredsløb let forstås. SUM 'S' er produceret i to trin:

- Ved XORing af de leverede input 'A' og 'B'

- Resultatet af A XOR B XORes derefter med C-IN

Dette genererer SUM, og C-OUT er kun sandt, når begge to af tre indgange er HIGH, så vil C-OUT være HIGH. Så vi kan implementere et fuldt adder kredsløb ved hjælp af to halv adder kredsløb. Indledningsvis vil den halve adder bruges til at tilføje A og B for at producere en delvis sum, og en anden halvdel af adderlogikken kan bruges til at tilføje C-IN til den sum, der produceres af den første halv adder for at få den endelige S-output.

Hvis nogen af halvtællerlogikken frembringer en bære, vil der være en outputbære. Så C-OUT vil være en ELLER-funktion af Carry-udgange med halvtaddere. Se på implementeringen af det fulde adderkredsløb vist nedenfor.

Fuld Adder logisk diagram

Implementeringen af større logiske diagrammer er mulig med ovenstående fulde adderlogik, og et enklere symbol bruges mest til at repræsentere operationen. Nedenfor er en enklere skematisk gengivelse af en en-bit fuld adder.

Med denne type symbol kan vi tilføje to bits sammen, tage en bære fra den næste lavere størrelsesorden og sende en bære til den næste højere størrelsesorden. I en computer til en multi-bit operation skal hver bit repræsenteres af en fuld adder og skal tilføjes samtidigt. For at tilføje to 8-bit tal skal du således bruge 8 fulde tilføjere, som kan dannes ved at kaskade to af 4-bit-blokkene.

Halvadder og fuldadder ved hjælp af K-Map

Selv summen og bæreoutputene til halvtadderen kan også opnås med metoden til Karnaugh-kortet (K-map). Det halv adder og fuld adder boolsk udtryk kan fås via K-map. Så K-kortet for disse tilføjere diskuteres nedenfor.

Halvtælleren K-map er

HA K-Map

Den fulde adder K-Map er

FA K-Map

Logisk udtryk for SUM og Carry

Det logiske udtryk for sum (S) kan bestemmes ud fra de input, der er nævnt i tabellen.

= A'B'Cin + A 'B CCin' + A B'Cin '+ AB Cin

= Cin (A'B '+ AB) + Cin' (A'B + A B ')

= Cin EX-OR (A EX-OR B)

= (1,2,4,7)

Det logiske udtryk for bæringen (Cout) kan bestemmes ud fra de input, der er nævnt i tabellen.

= A’B Cin + AB’Cin + AB Cin ’+ ABCin

= AB + BCin + ACin

= (3, 5, 6, 7)

Med de ovennævnte sandhedstabeller kan resultaterne opnås, og proceduren er:

Et kombineret kredsløb kombinerer de forskellige porte i kredsløbet, hvor de kan være en indkoder, dekoder, multiplexer og demultiplexer . Kombinationskredsløbets karakteristika er som følger.

- Outputtet på ethvert tidspunkt er kun baseret på de niveauer, der findes på indgangsterminalerne.

- Det bruger ikke nogen hukommelse. Den tidligere indgangstilstand har ingen effekt på kredsløbets nuværende tilstand.

- Det kan have et vilkårligt antal indgange og m antal udgange.

VHDL-kodning

VHDL-kodning til fuld adder inkluderer følgende.

enhed fuld_add er

Port (a: i STD_LOGIC

b: i STD_LOGIC

cin: i STD_LOGIC

sum: ud STD_LOGIC

cout: ud STD_LOGIC)

slut fuldt

Arkitektur Behavioral af full_add er

komponent ha er

Port (a: i STD_LOGIC

b: i STD_LOGIC

sha: ude STD_LOGIC

cha: ud STD_LOGIC)

slutkomponent

signal s_s, c1, c2: STD_LOGIC

begynde

HA1: ha havnekort (a, b, s_s, c1)

HA2: ha port kort (s_s, cin, sum, c2)

koste<=c1 or c2

slut Adfærdsmæssig

Det forskel mellem halvhugger og fuldhugger er, at halv adder producerer resultater, og fuld adder bruger halv adder til at producere et andet resultat. Tilsvarende, mens Full-Adder er af to Half-Adders, er Full-Adder den egentlige blok, som vi bruger til at oprette de aritmetiske kredsløb.

Carry Lookahead Adders

I begrebet krusningsbærende adderkredsløb er de bits, der er nødvendige for tilsætning, straks tilgængelige. Der henviser til, at hver addersektion skal holde sin tid til ankomsten af transport fra den forrige adderblok. På grund af dette tager det mere tid at producere SUM og CARRY, da hver sektion i kredsløbet venter på ankomst af input.

For at levere output til den nte blok skal den f.eks. Modtage input fra (n-1) th-blokken. Og denne forsinkelse betegnes tilsvarende som udbredelsesforsinkelse.

For at overvinde forsinkelsen i krusninger bærer huggorm, blev en bære-lookahead huggorm introduceret. Her kan udbredelsesforsinkelsen minimeres ved hjælp af kompliceret hardware. Nedenstående diagram viser en bærer-lookahead-addder ved hjælp af fulde tilføjere.

Bær lookahead ved hjælp af fuld adder

Sandhedstabellen og de tilsvarende outputligninger er

| TIL | B | C | C + 1 | Tilstand |

| 0 | 0 | 0 | 0 | Ingen bærer Frembringe |

| 0 | 0 | 1 | 0 | |

| 0 | 1 | 0 | 0 | |

| 0 | 1 | 1 | 1 | Ingen bærer Formere sig |

| 1 | 0 | 0 | 0 | |

| 1 | 0 | 1 | 1 | |

| 1 | 1 | 0 | 1 | Bære Frembringe |

| 1 | 1 | 1 | 1 |

Bæreformateringsligningen er Pi = Ai XOR Bi, og bæregenereringen er Gi = Ai * Bi. Med disse ligninger kan sum- og bære ligningerne repræsenteres som

SUM = Pi XOR Ci

Ci + 1 = Gi + Pi * Ci

Gi leverer kun carry, når begge input Ai og Bi er 1 uden at overveje input-carry. Pi er relateret til bærespredning fra Ci til Ci + 1.

Forskel mellem Half Adder og Full Adder

Det forskellen mellem halvtæller- og fuldtællertabellen er vist nedenfor.

| Halvadder | Fuld adder |

| Half Adder (HA) er et kombinationslogisk kredsløb, og dette kredsløb bruges til at tilføje to en-bit cifre. | Full Adder (FA) er et kombinations kredsløb, og dette kredsløb bruges til at tilføje tre en-bit cifre. |

| Når HA er genereret fra den tidligere tilføjelse i HA, kan den ikke tilføjes til næste trin i HA. | I FA, når bæringen er genereret fra den tidligere tilføjelse, kan den føjes til det næste trin. |

| Halvadder indeholder to logiske porte som AND gate og EX-OR gate. | Fuld adder indeholder to EX-OR-porte, to OR-porte og to AND-porte. |

| Indgangsbitene i halvtælleren er to som A, B. | Inputbitene i den fulde adder er tre som A, B & C-in |

| Halv optællingssum og bære ligning er S = a⊕b C = a * b | Fuld adder logik udtryk er S = a ⊕ b⊕Cin Cout = (a * b) + (Cin * (a⊕b)). |

| HA bruges i computere, regnemaskiner, enheder, der bruges til digital måling osv. | FA bruges i digitale processorer, multiple bit tilføjelse osv. |

Det nøgleforskelle mellem halvmåler og fuldmåler diskuteres nedenfor.

- Halvadder genererer sum & carry ved at tilføje to binære input, mens den fulde addder bruges til at generere sum & carry ved at tilføje tre binære input. Både halvadder- og fuldadderhardwarearkitekturen er ikke den samme.

- Det vigtigste træk, der adskiller HA & FA, er, at der i HA ikke er nogen sådan aftale at betragte den sidste tilføjelse ligesom dens input. Men en FA finder en bestemt indgangssøjle som Cin for at overveje den sidste tilføjelses bærebit.

- De to tilføjere viser en forskel baseret på de komponenter, der bruges i kredsløbet til dets konstruktion. Halvtilsætningerne (HA'er) er designet med kombinationen af to logiske porte som AND & EX-OR, mens FA er designet med kombinationen af tre AND-, to XOR- og en ELLER-porte.

- Dybest set fungerer HA'er på 2-to indgange på 1-bit, mens FA'er opererer på tre indgange på 1-bit. Halvadder bruges i forskellige elektroniske enheder til evaluering af tilføjelsen, mens den fulde adder bruges i digitale processorer til tilføjelse af en lang bit.

- Lighederne i disse to tilføjere er, at begge HA & FA er kombinerede digitale kredsløb, så de bruger ikke noget hukommelseselement såsom sekventielle kredsløb. Disse kredsløb er vigtige for aritmetisk drift for at tilføje tilføjelsen af det binære tal.

Fuld Adder Implementering ved hjælp af Half Adders

Implementeringen af en FA kan ske gennem to halve tilføjere, der er logisk forbundet. Blokdiagrammet over dette kan vises nedenfor, som fortæller forbindelsen af en FA ved hjælp af to halvaddere.

Summen og bære ligningerne fra tidligere beregninger er

S = A 'B' Cin + A 'BC' i + ABCin

Cout = AB + ACin + BCin

Sumligningen kan skrives som.

Cin (A'B '+ AB) + C' in (A‘B + A B ')

Så Sum = Cin EX-OR (A EX-OR B)

Cin (A EX-OR B) + C’in (A EX-OR B)

= Cin EX-OR (A EX-OR B)

Cout kan skrives som følger.

COUT = AB + ACin + BCin.

Cout = AB + + skuffelser BCin (A + A)

= ABCin + AB + ACin + A ’B Cin

= AB (1 + Cin) + ACin + A ’B Cin

= A B + ACin + A ’B Cin

= AB + ACin (B + B ') + A ’B Cin

= ABCin + AB + A’B Cin + A ’B Cin

= AB (Cin + 1) + A B Cin + A ’B Cin

= AB + AB ’Cin + A’ B Cin

= AB + Cin (AB ’+ A’B)

Derfor er COUT = AB + Cin (A EX-OR B)

Afhængigt af ovenstående to summer og bære ligninger kan FA kredsløbet implementeres ved hjælp af to HA'er og en ELLER gate. Kredsløbsdiagrammet for en fuldhugger med to halvtilføjere er illustreret ovenfor.

Fuld adder ved hjælp af to halvaddere

Fuld Adder Design med NAND Gates

En NAND-port er en slags universalport, der bruges til at udføre enhver form for logisk design. FA-kredsløbet med NAND-portdiagrammet er vist nedenfor.

FA ved hjælp af NAND Gates

FA er en let en-bit addder, og hvis vi ønsker at udføre tilføjelsen af n-bit, så n nej. af en-bit FA'er skal anvendes i kaskadeforbindelsesformatet.

Fordele

Det fordelene ved halv adder og fuld adder inkluderer følgende.

- Det vigtigste formål med en halv adder er at tilføje to single-bit tal

- Fuld tilføjere har muligheden for at tilføje en bærebit, som er resultatet af den tidligere tilføjelse

- Med fuld adder kan vigtige kredsløb som adder, multiplexer og mange andre implementeres

- De fulde adderkredsløb forbruger minimal strøm

- Fordelene ved en fuld adder over en halv adder er, at en full adder bruges til at overvinde ulempen ved en halv adder, fordi halv adder hovedsageligt bruges til at tilføje to 1-bit tal. Halve tilføjere tilføjer ikke bærebiten, så for at overvinde denne fulde adder anvendes. I fuld adder kan tilføjelsen af tre bits udføres og genererer to udgange.

- Design af tilføjere er enkel, og det er en grundlæggende byggesten, så en-bit tilføjelse let kan forstås.

- Denne optæller kan konverteres til halv subtraktor ved at tilføje en inverter.

- Ved at bruge en fuld adder kan man opnå høj output.

- Høj hastighed

- Meget stærk skaleringsforsyning

Ulemper

Det ulemperne ved halv adder og fuld adder inkluderer følgende.

- Derudover kan halvt adder ikke bruges, før det bæres, så det er ikke relevant til kaskadering af tilføjelsen af multi-bit.

- For at overvinde denne ulempe er FA nødvendigt at tilføje tre 1 bit.

- Når FA er brugt i form af en kæde som en RA (Ripple Adder), kan drevkapaciteten for output reduceres.

Ansøgninger

Anvendelserne af halv adder og fuld adder inkluderer følgende.

- Tilføjelsen af binære bits kan udføres ved halv adder ved hjælp af ALU i computeren, fordi den bruger adder.

- Halvadderkombination kan bruges til at designe et fuldt adderkredsløb.

- Halve tilføjere bruges i regnemaskinerne og til at måle adresser såvel som tabeller

- Disse kredsløb bruges til at håndtere forskellige applikationer inden for digitale kredsløb. I fremtiden spiller det en nøglerolle inden for digital elektronik.

- Et FA-kredsløb bruges som et element i mange store kredsløb såsom Ripple Carry Adder. Denne adder tilføjer antallet af bits samtidigt.

- FA'er bruges i aritmetisk logisk enhed (ALU)

- FA'er bruges i grafikrelaterede applikationer som GPU (Graphics Processing Unit)

- Disse bruges i multiplikationskredsløbet til at udføre Carryout Multiplication.

- På en computer til at generere hukommelsesadressen og til at opbygge programmets kontrapunkt mod efterfølgende instruktion bruges den aritmetiske logiske enhed ved hjælp af komplette tilføjere.

Således, når tilføjelsen af to binære tal er udført, tilføjes cifrene først de mindste bit. Denne proces kan udføres gennem en halv adder, fordi den enkleste n / w der tillader tilføjelse af to 1-bit tal. Indgangene til denne optager er de binære cifre, mens udgangene er summen (S) og bæringen (C).

Hver gang antallet af cifre er inkluderet, bruges HA-netværket simpelthen til at forbinde de mindst cifre, da HA ikke kan tilføje bære nummer fra den tidligere klasse. En fuld adder kan defineres som basen for alle digitale aritmetiske enheder. Dette bruges til at tilføje tre 1-cifrede tal. Denne adder indeholder tre input som A, B og Cin, mens output er Sum og Cout.

Relaterede begreber

Det begreber relateret til halv adder og fuld adder bare ikke hold dig til et eneste formål. De har omfattende brug i mange applikationer, og et par af de relaterede er nævnt:

- Halvadder og fuldadder IC-nummer

- Udvikling af 8-bit adder

- Hvad er de halve adderforholdsregler?

- JAVA-applet af en krusningsbærer

Derfor handler det kun om halv adder og fuld adder teori sammen med sandhedstabellerne og logiske diagrammer vises også designet af fuld adder ved hjælp af halvt adder kredsløb. Mange af de halv adder og fuld adder pdf dokumenter er tilgængelige for at give avanceret information om disse begreber. Det er desuden vigtigt at vide hvordan en 4-bit fuld adder implementeres ?