I denne verden ønsker alle at få deres ting/værker gjort hurtigt. er det ikke? Fra biler til industri- til husholdningsmaskiner ønsker alle, at de skal arbejde hurtigere. Ved du, hvad der sidder inde i disse maskiner, der får dem til at fungere? De er processorer . De kan være mikro- eller makroprocessorer afhængigt af funktionaliteten. Den grundlæggende processor udfører generelt én instruktioner pr. clock-cyklus. I måde at forbedre deres forarbejdningshastighed, så maskinerne kan forbedre deres hastighed opstod, er den superskalar processor som har pipelining-algoritme, der gør det muligt at udføre to instruktioner pr. clock-cyklus. Den blev først opfundet af Seymour Crays CDC 6600 opfundet i 1964 og blev senere forbedret af Tjaden & Flynn i 1970.

Den første kommercielle single-chip superscalar mikroprocessor MC88100 blev udviklet af Motorola i 1988, senere introducerede Intel sin version I960CA i 1989 og AMD 29000-serien 29050 i 1990. I øjeblikket er den typiske superscalar processor, der bruges, Intel Core i7-processoren Nehalem mikroarkitekturen.

Selvom implementeringerne af superskalar er på vej mod at øge kompleksiteten. Designet af disse processorer refererer normalt til et sæt metoder, der tillader CPU'en på en computer at opnå en gennemstrømning på over en instruktion for hver cyklus, mens den udfører et enkelt sekventielt program. Lad os yderligere se i denne artikel SuperScalarprocessor-arkitekturen, som reducerer dens udførelsestid og dens applikationer.

Hvad er Superscalar Processor?

En type mikroprocessor, der bruges til at implementere en type parallelisme kendt som instruktionsniveau-parallelisme i en enkelt processor for at udføre mere end én instruktion under en CLK-cyklus ved samtidig at sende forskellige instruktioner til specielle udførelsesenheder på processoren. EN skalar processor udfører en enkelt instruktion for hver clock-cyklus; en superskalær processor kan udføre mere end én instruktion i løbet af en clock-cyklus.

Superscalars designteknikker omfatter normalt omdøbning af parallelregister, parallelinstruktionsdekodning, udførelse af uorden og spekulativ udførelse. Så disse metoder bruges normalt med komplementerende designmetoder som pipelining, brancheforudsigelse, caching og multi-core inden for nuværende design af mikroprocessorer.

Funktioner

Funktionerne ved superskalære processorer omfatter følgende.

- Superscalar arkitektur er en parallel computerteknik, der bruges i forskellige processorer.

- I en superskalar computer administrerer CPU'en flere instruktionspipelines for at udføre adskillige instruktioner samtidigt i løbet af en urcyklus.

- Superskalære arkitekturer omfatter alle pipelining funktioner, selvom der er flere instruktioner, der udføres samtidigt inden for samme pipeline.

- Superskalære designmetoder omfatter normalt parallel register omdøbning, parallel instruktionsdekodning, spekulativ eksekvering og udelukket udførelse. Så disse metoder bruges normalt sammen med komplementerende designmetoder som caching, pipelining, grenforudsigelse og multi-core i nyere mikroprocessordesign.

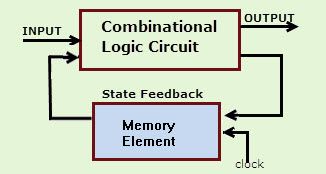

Superskalar processorarkitektur

Vi ved, at en superskalær processor er en CPU, der udfører over én instruktion for hver CLK-cyklus, fordi behandlingshastigheder simpelthen måles i CLK-cyklusser for hvert sekund. Sammenlignet med en skalær processor er denne processor meget hurtigere.

Superscalar processorarkitektur omfatter hovedsageligt parallelle eksekveringsenheder, hvor disse enheder kan implementere instruktioner samtidigt. Så først blev denne parallelle arkitektur implementeret i en RISC-processor, der bruger enkle og korte instruktioner til at udføre beregninger. Så på grund af deres superskalære evner, normalt RISIKO processorer har klaret sig bedre sammenlignet med CISC-processorer, der kører på samme megahertz. Men de fleste CISC processorer som nu Intel Pentium omfatter også en vis RISC-arkitektur, som giver dem mulighed for at udføre instruktioner parallelt.

Den superskalære processor er udstyret med flere behandlingsenheder til at håndtere forskellige instruktioner parallelt i hvert behandlingstrin. Ved at bruge ovenstående arkitektur starter en række instruktioner udførelse inden for en lignende clock-cyklus. Disse processorer er i stand til at opnå et instruktionsudførelsesoutput af den ovennævnte ene instruktion for hver cyklus.

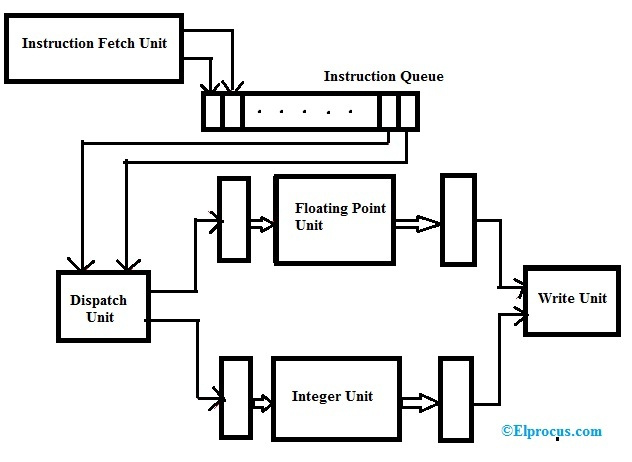

I ovenstående arkitekturdiagram bruges en processor med to eksekveringsenheder, hvor den ene bruges til heltal, og den anden bruges til operationerne med flydende komma. Instruktionshentningsenheden (IFU) er i stand til at læse instruktioner ad gangen og gemmer dem i instruktionskøen. I hver cyklus henter og afkoder afsendelsesenheden op til 2 instruktioner fra køfronten. Hvis der er et enkelt heltal, enkelt flydende komma-instruktion og ingen farer, afsendes begge instruktioner inden for en lignende clock-cyklus.

Rørføring

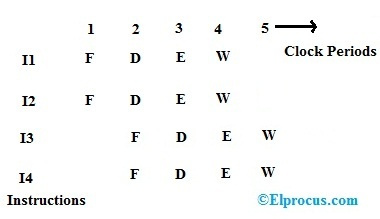

Pipelining er proceduren til at opdele opgaver i undertrin og udføre dem inden for forskellige processordele. I den følgende superskalære pipeline kan to instruktioner hentes og afsendes ad gangen for at fuldføre maksimalt 2 instruktioner pr. cyklus. Pipelining-arkitekturen i den skalære processor og den superskalære processor er vist nedenfor.

Instruktionerne i en superskalarprocessor udsendes fra en sekventiel instruktionsstrøm. Den skal tillade flere instruktioner for hver clock-cyklus, og CPU'en skal kontrollere dynamisk for dataafhængigheder mellem instruktionerne.

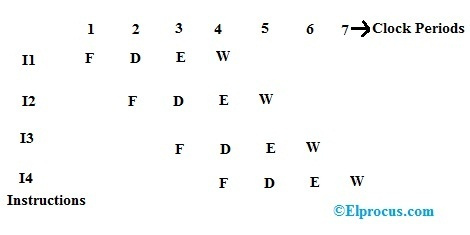

I nedenstående pipeline-arkitektur hentes F, D afkodes, E udføres, og W er registernedskrivning. I denne pipeline-arkitektur er I1, I2, I3 & I4 instruktioner.

Den skalære processorpipeline-arkitektur inkluderer en enkelt pipeline og fire stadier hentning, afkodning, eksekvering og resultatskrivning. I den enkelt pipeline skalarprocessor fungerer pipelinen i instruktion1 (I1) som; i den første clock-periode I1 vil den hente, i den anden clock-periode vil den afkode og i den anden instruktion vil I2 hente. Den tredje instruktion I3 i den tredje clockperiode henter, I2 vil afkode og I1 udføres. I den fjerde clockperiode vil I4 hente, I3 vil afkode, I2 udføre og I1 skrive i hukommelsen. Så i syv klokkeperioder vil den udføre 4 instruktioner i en enkelt pipeline.

Den superskalære processorpipeline-arkitektur inkluderer to pipelines og fire stadier hentning, afkodning, eksekvering og resultatskrivning. Det er en 2-udgave superskalarprocessor, hvilket betyder, at to instruktioner ad gangen vil hente, afkode, udføre og skrive tilbage til resultatet. De to instruktioner I1 & I2 vil ad gangen hente, afkode, udføre og skrive tilbage i hver klokkeperiode. Samtidig i den næste clockperiode vil de resterende to instruktioner I3 & I4 ad gangen hente, afkode, udføre og skrive tilbage. Så i fem urperioder vil den udføre 4 instruktioner i en enkelt pipeline.

En skalarprocessor udsender således en enkelt instruktion pr. clock-cyklus og udfører et enkelt pipeline-trin pr. clock-cyklus, hvorimod en superscalar-processor udsteder to instruktioner pr. clock-cyklus, og den udfører to instanser af hvert trin parallelt. Så instruktionsudførelsen i en skalarprocessor tager mere tid, mens det i en superskalar tager mindre tid at udføre instruktioner .

Typer af superskalar-processorer

Disse er forskellige typer superskalære processorer, der er tilgængelige på markedet, som diskuteres nedenfor.

Intel Core i7 processor

Intel core i7 er en superskalar-processor, der er baseret på Nehalem-mikroarkitekturen. I et Core i7-design er der forskellige processorkerner, hvor hver processorkerne er en superskalær processor. Dette er den hurtigste version af Intel-processoren, der bruges i forbrugercomputere og -enheder. I lighed med Intel Corei5 er denne processor indlejret i Intel Turbo Boost-teknologi. Denne processor er tilgængelig i 2 til 6 varianter, som understøtter op til 12 forskellige tråde på én gang.

Intel Pentium processor

Intel Pentium-processorens superskalære pipelinede arkitektur betyder, at CPU'en udfører minimum to eller flere instruktioner for hver cyklus. Denne processor er meget udbredt i personlige computere. Intel Pentium-processorenheder er normalt bygget til onlinebrug, cloud computing og samarbejde. Så denne processor fungerer perfekt til tablets og Chromebooks for at give stærk lokal ydeevne og effektive online-interaktioner.

IBM Power PC601

Den superskalære processor som IBM power PC601 er fra familien af PowerPC af RISC-mikroprocessorer. Denne processor er i stand til at udstede såvel som tilbagekalde tre instruktioner for hvert ur og en for hver af de 3 eksekveringsenheder. Instruktionerne er totalt ude af funktion for forbedret ydeevne; men PC601 vil få udførelsen til at komme i orden.

Power PC601-processoren giver 32-bit logiske adresser, 8, 16 og 32 bit heltal datatyper og 32 og 64 bit flydende-komma datatyper. Til implementering af 64-bit PowerPC giver denne processors arkitektur 64-bit-baserede heltaldatatyper, adressering og andre funktioner, der er nødvendige for at fuldende den 64-bit-baserede arkitektur.

MC 88110

MC 88110 er en andengenerations RISC-mikroprocessor med enkelt chip, der bruger avancerede metoder til at udnytte parallelitet på instruktionsniveau. Denne processor bruger flere on-chip caches, superskalære instruktionsproblemer, optagelse af begrænset dynamisk instruktion og spekulativ udførelse for at opnå maksimal ydeevne, så den er ideelt brugt som en central processor inden for billige pc'er og arbejdsstationer.

Intel i960

Intel i960 er en superskalær processor, som er i stand til at udføre og sende forskellige uafhængige instruktioner under hver processorurcyklus. Dette er en RISC-baseret mikroprocessor, der blev meget berømt som en indlejret mikrocontroller i begyndelsen af 1990'erne. Denne processor bruges kontinuerligt i nogle få militære applikationer.

MIPS R

MIPS R er en dynamisk og superskalær mikroprocessor, der bruges til at udføre 64-bit MIPS 4-instruktionssætarkitekturen. Denne processor henter og afkoder 4 instruktioner for hver cyklus og sender dem til fem fuldstændigt pipelinede og lav-latency eksekveringsenheder. Denne processor er specielt designet til højtydende, store og virkelige applikationer med dårlig hukommelse. Med omtrentlig udførelse beregner den blot hukommelsesadresser. MIPS-processorer bruges hovedsageligt i forskellige enheder som Nintendo Gamecube, SGIs produktlinje, Sony Playstation 2, PSP & Cisco-routere.

Forskel S/H Superscalar vs Pipelining

Forskellen mellem superskalar og pipelining diskuteres nedenfor.

|

Superskalar |

Rørføring |

| En superskalar er en CPU, der bruges til at implementere en form for parallelisme, som kaldes instruktionsniveau parallelisme i en enkelt processor. | En implementeringsteknik som pipelining bruges, hvor flere instruktioner overlappes i udførelsen. |

| En superskalær arkitektur starter flere instruktioner samtidigt og udfører dem separat. | Pipelining-arkitektur udfører kun et enkelt pipeline-trin for hver clock-cyklus.

|

| Disse processorer er afhængige af rumlig parallelitet. | Det afhænger af tidsmæssig parallelitet. |

| Flere operationer kører samtidigt på separat hardware. | Overlapper flere operationer på almindelig hardware. |

| Det opnås ved at duplikere hardwareressourcer som registerfilporte og eksekveringsenheder. | Det opnås ved at udføre enheder, der er pipelinet dybere med meget hurtige CLK-cyklusser. |

Egenskaber

Det superscalar processor egenskaber omfatte følgende.

- En superskalar processor er en super-pipelinet model, hvor de uafhængige instruktioner simpelthen udføres serielt uden nogen ventesituation.

- En superskalær processor henter og afkoder ad gangen adskillige instruktioner fra den indkommende instruktionsstrøm.

- Arkitekturen af superskalære processorer udnytter potentialet for parallelisme på instruktionsniveau.

- Superscalar-processorer udsteder hovedsageligt ovenstående enkeltinstruktion for hver cyklus.

- Nr. af udstedte instruktioner afhænger hovedsageligt af instruktionerne i instruktionsstrømmen.

- Instruktioner omorganiseres ofte, så de passer bedre til processorens arkitektur.

- Den superskalære metode er normalt forbundet med nogle identificerende karakteristika. Instruktioner udsendes normalt fra en sekventiel instruktionsstrøm.

- CPU'en kontrollerer dynamisk for dataafhængigheder mellem instruktionerne under kørsel.

- CPU'en udfører flere instruktioner for hver clock-cyklus.

Fordele og ulemper

Det fordelene ved den superskalære processor omfatte følgende.

- En superskalær processor implementerer parallelitet på instruktionsniveau i en enkelt processor.

- Disse processorer er simpelthen lavet til at udføre ethvert instruktionssæt.

- Den superskalære processor inklusive forudsigelse af eksekveringsgrene i uorden og spekulativ eksekvering kan simpelthen finde parallelitet over flere grundlæggende blokke og loop-iterationer.

Det ulemper ved den superskalære processor omfatte følgende.

- Superscalar-processorer bruges ikke meget i små indlejrede systemer på grund af strømforbrug.

- Problemet med planlægning kan ske i denne arkitektur.

- Superscalar processor øger kompleksitetsniveauet i design af hardware.

- Instruktionerne i denne processor hentes simpelthen baseret på deres sekventielle programrækkefølge, men dette er ikke den bedste udførelsesrækkefølge.

Superskalar processorapplikationer

Anvendelserne af en superskalar processor omfatter følgende.

- Den superskalære udførelse bruges ofte af en bærbar eller stationær computer. Denne processor scanner simpelthen det program, der udføres, for at opdage sæt instruktioner, der kan udføres som én.

- En superskalær processor inkluderer forskellige datastihardwarekopier, som udfører forskellige instruktioner på én gang.

- Denne processor er hovedsageligt designet til at generere en implementeringshastighed på over én instruktion for hver clock-cyklus for et enkelt sekventielt program.

Det handler altså om en oversigt over den superskalære processor – arkitektur, typer og applikationer. Her er et spørgsmål til dig, hvad er den skalære processor?