RISC V er en instruktionssætarkitektur udviklet af University of California, Berkeley. Begrebet RISC var motiveret af sandheden om, at de fleste af processorinstruktionerne ikke blev brugt af de fleste computerprogrammer. Så unødvendig afkodningslogik blev brugt inden for design af processorer , der bruger mere strøm såvel som areal. For at forkorte instruktionssættet og investere mere i registerressourcer, RISC V processor blev gennemført.

Denne teknologi blev bemærket af mange teknologigiganter og nystartede virksomheder, fordi den er fuldstændig open source og gratis. De fleste typer processorer er tilgængelige med en licensaftale, dog med denne type processor; alle kan lave deres nye processordesign. Så denne artikel diskuterer en oversigt over en RISC V-processor – funktion og dens applikationer.

Hvad er RISC V-processor?

I RISC V-processoren står udtrykket RISC for 'reduceret instruktionssæt computer', som udfører få computerinstruktioner, mens 'V' står for 5. generation. Det er en open source hardware ISA (instruction set architecture) baseret på det etablerede princip om RISIKO .

Sammenlignet med andre ISA-designs er denne ISA tilgængelig med en open source-licens. Så en række produktionsvirksomheder har annonceret og også leveret RISC-V-hardware med open source-operativsystemer.

Dette er en ny arkitektur og er tilgængelig i åbne, ikke-begrænsende og gratis licenser. Denne processor har omfattende support fra chip- og enhedsproducenter. Så den er hovedsageligt designet til at være frit udvidelig og tilpasselig til brug i mange applikationer.

RISC V historie

RISC blev opfundet af prof. David Patterson omkring 1980 ved University of California, Berkeley. Prof. David og Prof. John Hennessy indsendte deres indsats i to bøger, nemlig 'Computer Organization and Design' & 'Computer Architecture at Stanford University. Så de modtog ACM A.M. Turing-prisen i 2017.

Fra år 1980 til 2010 år blev RISCs femte generations udviklingsforskning startet og blev endelig identificeret som RISC-V, der udtales som risiko fem.

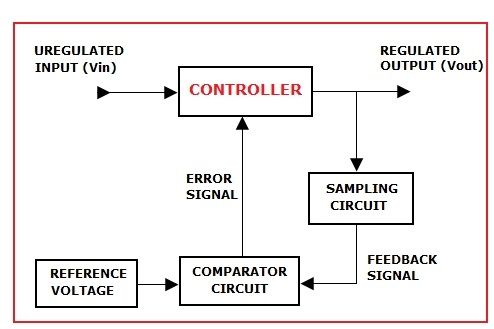

RISC V Architecture & Working

RV12 RISC V-arkitekturen er vist nedenfor. RV12 er meget konfigurerbar med en single-core RV32I og RV64I kompatibel RISC CPU, som bruges i indlejrede felter. RV12 er også fra en 32- eller 64-bit CPU-familie afhængigt af det industrielle standard RISC-V-instruktionssæt.

RV12 udfører simpelthen en Harvard-arkitektur for samtidig adgang til instruktion samt datahukommelse. Det inkluderer også en 6-trins pipeline, som hjælper med at optimere overlapninger mellem udførelsen samt hukommelsesadgange for at forbedre effektiviteten. Denne arkitektur inkluderer hovedsageligt Branch Prediction, Data Cache, Debug Unit, Instruction Cache og valgfri multiplikator- eller divider-enheder.

De vigtigste funktioner i RV12 RISC V omfatter følgende.

- Det er et industristandard instruktionssæt.

- Parametriseret med 32 eller 64 bit data.

- Den har præcise og hurtige afbrydelser.

- Brugerdefinerede instruktioner tillader tilføjelse af proprietære hardwareacceleratorer.

- Udførelse af enkelt cyklus.

- Seks-trins rørledning med optimering foldet.

- Support med hukommelsesbeskyttelse.

- Valgfri eller parametriserede caches.

- Ekstremt parametriseret.

- Brugere kan vælge 32/64-bit data & Branch Prediction Unit.

- Brugere kan vælge instruktions-/datacache.

- Brugervalgbar struktur, størrelse og arkitektur af cache.

- Hardware Divider eller Multiplikator Understøttelse af brugerdefineret latens.

- Busarkitekturen er fleksibel, hvilket understøtter Wishbone & AHB.

- Dette design optimerer kraften og størrelsen.

- Designet er fuldstændigt parametriseret, hvilket giver ydeevne eller kraftafvejninger.

- Gated CLK-design for at reducere kraften.

- Softwaresupport efter industristandard.

- Arkitektonisk simulator.

- Eclipse IDE bruges til Linux/Windows.

RISC V-udførelsesrørledningen

Det inkluderer fem trin som IF (instruktionshentning), ID (instruktionsafkodning), EX (execute), MEM (hukommelsesadgang) & WB (register-tilbageskrivning).

Hent instruktion

I Instruction Fetch- eller IF-stadiet læses en enkelt instruktion fra programtælleren (PC) og instruktionshukommelsen, som opdateres til den næste instruktion.

Instruktion Pre-Decode

Når RVC-understøttelse er tilladt, vil instruktionspræ-afkodningsfasen afkode en 16-bit-komprimeret instruktion til en indbygget 32-bit-instruktion.

Instruktion afkode

I Instruction Decode (ID)-stadiet er registerfilen tilladt, og bypass-kontrollerne bestemmes.

Udfør

I Udfør-stadiet beregnes resultatet for en ALU-, DIV-, MUL-instruktion, hukommelsen tilladt for en Store- eller Load-instruktion, og grene og spring måles i forhold til deres forventede resultater.

Hukommelse

I dette hukommelsestrin er der adgang til hukommelsen gennem pipelinen. Medtagelsen af denne fase sikrer rørledningens høje ydeevne.

Skrive tilbage

I dette trin skrives resultatet af udførelsesfasen ind i registerfilen.

Branch Predictor

Denne processor inkluderer en gren forudsigelsesenhed eller BPU, der bruges til at lagre tidligere data for at guide RISC V processoren til at beslutte, om en specifik gren er taget eller ej. Disse forudsigelsesdata opdateres simpelthen, når grenen udføres.

Denne enhed indeholder forskellige parametre, som bestemmer dens opførsel. For eksempel bruges HAS_BPU til at bestemme, om en gren forudsiger, at en enhed er til stede, BPU_GLOBAL_BITS vil bestemme, hvor mange tidligere bits, der skal bruges, og BPU_LOCAL_BITS vil bestemme, hvor mange af programtællerens LSB'er, der skal bruges. Kombinationen af BPU_LOCAL_BITS & BPU_GLOBAL_BITS vil skabe en vektor, der hovedsageligt bruges til at adressere gren-forudsigelsestabellen.

Data cache

Dette bruges hovedsageligt til at fremskynde adgangen til datahukommelse ved at buffere nyligt tilgåede hukommelsesplaceringer. Dette er i stand til at håndtere halvords-, byte- og ordadgange, når XLEN = 32, hvis de er på deres egne grænser. Den er også i stand til at håndtere halvords-, byte-, ord- og dobbeltordsadgange, når XLEN=64, hvis de er på deres egne grænser.

Igennem en cache-miss kan en hel blok skrives tilbage til hukommelsen, så om nødvendigt kan en ny blok indlæses i cachen. Datacachen deaktiveres ved at sætte DCACHE_SIZE til nul. Derefter tilgås hukommelsesplaceringer direkte gennem Datagrænseflade .

Instruktions cache

Dette bruges hovedsageligt til at fremskynde hentning af instruktioner ved at buffere nyligt hentede instruktioner. Denne cache bruges til at hente en pakke for hver cyklus på enhver 16-bit grænse, men ikke på tværs af en blokgrænse. Gennem en cache-miss kan en hel blok indlæses fra instruktionshukommelsen. Konfigurationen af denne cache kan udføres baseret på brugerens behov. Størrelsen af cachen, erstatningsalgoritmen og bloklængden kan konfigureres.

Instruktionscyklussen vil blive deaktiveret ved at sætte ICACHE_SIZE til nul. Derefter hentes pakker direkte fra hukommelsen gennem Instruktionsgrænseflade.

Debug enhed

Debug-enheden vil tillade fejlretningsomgivelserne at stoppe og undersøge CPU'en. De vigtigste funktioner i dette er Branch Tracing, Single Step Tracing op til 8- Hardware Breakpoints.

Registrer fil

Dette er designet med 32 registerplaceringer fra X0 til X31, hvor X9 Register altid er nul. Registerfilen inkluderer 1-skriveporte og 2-læseporte.

Konfigurerbar grænseflade

Dette er en ekstern grænseflade, hvor denne processor understøtter forskellige eksterne busgrænseflader.

Hvordan virker RISC V?

RISC-V er en instruktionssæt-arkitektur, der er forankret i RISC-principperne (reduced instruction set computer). Denne processor er meget unik og også revolutionerende, da den er en gratis, almindelig og open source ISA, hvor hardware kan udvikles, softwaren kan porteres og processorer kan designes til at understøtte det.

Forskel S/H RISC V Vs MIPS

Forskellen mellem RISC V og MIPS inkluderer følgende.

|

RISC V |

MIPS |

| Udtrykket RISC V står for Reduced Instruction Set Computer, hvor 'V' er den femte generation. | Udtrykket 'MIPS' står for 'Million instruktioner pr. sekund'. |

| RISC-V tillader simpelthen producenter af mindre enheder at designe hardware uden at betale. | MIPS giver producenten mulighed for at måle processorens hastighed ved at betale, fordi det ikke er gratis. |

| MIPS er effektivt dødt. | RISC-V er ikke effektivt dødt. |

| Denne processor giver greninstruktioner til sammenligning af to registre. | MIPS afhænger af en sammenligningsinstruktion, der lokaliserer et register til 1 eller 0 baseret på, om kontrasten er sand. |

| ISA-kodningsskemaet er fast og variabelt i RISC V. | ISA-kodningsskemaet er fastsat i MIPS |

| Instruktionssættets størrelse er 16-bit eller 32-bit eller 64-bit eller 128-bit. | Instruktionssættets størrelse er 32-bit eller 64-bit. |

| Den har 32 registre til generelle formål og flydende komma | Den har 31 registre til generelle formål og flydende komma. |

| Den har 26 enkelt og dobbelt præcision flydende komma operationer. | Den har 15 enkelt og dobbelt præcision flydende komma operationer. |

Forskel S/H RISC V Vs ARM

Forskellen mellem RISC V og ARM inkluderer følgende.

|

RISC V |

ARM |

| RISC-V er open source, så det kræver ingen licens. | ARM er en lukket kilde, så den har brug for en licens. |

| Det er en ny processorplatform, så der er meget lille support til software & programmeringsmiljøer. | ARM har et meget stort online-fællesskab, som understøtter biblioteker og strukturer for at hjælpe måldesignerne på forskellige platforme som mikroprocessorer, mikrocontrollere og også servere. |

| RISC V-baserede chips bruger 1 watt strøm. | ARM-baserede chips bruger under 4 watt strøm. |

| Den har et fast og variabelt ISA-kodningssystem. | Den har et fast ISA-kodningssystem. |

| RISC V-instruktionssættets størrelse spænder fra 16-bit til 128-bit. | Dens instruktionsstørrelse spænder fra 16-bit til 64-bit. |

| Det inkluderer 32 registre til generelle formål og flydende komma. | Det inkluderer 31 registre til generelle formål og flydende komma. |

| Den har 26-enkelt præcision flydende komma operationer. | Den har 33-enkelt præcision flydende komma operationer. |

| Den har 26-dobbelt præcision flydende komma operationer. | Den har 29-dobbelt præcision flydende komma operationer. |

RISC V Verilog-kode

Instruktionshukommelsens verilog-kode for RISC er vist nedenfor.

// Verilog-kode til RISC-processor

// Verilog-kode til instruktionshukommelse

modul Instruction_Memory(

input[15:0] pc,

output[15:0] instruktion

);

reg [`col – 1:0] memory [`row_i – 1:0];

wire [3 : 0] rom_addr = pc[4 : 1];

initial

begynde

$readmemb(“./test/test.prog”, memory,0,14);

ende

tildel instruktion = memory[rom_addr];

slutmodul

Verilog-kode til 16-bit RISC V-processoren:

modul Risc_16_bit(

input clk

);

trådspring,bne,beq,mem_read,mem_write,alu_src,reg_dst,mem_to_reg,reg_write;

wire[1:0] alu_op;

wire [3:0] opcode;

// Datasti

Datapath_Unit DU

(

.clk(clk),

.jump(spring),

.frog(frø),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.reg_write(reg_write),

.bne(bne),

.alu_op(alu_op),

.opcode(opcode)

);

// styreenhed

Kontrol_Enhedskontrol

(

.opcode(opcode),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.alu_op(alu_op),

.jump(spring),

.bne(bne),

.frog(frø),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_write(reg_write)

);

slutmodul

Instruktionssæt

RISC V instruktionssættene er beskrevet nedenfor.

Aritmetiske operationer

RISC V aritmetiske operationer er angivet nedenfor.

| Mnemonisk | Type | Instruktion | Beskrivelse |

| TILFØJ rd, rs1, rs2 |

R |

Tilføje | rdß rs1 + rs2 |

| SUB rd, rs1, rs2 |

R |

Trække fra | rdß rs1 – rs2 |

| ADDI rd, rs1, imm12 |

jeg |

Tilføj straks | rdß rs1 + imm12 |

| SLT rd, rs1, rs2 |

R |

Indstil mindre end | rdß rs1 -< rs2 |

| SLTI rd, rs1, imm12 |

jeg |

Indstil mindre end øjeblikkeligt | rdß rs1 -< imm12 |

| SLTU rd, rs1, rs2 |

R |

Indstil mindre end usigneret | rdß rs1 -< rs2 |

| SLTIU rd, rs1, imm12 |

jeg |

Indstil mindre end øjeblikkelig usigneret | rdß rs1 -< imm12 |

| LUI rd, imm20 |

I |

Indlæs øverste øjeblikkeligt | rdß imm20<<12 |

| AUIP rd, imm20 |

I |

Tilføj øvre øjeblikkelig til pc | rdß PC+imm20<<12 |

Logiske operationer

RISC V logiske operationer er anført nedenfor.

| Mnemonisk | Type | Instruktion | Beskrivelse |

| OG rd, rs1, rs2 |

R |

OG | rdß rs1 & rs2 |

| ELLER rd, rs1, rs2 |

R |

ELLER | rdß rs1 | rs2 |

| XOR rd, rs1, rs2 |

R |

LEDIG | rdß rs1 ^ rs2 |

| ANDI rd, rs1, imm12 |

jeg |

OG øjeblikkelig | rdß rs1 & imm2 |

| ORI rd, rs1, imm12 |

jeg |

ELLER Straks | rdß rs1 | imm12 |

| OXRI rd, rs1, imm12 |

jeg |

XOR øjeblikkeligt | rdß rs1 ^ rs2 |

| SLL rd, rs1, rs2 |

R |

Skift til venstre logisk | rdß rs1 << rs2 |

| SRL rd, rs1, rs2 |

R |

Skift til højre logisk | rdß rs1 >> rs2 |

| RAS rd, rs1, rs2 |

R |

Skift til højre aritmetik | rdß rs1 >> rs2 |

| SLLI rd, rs1, shamt |

jeg |

Skift logisk til venstre med det samme | rdß rs1 << shamt |

| SRLI rd, rs1, shamt |

jeg |

Skift logisk til højre med det samme | rdß rs1 >> shamt |

| SRAI rd, rs1, shamt |

jeg |

Skift højre aritmetik med det samme | rdß rs1 >> shamt |

Indlæsnings-/lageroperationer

RISC V-indlæsnings-/lageroperationerne er anført nedenfor.

| Mnemonisk | Type | Instruktion | Beskrivelse |

| LD rd, imm12 (rs1) |

jeg |

Indlæs dobbeltord | rdß mem [rs1 +imm12] |

| LW rd, imm12 (rs1) |

jeg |

Indlæs ord | rdß mem [rs1 +imm12] |

| LH rd, imm12 (rs1) |

jeg |

Læs halvvejs | rdß mem [rs1 +imm12] |

| LB rd, imm12 (rs1) |

jeg |

Indlæs byte | rdß mem [rs1 +imm12] |

| LWU rd, imm12 (rs1) |

jeg |

Indlæs ord usigneret | rdß mem [rs1 +imm12] |

| LHU rd, imm12 (rs1) |

jeg |

Indlæs halvt ord usigneret | rdß mem [rs1 +imm12] |

| LBU rd, imm12 (rs1) |

jeg |

Indlæs byte usigneret | rdß mem [rs1 +imm12] |

| SD rs2, imm12 (rs1) |

S |

Gem dobbeltord | rs2 til mem [rs1 +imm12] |

| SW rs2, imm12 (rs1) |

S |

Gem ord | rs2 (31:0) til mem [rs1 +imm12] |

| SH rs2, imm12 (rs1) |

S |

Opbevar halvvejs | rs2 (15:0) til mem [rs1 +imm12] |

| SB rs2, imm12 (rs1) |

S |

Gem byte | rs2 (15:0) til mem [rs1 +imm12] |

| SRAI rd, rs1, shamt |

jeg |

Skift højre aritmetik med det samme | rs2 (7:0) til mem [rs1 +imm12] |

Forgreningsdrift

RISC V-forgreningsaktiviteterne er anført nedenfor.

| Mnemonisk | Type | Instruktion | Beskrivelse |

| BEQ rs1, rs2, imm12 |

SB |

Gren lig | Hvis rs1== rs2 PC ß PC+imm12 |

| BNE rs1, rs2, imm12 |

SB |

Gren ikke lige | Hvis rs1!= rs2 PC ß PC+imm12 |

| BGE rs1, rs2, imm12 |

SB |

Gren større end eller lig | Hvis rs1>= rs2 PC ß PC+imm12 |

| BGEU rs1, rs2, imm12 |

SB |

Gren større end eller lig med usigneret | Hvis rs1>= rs2 PC ß PC+imm12 |

| BLT rs1, rs2, imm12 |

SB |

Filial mindre end | Hvis rs1< rs2 PC ß PC+imm12 |

| BLTU rs1, rs2, imm12 |

SB |

Filial mindre end usigneret | Hvis rs1< rs2 PC ß PC+imm12 <<1 |

| JAL rd, imm20 |

UJ |

Hop og Link | rdßPC+4 PCß PC+imm20 |

| JALR rd, imm12(rs1) |

jeg |

Hop og Link register | rdßPC+4 PCß rs1+imm12 |

Fordele

Det fordelene ved RISC V processor omfatte følgende.

- Ved at bruge RISCV kan vi spare udviklingstid, softwareudvikling, verifikation mv.

- Denne processor har mange fordele som enkelhed, åbenhed, modularitet, rent tavledesign og udvidelsesmuligheder.

- Dette understøttes af adskillige sprogkompilere som GCC (GNU Compiler Collection), en gratis software-kompiler og gennem Linux OS .

- Dette kan bruges af virksomheder frit på grund af ingen royalties, ingen licensgebyrer og ingen bindinger.

- RISC-V-processoren indeholder ingen nye eller innovative funktioner, fordi den blot følger etablerede principper for RISC.

- I lighed med flere andre ISA'er definerer denne processorspecifikation blot forskellige instruktionssætniveauer. Så dette indeholder 32 & 64-bit varianter samt udvidelser for at give support til floating point instruktioner.

- Disse er gratis, enkle, modulære, stabile osv.

Ulemper

Det ulemper ved RISC V-processoren omfatte følgende.

- Komplekse instruktioner bruges ofte af compilere og programmører.

- O/p af en RISC kan ændre sig baseret på koden, når efterfølgende instruktioner i en loop afhænger af den tidligere instruktion til udførelse.

- Disse processorer skal gemme en række instruktioner hurtigt, hvilket kræver et stort cachehukommelsessæt for at reagere på instruktionen inden for en rettidig måde.

- De komplette funktioner, muligheder og fordele ved RISC afhænger hovedsageligt af arkitekturen.

Ansøgninger

Det anvendelser af RISC V processor omfatte følgende.

- RISC-V bruges i indlejrede systemer, kunstig intelligens og maskinlæring.

- Disse processorer bruges i højtydende-baserede indlejrede systemapplikationer.

- Denne processor er egnet til at bruge i nogle bestemte områder som edge computing, AI og lagringsapplikationer.

- RISC-V er vigtigt, da det giver mindre enhedsproducenter mulighed for at designe hardware uden at betale.

- Denne processor giver simpelthen forskerne og udviklerne mulighed for at designe såvel som forskning med en frit tilgængelig ISA- eller instruktionssæt-arkitektur.

- Anvendelsen af RISC V spænder fra små indlejrede mikrocontrollere til stationære pc'er og supercomputere inklusive vektorprocessorer.

Dette er således en oversigt over en RISC V-processor – arkitektur, arbejde med applikationer. Her er et spørgsmål til dig, hvad er en CISC-processor?