JTAG (Joint Test Action Group) er en veletableret IEEE 1149.1 standard, der blev udviklet i år 1980 for at løse de produktionsproblemer, der opstod inden for elektroniske tavler eller printplader . Denne teknologi bruges til at give tilstrækkelig testadgang til hvert komplekst bord, når testadgangen var faldende. Således blev grænsescanningsteknologi lanceret & JTAG-standarden eller JTAG specifikation er etableret. Kompleksiteten af elektronik er vokset dag for dag, så JTAG-specifikationen er blevet det accepterede testformat til at teste komplicerede og kompakte elektronikenheder. Denne artikel diskuterer en oversigt over en JTAG protokol – arbejde med applikationer.

Hvad er JTAG?

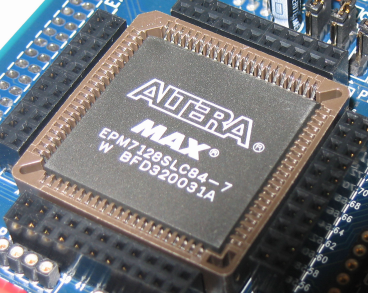

Navnet, som er givet til IEEE 1149.1 Standard Test Access Port samt Boundary-Scan Architecture er kendt som JTAG (Joint Test Action Group). Denne grænsescanningsarkitektur bruges mest inden for computere processorer fordi den første processor med JTAG blev udgivet af Intel. Denne IEEE-standard definerer blot, hvordan en computers kredsløb testes for at bekræfte, om den fungerer korrekt efter fremstillingsproceduren. På printpladerne udføres test for at kontrollere loddesamlingerne.

Joint Test Action Group giver testere en pins-out-visning med hver IC-pad, som hjælper med at identificere eventuelle fejl på et printkort. Når først denne protokol er forbundet med en chip, kan denne vedhæfte en sonde til chippen ved at tillade en udvikler at kontrollere chippen såvel som dens forbindelser med andre chips. Interfacet med Joint Test Action-gruppen kan også bruges af udviklere til at kopiere firmwaren til ikke-flygtig hukommelse i en elektronisk enhed.

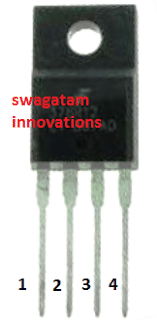

Konfiguration/Pin Out

Joint Test Action Group inkluderer 20-ben, hvor hver pin og dens funktion er diskuteret nedenfor.

Pin1 (VTref): Dette er målreferencespændingsbenet, der bruges til at forbinde til målets hovedstrømforsyning, som spænder fra 1,5 til 5,0 VDC.

Pin2 (Vsupply): Dette er målforsyningsspændingen, der bruges til at tilslutte hovedspændingsforsyningen til mål 1,5VDC – 5,0VDC.

Pin3 (nTRST): Dette er en testnulstillingsstift, der bruges til at nulstille TAP-controllerens tilstandsmaskine.

Pins (4, 6, 8, 10, 12, 14, 16, 18 og 20): Disse er almindelige GND-stifter.

Pin5 (TDI): Dette er testdata i stiften. Disse data flyttes ind i målenheden. Denne stift skal trækkes op på en defineret tilstand på målbrættet.

Pin7 (TMS): Dette er Test Mode State-stiften, der trækkes for at bestemme den næste tilstand af TAP-controllerens tilstandsmaskine.

Pin9 (TCK): Dette er en test-ur-pin, der synkroniserer de interne tilstandsmaskiners operationer i TAP-controlleren.

Pin11 (RTCK): Dette er Input Return TCK pin, der bruges i enheder, der understøtter adaptiv clocking.

Pin13 (TDO): Dette er Test Data Out-pinden, så data flyttes ud af målenheden og ind i Fluesmækkeren.

Pin15 (nSRST): Dette er målsystemets nulstillingsstift, som er forbundet til målets primære nulstillingssignal.

Ben 17 og 19 (NC): Disse er ikke tilsluttede ben.

JTAG virker

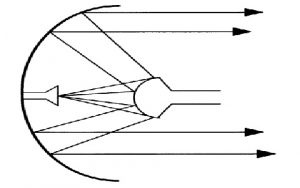

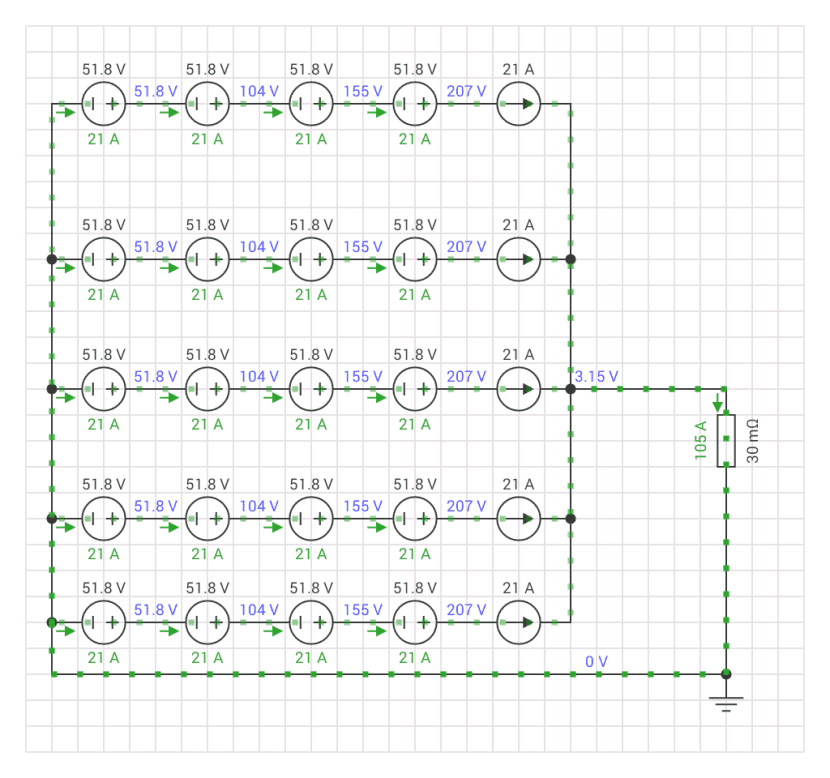

JTAG'ens oprindelige brug er til grænsetest. Her er et simpelt printkort inklusive to IC'er som CPU & FPGA . Et typisk kort kan indeholde mange IC'er. Generelt inkluderer IC'er mange ben, der er forbundet sammen med mange forbindelser. Her, i det følgende diagram, er der kun vist fire forbindelser.

Så hvis du designer mange boards, hvor hvert board har tusindvis af forbindelser. I det er der nogle dårlige tavler. Så vi er nødt til at tjekke, hvilket bord der virker, og hvilket der ikke virker. Til det blev Joint Test Action Group designet.

Denne protokol kan bruge kontrolbenene på alle chipsene, men i det følgende diagram vil Joint Test Action Group lave alle udgangsbenene på CPU'en og alle inputbenene på FPGA. Derefter, ved at transmittere en vis mængde data fra benene på CPU'en og læse værdierne af pindene fra FPGA'en, siger JTAG, at tilslutningerne til printkortet er i orden.

Faktisk inkluderer Joint Test Action Group fire logiske signaler TDI, TDO, TMS & TCK. Og disse signaler skal forbindes på en bestemt måde. I første omgang er TMS & TCK forbundet parallelt med alle IC'er i JTAG.

Derefter er både TDI og TDO forbundet for at danne en kæde. Som du kan observere, inkluderer hver JTAG-kompatibel IC 4-ben, som bruges til JTAG, hvor 3-ben er input og 4. ben er output. Den femte pin som TRST er valgfri. Normalt deles JTAG-stifterne ikke til andre formål.

Ved at bruge Joint Test Action Group bruger alle IC'er grænsetest, som den oprindelige årsag er skabt af JTAG. På nuværende tidspunkt er brugen af denne protokol blevet udvidet til at tillade forskellige ting som at konfigurere FPGA'er, og derefter bruges JTAG i FPGA-kernen til fejlfindingsformål.

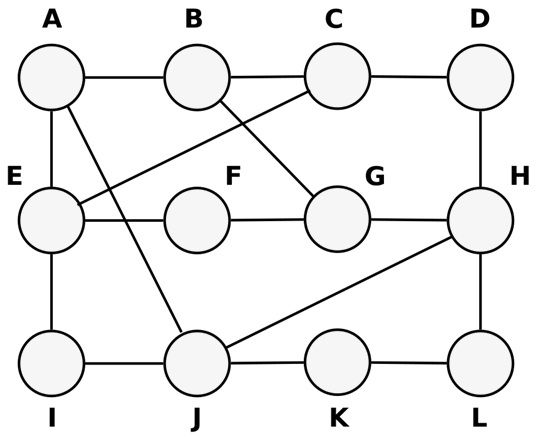

JTAG arkitektur

JTAG-arkitekturen er vist nedenfor. I denne arkitektur bliver alle signalerne mellem enhedens kernelogik og stifterne afbrudt gennem en seriel scanningssti kaldet BSR eller Boundary Scan Register. Denne BSR inkluderer forskellige grænsescannings-'celler'. Generelt er disse grænsescanningsceller ikke synlige, men de kan bruges til at indstille eller læse værdier i testtilstand fra enhedens ben.

JTAG-grænsefladen kaldet en TAP eller Test Access Port bruger forskellige signaler til at understøtte grænsescanningsoperationen som TCK, TMS, TDI, TDO og TRST.

- TCK- eller Test Clock-signalet synkroniserer simpelthen de indvendige operationer af en tilstandsmaskine.

- TMS eller Test Mode Select-signal samples ved den stigende flanke af et test-ursignal for at bestemme den næste tilstand.

- TDI eller Test Data In-signal angiver de flyttede data ind i testenheden ellers programmeringslogik. Når først den indvendige tilstandsmaskine er i den rigtige tilstand, bliver den samplet ved den stigende kant af TCK.

- TDO eller Test Data Out-signal angiver de udskiftede data fra testenheden ellers programmeringslogik. Når først den indvendige tilstandsmaskine er i den rigtige tilstand, er den gyldig på den faldende kant af TCK

- TRST eller Test Reset er en valgfri pin, der bruges til at nulstille TAP-controllerens tilstandsmaskine.

TAP-controller

Testadgangspunktet i JTAG's arkitektur er sammensat af en TAP-controller, et instruktionsregister og testdataregistre. Denne controller inkluderer testtilstandsmaskinen, som er ansvarlig for at læse TMS- og TCK-signalerne. Her bruges data i/p-pinden blot til at indlæse data i grænsecellerne mellem IC-kernen og fysiske ben, og også indlæse data i et af dataregistrene eller i instruktionsregisteret. Data o/p pin bruges til at læse data fra enten registrene eller grænseceller.

TAP-controllerens tilstandsmaskine styres af TMS'en, og den clockes af TCK. Statsmaskine bruger to stier til at betegne to forskellige tilstande som instruktionstilstand og datatilstand.

Registre

Der er to slags registre tilgængelige inden for grænsescanning. Hver kompatibel enhed inkluderer mindst to eller flere dataregistre og et instruktionsregister.

Instruktionsregister

Instruktionsregisteret bruges til at holde den aktuelle instruktion. Så dens data bruges af TAP-controlleren til at beslutte, hvad der skal udføres med signaler, der opnås. Oftest vil instruktionsregisterdataene beskrive, til hvilke af dataregistrene signaler skal sendes.

Dataregistre

Dataregistrene er tilgængelige i tre typer: BSR (Boundary Scan Register), BYPASS & ID CODES registret. Og også andre dataregistre kan være der, men de er ikke nødvendige som et element i JTAG-standarden.

Boundary Scan Register (BSR)

BSR er det vigtigste testdataregister, der bruges til at flytte data fra og til enhedens I/O-ben.

OMGANG

Bypass er et enkelt-bit register, der bruges til at sende data fra TDI – TDO. Så det tillader yderligere enheder i et kredsløb at blive testet med minimum overhead.

ID-KODER

Denne type dataregister inkluderer ID-koden samt revisionsnummeret for enheden. Så disse data gør det muligt for enheden at blive forbundet til dens BSDL-fil (Boundary Scan Description Language). Denne fil indeholdt Boundary Scan-konfigurationsdetaljerne for enheden.

Funktionen af JTAG er i første omgang, at instruktionstilstanden vælges, hvor en af tilstandene i denne tilstands 'sti' lader operatøren klokke inden for en instruktion fra TDI. Derefter udvikler statsmaskinen sig, indtil den omarrangerer. Det næste trin for de fleste instruktioner er at vælge datatilstanden. Så i denne tilstand indlæses dataene gennem TDI for at læse fra TDO. For TDI & TDO vil datastierne blive arrangeret i overensstemmelse med den instruktion, der er blevet clocket ind. Når først læse/skrive-operationen er udført, udvikler tilstandsmaskinen igen til nulstillingstilstanden.

Forskellen mellem JTAG vs UART

Forskellen mellem JTAG og UART inkluderer følgende.

| JTAG |

UART |

| Udtrykket 'JTAG' står for Joint Test Action Group. | Begrebet ' UART ” står for Universal Asynchronous Receiver/Transmitter. |

| Det er en synkron grænseflade, der bruger indbygget hardware til programmering af flashen . | UART er en asynkron grænseflade, der bruger en bootloader, der kører i hukommelsen. |

| Det er et sæt testporte, som bruges til fejlfinding, men som også kan bruges til at programmere firmware (hvilket ofte er gjort).

|

UART er en type chip, der styrer kommunikation til og fra en enhed, såsom en mikrocontroller, ROM, RAM osv. Det meste af tiden er det en seriel forbindelse, der giver os mulighed for at kommunikere med en enhed. |

| Disse fås i fire typer TDI, TDO, TCK, TMS & TRST. | Disse fås i to typer dumb UART & FIFO UART. |

| Joint Test Action Group er seriel programmering eller dataadgangsprotokol, der bruges i grænsefladen mellem mikrocontrollere og relaterede enheder. | En UART er en slags chip ellers mikrocontrollers underkomponent, som bruges til at levere hardwaren til at generere en asynkron seriel strøm som RS-232/RS-485. |

| JTAG-komponenter er processorer, FPGA'er, CPLD'er , etc. | UART-komponenter er CLK-generator, I/O-skifteregistre, sende- eller modtagebuffere, systemdatabusbuffer, læse- eller skrivekontrollogik osv. |

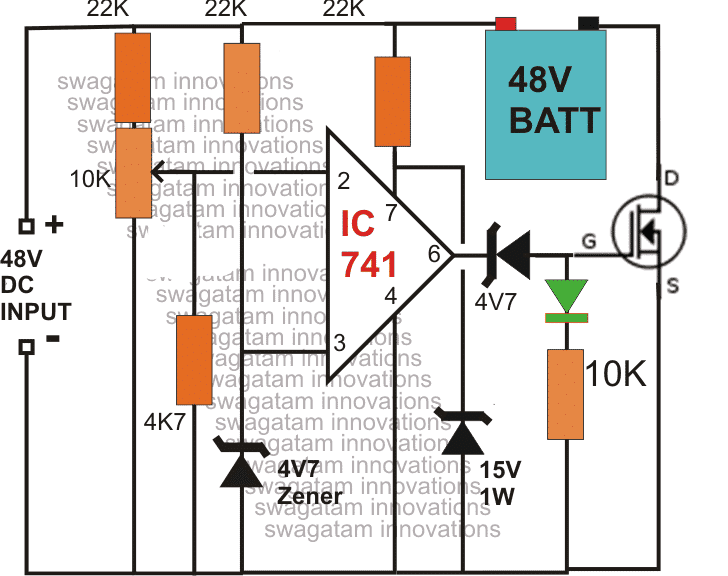

JTAG Protocol Analyzer

JTAG Protocol Analyzer som PGY-JTAG-EX-PD er en slags Protocol Analyzer, der inkluderer nogle funktioner til at fange og fejlfinde kommunikation mellem vært og design under test. Denne type analysator er det førende instrument, der gør det muligt for test- og designingeniørerne at teste de særlige designs af JTAG for dets specifikationer ved at arrangere PGY-JTAG-EX-PD som Master eller Slave for at generere JTAG-trafik og afkode afkodningspakkerne i Joint Test Action Group protokol.

Funktioner

Funktionerne i JTAG-protokolanalysatoren omfatter følgende.

- Den understøtter op til 25MH JTAG-frekvenser.

- Det genererer JTAG-trafik og protokolafkodning til bussen samtidigt.

- Den har JTAG Master Capability.

- Variable JTAG-datahastigheder og driftscyklus.

- Brugerdefinerede TDI & TCK Delays.

- Værtscomputer USB 2.0 eller 3.0 interface.

- Fejlanalyse inden for protokolafkodning

- Protokol dekodet bus timing diagram.

- Kontinuerlig protokoldatastreaming til værtscomputeren for at give en stor buffer.

- Protokol aktivitetsliste.

- Ved forskellige hastigheder kan et øvelsesscript skrives til at kombinere generering af flere dataramme.

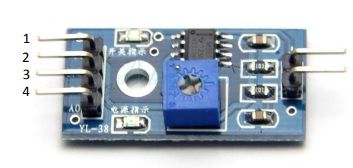

Tidsdiagram

Det tidsdiagram af JTAG protokollen er vist nedenfor. I det følgende diagram forbliver TDO-stiften inden for højimpedanstilstanden undtagen under en skift-IR/skift-DR-controllertilstand.

I skift-IR- og Shift-DR-controllerbetingelserne opdateres TDO-pinden på den faldende kant af TCK gennem Target og samples på den stigende kant af TCK gennem Host.

Både TDI- og TMS-stifterne er simpelthen samplet på den stigende kant af TCK gennem Target. Opdateret på den faldende kant ellers TCK gennem Host.

Ansøgninger

Det JTAG applikationer omfatte følgende.

- Joint Test Action Group bruges ofte i Processorer til at give adgangsretten til deres emulerings- eller debug-funktioner.

- Alle CPLD'er og FPGA'er bruger dette som en grænseflade for at give adgang til deres programmeringsfunktioner.

- Det bruges til PCB-test uden fysisk adgang

- Det bruges til fremstillingstests på tavleniveau.

Det handler altså om en oversigt over JTAG – pin-konfiguration, arbejde med applikationer. Industristandarden JTAG bruges til designverifikation samt PCB-testning efter fremstilling. Her er et spørgsmål til dig, JTAG står for?