MOS-transistoren er det mest grundlæggende element i design af integrerede kredsløb i stor skala. Disse transistorer er generelt klassificeret i to typer PMOS og NMOS. Kombinationen af NMOS- og PMOS-transistorer er kendt som en CMOS transistor . Det anderledes logiske porte & andre digitale logiske enheder, som er implementeret, skal have PMOS-logik. Denne teknologi er billig og har god modstandsdygtighed over for interferens. Denne artikel diskuterer en af typerne af MOS-transistorer som en PMOS-transistor.

Hvad er PMOS-transistor?

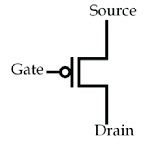

PMOS-transistoren eller P-kanal metaloxid-halvlederen er en slags transistor, hvor p-type dopingmidler anvendes i kanal- eller gate-området. Denne transistor er præcis det modsatte af NMOS-transistoren. Disse transistorer har tre hovedterminaler; source, gate & drain, hvor transistorens source er designet med et p-type substrat, og drain terminalen er designet med et n-type substrat. I denne transistor er ladningsbærerne som huller ansvarlige for ledningen af strøm. PMOS-transistorsymbolerne er vist nedenfor.

Hvordan virker PMOS-transistor?

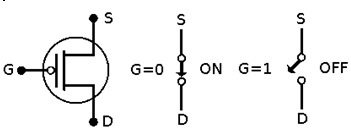

P-type transistoren fungerer helt modsat af n-type transistoren. Denne transistor vil danne et åbent kredsløb, når den får en ikke-ubetydelig spænding, hvilket betyder, at der ikke er nogen strøm af elektricitet fra porten (G) terminalen til kilden (S). På samme måde danner denne transistor et lukket kredsløb, når den får en spænding på omkring 0 volt, hvilket betyder, at strømmen løber fra gate (G) terminalen til drænet (D).

Denne boble er også kendt som en inversionsboble. Så hovedfunktionen af denne cirkel er at invertere indgangsspændingsværdien. Hvis gateterminalen giver en 1-spænding, vil denne inverter ændre den til nul og fungerer kredsløbet i overensstemmelse hermed. Så funktionen af PMOS-transistoren og NMOS-transistoren er helt modsat. Når vi fusionerer dem til et enkelt MOS-kredsløb, bliver det et CMOS-kredsløb (komplementært metal-oxid-halvleder).

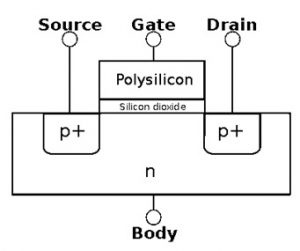

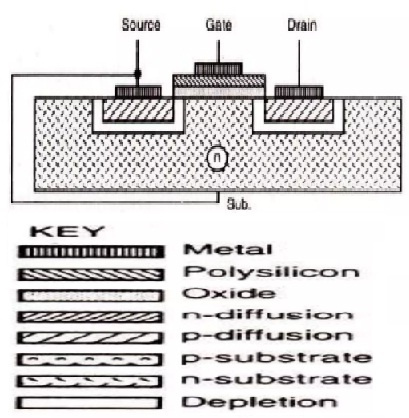

Tværsnit af PMOS-transistor

Tværsnittet af PMOS-transistoren er vist nedenfor. En pMOS-transistor er bygget med en n-type krop, der inkluderer to p-type halvlederområder, som støder op til porten. Denne transistor har en kontrollerende gate som vist i diagrammet, der styrer elektronstrømmen mellem de to terminaler som source & drain. I pMOS-transistoren holdes kroppen på +ve spænding. Når portterminalen er positiv, er source- og drainterminalerne omvendt forspændt. Når dette sker, er der ingen strøm, så transistoren vil blive slukket.

Når spændingsforsyningen ved gateterminalen er sænket, vil positive ladningsbærere blive tiltrukket til bunden af Si-SiO2-grænsefladen. Når spændingen bliver tilstrækkelig lav, vil kanalen blive inverteret og skaber en ledende bane fra kildeterminalen til drænet ved at tillade strømmen.

Når disse transistorer beskæftiger sig med digital logik, har der normalt kun to forskellige værdier som 1 & 0 (ON og OFF). Transistorens positive spænding er kendt som VDD, som repræsenterer den logiske høje (1) værdi i digitale kredsløb. VDD-spændingen stiger ind TTL logik var generelt omkring 5V. På nuværende tidspunkt kan transistorer faktisk ikke modstå så høje spændinger, fordi de typisk spænder fra 1,5V – 3,3V. Lavspændingen er ofte kendt som GND eller VSS. Så VSS betegner logikken '0', og den er også indstillet normalt til 0V.

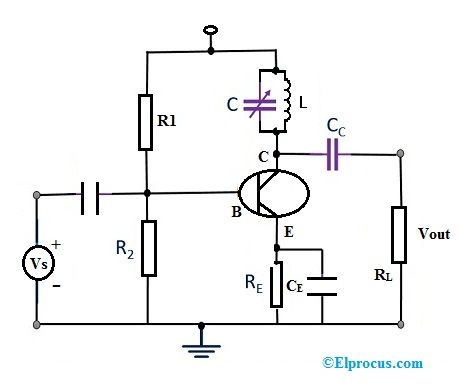

PMOS transistorkredsløb

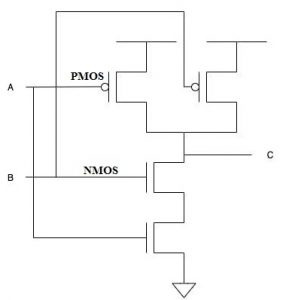

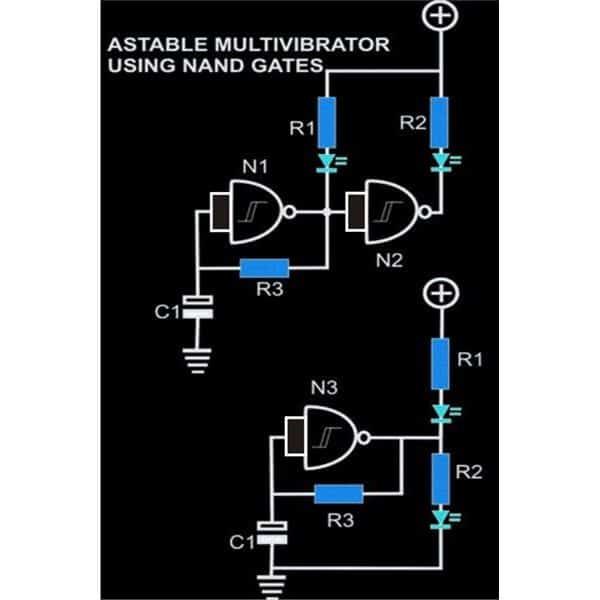

NAND-portdesignet ved hjælp af PMOS-transistoren og NMOS-transistoren er vist nedenfor. Generelt er en NAND-port i digital elektronik en logisk port, som også kaldes en IKKE-OG-port. Outputtet af denne gate er kun lav (0), hvis de to input er høje (1), og dens output er et komplement til en AND-gate. Hvis nogen af de to indgange er LAV (0), giver det høje outputresultater.

I nedenstående logiske kredsløb, hvis input A er 0 og B er 0, vil en input af pMOS producere '1' og en input på nMOS vil producere '0'. Så denne logiske gate genererer en logisk '1', fordi den er forbundet til kilden af et lukket kredsløb og adskilt fra GND gennem et åbent kredsløb.

Når A er '0' & B' er '1', så vil et input af pMOS generere en '1' og et input fra NMOS vil generere et '0'. Således vil denne gate producere en logisk, fordi den er forbundet til kilden gennem et lukket kredsløb og adskilt fra GND af et åbent kredsløb. Når A er '1' og B er '0', vil 'B'-input af pMOS generere høj output (1) og 'B' input af NMOS vil generere et output så lavt (0). Så denne logiske gate vil generere en logisk 1, fordi den er forbundet til kilden gennem et lukket kredsløb og adskilt fra GND af et åbent kredsløb.

Når A er '1' og B er '1', så vil et input af' pMOS producere et nul, og et input af nMOS vil generere '1'. Derfor bør vi også verificere B-input af pMOS & nMOS. B-input af pMOS vil generere en '0' og B-input af nMOS vil generere en '1'. Så denne logiske gate vil generere en logisk '0', fordi den er adskilt fra kilden af et åbent kredsløb og er forbundet til GND gennem et lukket kredsløb.

Sandhedstabel

Sandhedstabellen for ovenstående logiske kredsløb er givet nedenfor.

|

EN |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

Tærskelspændingen for PMOS-transistoren er normalt 'Vgs', som er nødvendig for at skabe kanalen kendt som kanalinversion. I en PMOS-transistor er substratet og kildeterminalerne simpelthen forbundet til 'Vdd'. Hvis vi begynder at reducere spændingen ved at henvise til kildeterminalen ved gateterminalen fra Vdd til et punkt, hvor end du bemærker kanalinversionen, ved denne position, hvis du analyserer Vgs & kilden på det høje potentiale, vil du få en negativ værdi. Så PMOS-transistoren har en negativ femte værdi.

PMOS fremstillingsproces

De trin, der er involveret i PMOS-transistorfremstilling, er diskuteret nedenfor.

Trin 1:

Et tyndt siliciumwaferlag ændres til N-type materiale ved blot at dope fosformateriale.

Trin 2:

Et tykt siliciumdioxid (Sio2) lag dyrkes på et komplet p-type substrat.

Trin 3:

Nu er overfladen belagt med en fotoresist over det tykke siliciumdioxidlag.

Trin 4:

Derefter udsættes dette lag ganske enkelt for UV-lys gennem en maske, der definerer de områder, hvori diffusion skal finde sted sammen med transistorkanaler.

Trin 5:

Disse områder ætses væk indbyrdes med den underliggende siliciumdioxid, således at overfladen af waferen blotlægges inden for vinduet defineret af masken.

Trin 6:

Den resterende fotoresist løsnes, og tyndt Sio2-lag dyrkes typisk 0,1 mikrometer over hele overfladen af chippen. Derefter placeres polysilicium over dette for at danne strukturen af porten. En fotoresist placeres over hele polysiliciumlaget og eksponerer UV-lys gennem masken2.

Trin 7:

Diffusioner opnås gennem wafer-opvarmning til maksimal temperatur og passerer gas med ønskede p-type urenheder som bor.

Trin 8:

En 1-mikrometer tykkelse siliciumdioxid dyrkes, og fotoresistmateriale afsættes på det. Udsæt det ultraviolette lys med maske3 på de foretrukne områder af porten, kilden og afløbet, som er ætset for at få kontaktskæringerne.

Trin 9:

Nu er et metal eller aluminium aflejret over dets 1-mikrometer tykkelse overflade. Igen dyrkes et fotoresistmateriale over hele metallet og eksponerer UV-lyset gennem mask4, som er ætset for at danne det nødvendige sammenkoblingsdesign. Den endelige PMOS-struktur er vist nedenfor.

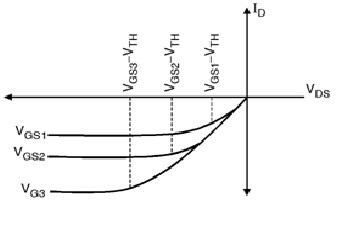

PMOS-transistoregenskaber

PMOS transistor I-V karakteristika er vist nedenfor. Disse karakteristika er opdelt i to regioner for at opnå forholdet mellem dræn-til-kildestrømmen (I DS) såvel som dens terminalspændinger som lineære og mætningsområder.

I en liner-region vil IDS lineært stige, når VDS (drain to source-spænding) øges, mens I DS i mætningsområdet er stabil, og den er uafhængig af VDS. Hovedforholdet mellem ISD (kilde til drænstrøm) og dens terminalspændinger er afledt af en lignende procedure for NMOS-transistoren. I dette tilfælde vil den eneste ændring være, at ladningsbærerne i inversionslaget simpelthen er huller. Når hullerne bevæger sig fra kilde til dræn, er strømmen også den samme.

Således vises det negative fortegn inden for den aktuelle ligning. Derudover er alle de anvendte forspændinger ved enhedens terminaler negative. Så PMOS-transistorens ID - VDS-karakteristika er vist nedenfor.

Drænstrømsligningen for PMOS-transistor i det lineære område er givet som:

ID = – mp Cox

Ligeledes er Drain-strømligningen for PMOS-transistor i mætningsområdet givet som:

ID = – mp Cox (VSG – | V TH |p )^2

Hvor 'mp' er hullets mobilitet & '|VTH| p' er PMOS-transistorens tærskelspænding.

I ovenstående ligning vil det negative fortegn angive, at ID( afløbsstrøm ) strømmer fra afløbet (D) til kilden (S), mens huller strømmer i den modsatte retning. Når hullets mobilitet er lav sammenlignet med elektronmobiliteten, lider PMOS-transistorer af lavstrømsdrevets evne.

Dette handler således om en oversigt over PMOS transistor eller p-type mos transistor - fremstilling, kredsløb og dens funktion. PMOS transistorer er designet med en p-kilde, et n-substrat & dræn. Ladningsbærerne af PMOS er huller. Denne transistor leder, når lav spænding er påført ved gateterminalen. PMOS-baserede enheder er mindre tilbøjelige til interferens sammenlignet med NMOS-enheder. Disse transistorer kan bruges som spændingsstyrede modstande, aktive belastninger, strømspejle, transimpedansforstærkere og også bruges i switche og spændingsforstærkere. Her er et spørgsmål til dig, hvad er en NMOS-transistor?

![Ikke-kontakt AC fasedetektor kredsløb [testet]](https://electronics.jf-parede.pt/img/sensors-detectors/38/non-contact-ac-phase-detector-circuit.png)