I vores daglige liv bruger vi ofte kommunikation med andre ved hjælp af flere typer kommunikationssystemer . Dette kommunikationssystem kan klassificeres i forskellige typer, såsom et radiokommunikationssystem, telekommunikationssystem, Trådløst kommunikationssystem , Optisk kommunikationssystem og så videre. For at alle disse kommunikationssystemer skal fungere effektivt, har vi brug for et par kontrolsystemer, såsom en faselåst sløjfe, kooperativ kontrol, netværksstyring og så videre.

Hvad er faselåst sløjfe (PLL)?

Faselåst sløjfe bruges som et kontrolsystem til at styre forskellige operationer i mange kommunikationssystemer, computere og mange elektroniske applikationer . Det bruges til at generere et udgangssignal, der har en fase relateret til indgangssignalfasen.

Der er forskellige typer PLL'er såsom Analog eller Lineær PLL, Digital PLL, Software PLL, Neuronal PLL og al digital PLL.

Faselåst sløjfe

I kommunikationssystemer kan PLL-operationen forklares ved at overveje analoge og digitale systemer .

Analog faselåst sløjfe i kommunikationssystemer

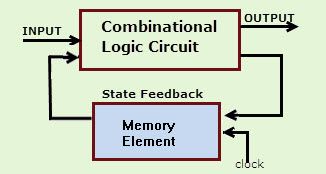

Grundlæggende er PLL en form for servosløjfe, og en grundlæggende PLL består af tre hovedelementer, nemlig fasekomparator / detektor, loopfilter og spændingsstyret oscillator .

Faselåst sløjfe

Hovedkonceptet bag PPL-operationen er sammenligning af faserne i to signaler (generelt sammenlignes input- og output-signalfaser). Således kan faseforskellen mellem indgangs- og udgangssignalet anvendes til styring af sløjfefrekvensen. Selvom matematisk analyse er meget kompliceret, men betjeningen af PLL er meget enkel.

I mange kommunikationssystemer bruges PLL til forskellige formål:

- Til at følge fasen eller frekvensmodulation , det bruges som demodulator.

- At spore eller synkronisere de to signaler med forskellige frekvenser.

- For at fjerne store lyde fra små signaler.

Nedenstående figur viser den grundlæggende PLL, der består af fasedetektor, spændingsstyret oscillator (VCO), sløjfefilter.

Den spændingsstyrede oscillator af PLL producerer et signal, og dette signal fra VCO gives til fasedetektoren. Fasedetektoren sammenligner dette signal med referencesignalet og frembringer således en fejlspænding eller forskelsspænding. Dette fejlsignal fra fasedetektoren føres til lavpasfilteret til fjernelse af højfrekvente elementer i signalet - hvis det er tilfældet, og til at styre mange egenskaber ved sløjfen. Derefter tilføres udgangen fra sløjfefilteret til at levere indstillingsspændingen til kontrolterminalen til den spændingsstyrede oscillator.

Ændringen i denne indstillingsspænding registreres for at reducere faseforskellen mellem de to signaler (input og output) og dermed frekvensen mellem dem. Oprindeligt låser PLL ikke, og fejlspændingen trækker VCO-frekvensen mod referencen, indtil fejlen ikke kan reduceres yderligere, og derefter bliver sløjfen låst.

Den faktiske fejl mellem de to signaler (input og output) reduceres til meget små niveauer ved hjælp af en forstærker imellem den spændingsstyrede oscillator og en fasedetektor. Hvis PLL er låst, produceres der en steady-state fejlspænding. Denne steady-state fejlspænding repræsenterer, at der ikke er nogen faseforskelændring mellem referencesignalet og VCO. Således kan vi sige, at frekvensen af de to signaler (input og output signaler) er nøjagtig den samme.

Digital faselåst sløjfe i kommunikationssystemer

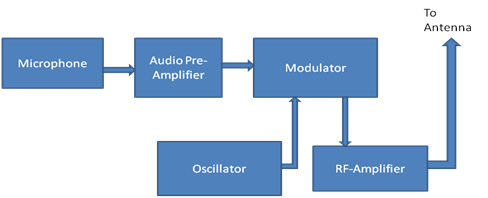

Generelt består analoge PLL'er af en analogfasedetektor, spændingsstyret oscillator og lavpasfilter. Tilsvarende består den digitale faselåste sløjfe af en digitalfasedetektor, a serielt skiftregister , et stabilt lokalt ursignal.

Digital faselåst sløjfe

De digitale indgangssampler ekstraheres fra det modtagne signal, og disse sampler modtages af det serielle skiftregister, der drives af urimpulser leveret fra et lokalt ursignal. Et fasekorrigeringskredsløb, der tager lokalt ur, bruges til at regenerere et stabilt ursignal i fase med det modtagne signal ved langsom fasejustering for at matche den modtagne signalfase.

Denne justering kan udføres baseret på en højhastighedsprøve af hver bit ved hjælp af en korrektionslogik. Den modtagne signalprøve opnået ved samplingen af det modtagne signal ved lokal klokkehastighed placeres i skiftregisteret.

Den nødvendige fasejustering kan detekteres ved at observere sæt af prøver af det modtagne signal. De to ure siges at være i fase, hvis og kun hvis midten af den modtagne bit ligger i midten af skiftregisteret. Fasejustering er beregnet til at kompensere, hvis det regenererede ur halter eller fører referencesignalet.

Anvendelse af faselåst sløjfe

- PLL'er bruges ofte til synkroniseringsformål og til bit-synkronisering, symbolsynkronisering, sammenhængende demodulation og tærskeludvidelse i rumkommunikation.

- De frekvensmodulerede signaler kan demoduleres ved hjælp af PLL.

- Den nye frekvens, som er et multiplum af referencefrekvensen i radiokommunikationssendere og syntetiseres ved at opretholde stabiliteten af referencefrekvensen med den nye frekvens kan opnås med PLL'er.

- Der er mange applikationer til PLL'er i mange kommunikationssystemer, computere og mange elektroniske kredsløb .

- Nedenstående anvendelse af PLL beskriver brugen af PLL som spænding til frekvensomformer .

Voltage to Frequency Converter (VFC) ved hjælp af en PLL

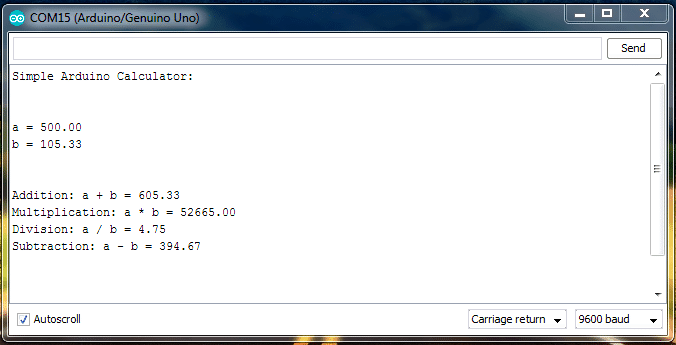

I kommunikationssystemer er det nødvendigt at sende signaler (betragt et analogt signal her) til en lang afstand med fuld nøjagtighed. Til dette formål anvendes en spænding-til-frekvensomformer, da det er let at sende et frekvenssignal uden at forårsage interferens over lang afstand ved hjælp af optiske isolatorer, koaksiale eller snoede par linjer, radioforbindelser, links til optiske fibre .

Der er to typer spænding-til-frekvensomformere, nemlig multivibratortype VFC og opladningsbalancetype VFC.

Multivibrator type VFC

Multivibrator VFC

I multivibrator type VFC oplades kondensatoren og aflades ved hjælp af den strøm, der opnås fra indgangsspændingen. Stabil referenceindgang er givet til at indstille skiftetærskler, og udgangsfrekvensen er proportional med indgangsspændingen og har enhedsmærke-plads-forhold.

Charge Balance type VFC

Charge Balance VFC

Opladningsbalancen VFC består af en integrator, en komparator og en præcis opladningskilde. Hver gang der gives et input til integratoren, oplades det, og hvis output fra denne integrator når komparatortærsklen, udløses ladningskilden og fast opladning fjernes fra integratoren. Den fjernede ladningshastighed skal være lig med den tilførte ladningshastighed, således at ladningskildens udløste frekvens og indgangen til integratoren vil være proportional med hinanden.

Således giver denne artikel en kort beskrivelse af faselåst sløjfesystem i kommunikationssystemet. Yderligere kan denne artikel udvides teknisk baseret på dine forslag og spørgsmål. Derfor kan du henvende os til teknisk support ved at sende dine kommentarer nedenfor.