Indlægget forklarer et overspændingsafskærmningskredsløb i form af dumping til bilindustrien til beskyttelse af følsom og sofistikeret moderne bilelektronik fra forbigående DC elektriske spidser, der stammer fra køretøjets elektriske.

Transiente busspændinger er en væsentlig risikofaktor for integrerede kredsløb. Den maksimale nedbrydningsspænding, som et integreret kredsløb kan specificeres til at tolerere, bestemmes af dets stil og designtilgang, der overvejende kan være lav for små CMOS-enheder.

Hvad er forbigående spænding

Forbigående eller gentagne overspændingsforhold, der besejrer en ICs absolut højeste spændingsspecifikation, kan muligvis skade en enhed irreversibelt.

Nødvendigheden af overspændingssikkerhed er især fremherskende i 12V- og 24V-bilkonstruktioner, hvor peak 'load dump'-transienter normalt er så meget høje som GOV. Visse belastningsbeskyttelsesstrategier shunter input, der er forbigående til jorden gennem enheder, der ligner lavindioder og MOV'er.

Vanskeligheden med shuntmetoden er, at en hel del magt muligvis ender med at blive behandlet.

Shunt-teknikker er normalt uønskede, hvis der er pligt til at yde kontinuerlig beskyttelse i en overspændingssituation (som foregår med dobbelt batteri).

Designet

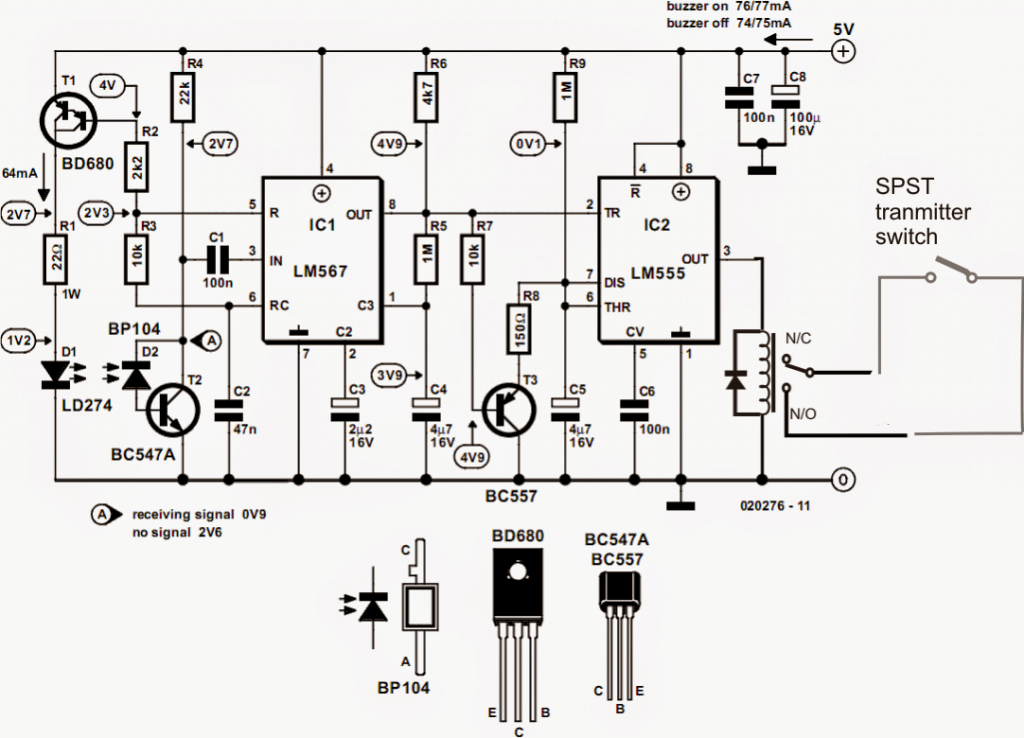

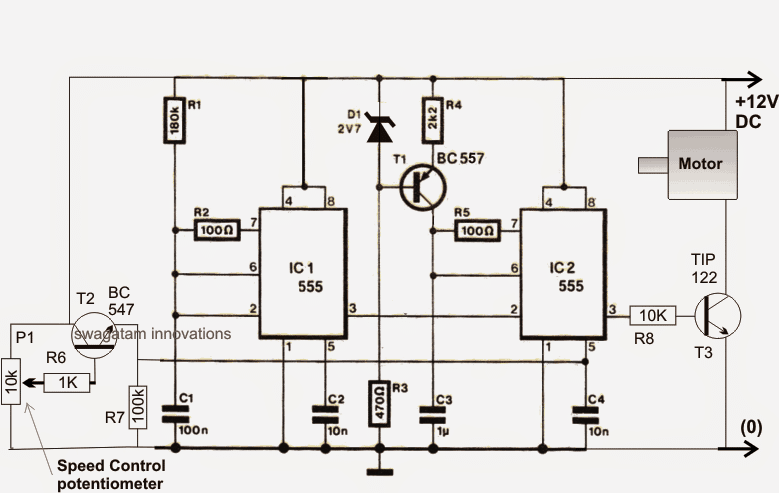

Overspændingsbeskyttelseskredsløbet til automobilbelastningsdump vist i figur 1 er en perfekt seriekobling eller seriekobling, der er bygget til at beskytte en koblingsregulatorbelastning, der har en optimal indgangsspænding på 24V.

Kredsløbet er beregnet fra økonomiske diskrete enheder og bruger en enkelt Texas Instruments LMV431AIMF.

I betragtning af at dette kredsløb anvender en PFET-passeringsenhed (Q1), kan der være et marginalt fremadspændingsfald eller relateret effekttab.

Kredsløbsdiagram

Figur 1

Høflighed : Overspændingsbeskyttelseskredsløb til bilaflastning

Sådan fungerer LM431AIMF-diode

LMV431AIMF (D1) -tilpasningsreferencen fungerer bedst i denne situation, bare fordi den giver mulighed for et billigt middel til at fastslå et omhyggeligt trippunkt og overvåge optimal temperaturnøjagtighed, der bliver ret vanskelig med en zenerdiode eller ligeledes ved hjælp af andre alternative muligheder (1% for En version, 0,5% for B-versionen).

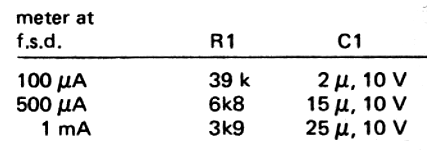

For at bevare denne nøjagtighed og pålidelighed er modstandene R1 og R2 valgt til at være 1% tolerance, eller en endnu bedre kan anbefales.

Variable referencespændinger kan normalt overvejes forkert. Tag for eksempel: 'Hvad afslutter den tredje ledning fra dioden'? '

Du kan finde adskillige typer af variable spændingsreferencer. Forskellig med forskellige indbyggede indstillede spændinger, mens andre med vekselstrømretningspolaritet.

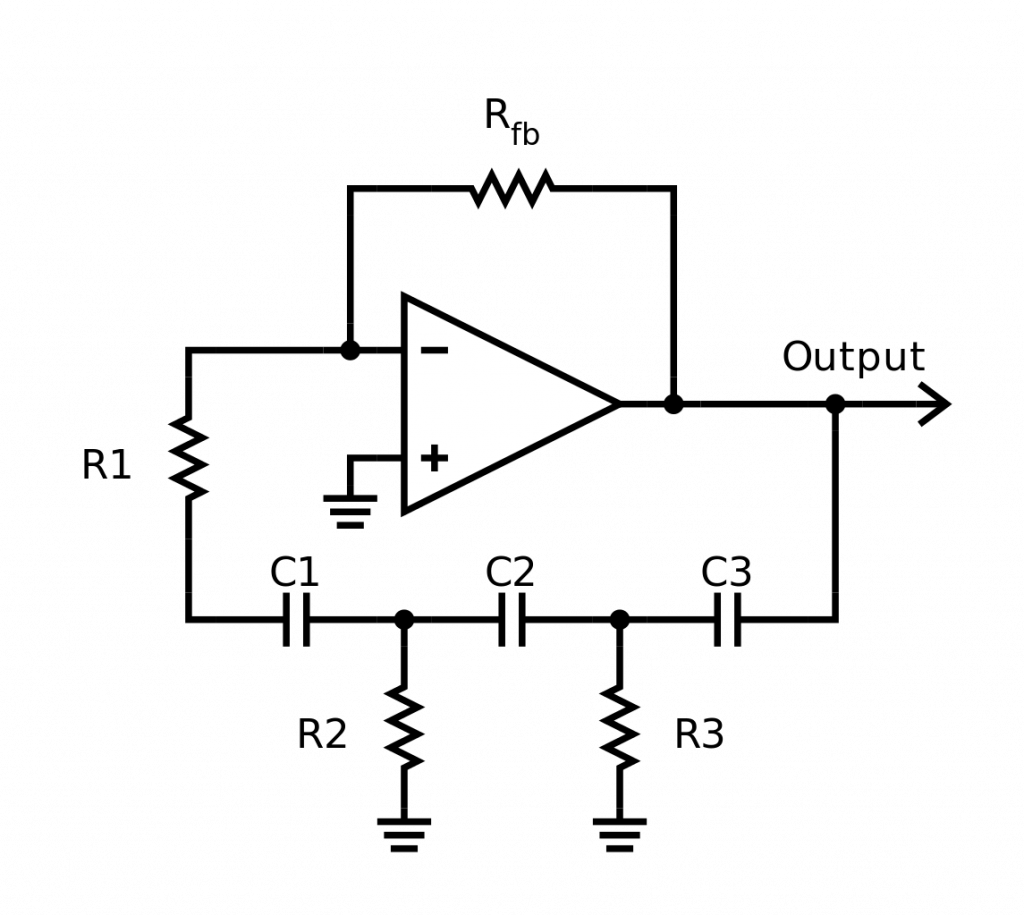

Alle kan identificeres med et par grundlæggende (og ganske betydningsfulde) trin: En temperaturreguleret, nøjagtig båndgabsspændingsreference sammen med en forstærkningsfejlforstærker (inkorporeret som en komparator i det diskuterede kredsløb).

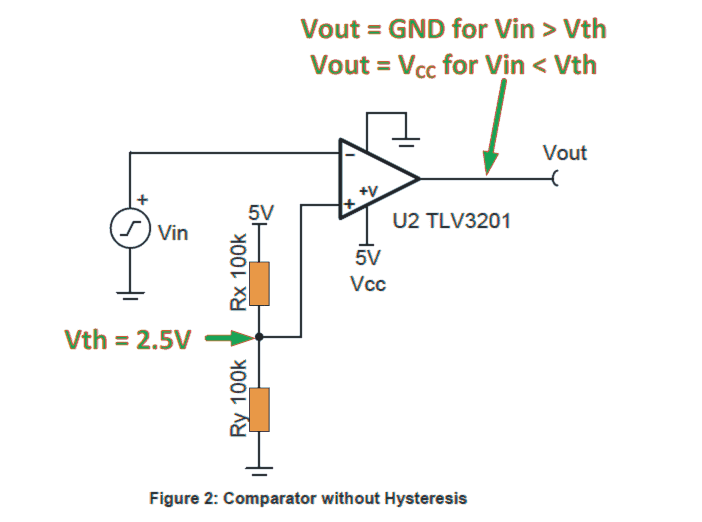

Størstedelen af delene udviser unipoIar-resultater ved at inkorporere en åben samler eller emitter. Figur 2 viser konceptuelt, hvad der kan forventes inde i Texas Instruments LMV431AIMF.

Beregning af tærskelværdien

Indgangsspændingen kontrolleres og styres af LMV431 ved hjælp af spændingsdeler R1 og R2. Kredsløbet, der er beskrevet i figur 1, er konfigureret til at aktivere ved 19,2 V, selvom der kan vælges et vilkårligt niveauskæring, der kan regnes ud ved hjælp af følgende ligninger:

Vtrip = 1,24 x (R1 + R2 / R1)

R2 = R1 (Vtrip / 1.24 - 1)

Hvordan det virker

Outputtet fra LMV431 sænkes ned, så snart den indstillede referencetap registreres til at være over 1,24V. Katoden på en LMV431 er i stand til at bringe ned til et mætningsniveau på ca. 1,2V.

Det nævnte niveau kan være lige nok til at slukke for Q2. Q2 blev overvejende håndplukket for at bære en forhøjet porttærskel (> 1,3V). Det anbefales ikke at bruge en erstatning for Q2 uden at tage dette i betragtning.

Chipens driftsbetingelser for D1, Q2 og Q1 er angivet i tabel 1 for tilstanden, der involverer en 19,2 V punktafskæring.

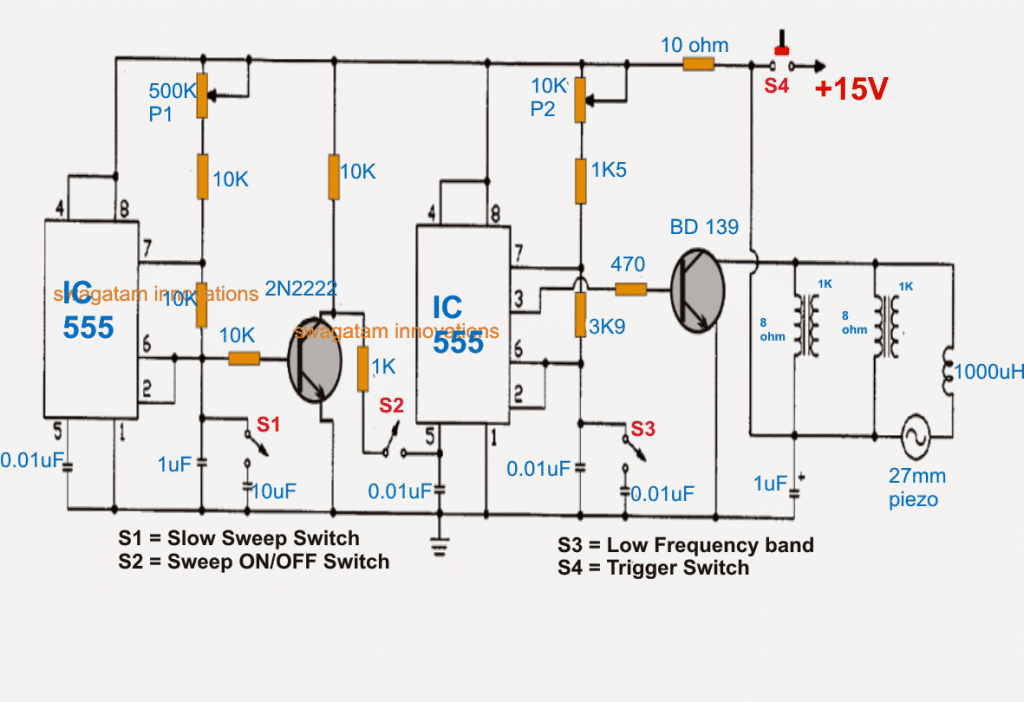

Kredsløbets driftsforhold er beskrevet i figur 3. Niveauskæringen kan forventes at være ca. i området 2.7V til GOV. Under ca. 2,7 V kan kredsløbet ses over til off-situationen.

Årsagen er fraværet af tilstrækkelig indgangsspænding til at niveauere porten op til kildetærsklerne for Q1 og Q2.

Mens det er i slukket tilstand, tilbyder kredsløbet omkring 42 kQ til input (off status hvilende belastning). Zener-dioder D2 og D3 er afgørende for at begrænse overskydende port til kildespændinger som udtrykt ved Q og Q2 (som muligvis ikke får lov til at gå ud over 20 V).

D3 hæmmer ligeledes katoden i D fra at skyde over den specificerede grænse på 35V. Resistor Rd sikrer en kompromitteret bias til Q2, så den kan opfylde Q2's dræningslækage i slukket tilstand.

Det er vigtigt at se kropsdioden i Q, det betyder, at den ikke beskytter belastningen for forkert tilsluttet batteri (modsatte polaritetsindgangsspændinger).

For at være i stand til at beskytte betingelsen for forkert batteripolaritet kan det være tilrådeligt at inkorporere en blokerende diode eller en forstærket alternativ (den ene bag den anden) PFET kan også være påkrævet.

Kredsløbet kan ses tilskrives at aktivere øjeblikkeligt, selvom forholdene ret trægt genoprettes. Kondensator C, udviser hurtig afladning til negativ via LMV431 i en lige overspænding registrerer.

Så snart situationen er normal, holdes genforbindelsen let op af variablerne R3-C1 tidsforsinkelse.

Et betydeligt antal belastninger (der kan være regulatorer) anvender betydelige indgangskondensatorer, som tillader tidsforsinkelse for afskæringskredsløbet at arbejde ved at hæmme den forbigående svinghastighed.

Arbejdsmønsteret for standard transient og den tilgængelige kapacitans bliver ansvarlig, fastlægger den tilsigtede forsinkelsestid.

Lukningsimplementeringen fra det foreslåede overspændingsbeskyttelseskredsløb til køretøjsdump finder sted på cirka tolv sek. De forventede højeste forbigående stigningsperioder er begrænset i et afbalanceret niveau til de nævnte perioder med C (belastning).

Dette kredsløb blev verificeret med en C (belastning) på 1 pF. Større belastning er muligvis prøvet og er okay i betragtning af hurtig stigning, reducerede kildeimpedans-transienter skal være til stede.

Tidligere: Solid-state inverter / strømforsyningskoblingskredsløb ved hjælp af Triacs Næste: Lav dette 3,3V, 5V, 9V SMPS-kredsløb

![Byg et simpelt Buck Converter-kredsløb [Step Down Converter]](https://electronics.jf-parede.pt/img/3-phase-power/D0/build-a-simple-buck-converter-circuit-step-down-converter-1.jpg)