Kontrolenheden er hovedkomponenten i en central processorenhed (CPU) på computere, der kan styre operationerne under udførelsen af et program ved at processoren /computer. Kontrolenhedens hovedfunktion er at hente og udføre instruktioner fra en computers hukommelse. Den modtager inputinstruktion / information fra brugeren og konverterer den til kontrolsignaler , som derefter gives til CPU'en til yderligere udførelse. Det er inkluderet som en del af Von Neumann-arkitekturen udviklet af John Neumann. Det er ansvarligt for at levere timing-signaler og styresignaler og styrer udførelsen af et program af CPU'en. Det er inkluderet som en intern del af CPU'en i moderne computere. Denne artikel beskriver komplette oplysninger om kontrolenheden.

Hvad er kontrolenheden?

Komponenten, der modtager indgangssignalet / informationen / instruktionen fra brugeren og konverterer til styresignaler til udførelse i CPU'en. Den styrer og styrer hovedhukommelsen, aritmetik- og logikkenheden (ALU), input- og outputenheder og er også ansvarlig for de instruktioner, der sendes til en computers CPU. Den henter instruktionerne fra primære hukommelse af en processor og sendt til processorinstruktionsregistret, som indeholder registerindhold.

Kontrolenheds blokdiagram

Styreenheden konverterer indgangen til styresignaler og sendes derefter til processoren og leder udførelsen af et program. De handlinger, der skal udføres, styres af processoren på computeren. Hovedsageligt Central Processing Unit (CPU) og Grafisk behandlingsenhed (GPU) kræver en styreenhed som den interne del. Kontrolenhedens blokdiagram er vist ovenfor.

Komponenter i en kontrolenhed

Komponenterne i denne enhed er instruktioner registre , styresignaler i CPU'en, styresignaler til / fra bussen, kontrolbus, inputflag og ursignaler.

Komponenterne i Hardwired-styreenheden er instruktionsregister (indeholder opcode og adressefelt), timing-enhed, kontroltilstand generator , matrix til styresignalgenerering og instruktionsdekoder.

Komponenterne i den mikroprogrammerede styreenhed er den næste adressegenerator, et kontroladresseregister, kontrolhukommelse og kontroldataregister.

Funktioner

Det kontrolenhedens funktioner inkluderer følgende.

- Det styrer strømmen af datasekvens mellem processoren og andre enheder.

- Det kan fortolke instruktionerne og kontrollere strømmen af data i processoren.

- Det genererer sekvensen af styresignaler fra de modtagne instruktioner eller kommandoer fra instruktionsregistret.

- Det har ansvaret for at kontrollere eksekveringsenhederne såsom ALU, databuffere og registre i CPU'en på en computer.

- Det har evnen til at hente, afkode, håndtere udførelsen og gemme resultater.

- Det kan ikke behandle og gemme dataene

- For at overføre dataene kommunikerer den med input- og outputenhederne og styrer alle enhederne på computeren.

Design af kontrolenhed

Designet af dette kan gøres ved hjælp af to typer styreenhed som inkluderer følgende.

- Hardwire-baseret

- Mikroprogrammeret baseret (enkelt-niveau og to-niveau)

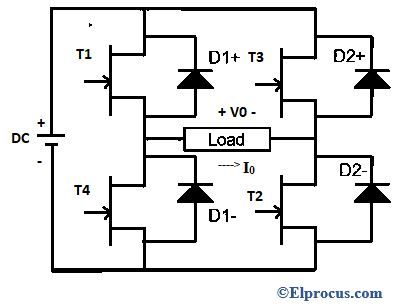

Hardwired kontrolenhed

Det grundlæggende design af en hardwired kontrolenhed er vist ovenfor. I denne type genereres styresignalerne af en særlig hardware logisk kredsløb uden nogen ændring i kredsløbets struktur. I dette kan det genererede signal ikke modificeres til udførelse i processoren.

De grundlæggende data for en opcode (operationskoden for en instruktion sendes til instruktionsdekoderen til afkodning. Instruktionen dekoder er det sæt dekodere, der skal afkode forskellige typer data i opkoden. Dette resulterer i udgangssignaler, der indeholder værdier af aktive signaler, der er givet som input til matrixgeneratoren for at generere styresignaler til udførelse af et program af computerens processor.

Hardwire-baseret kontrolenhed

Matrixgeneratoren tilvejebringer tilstande for kontrolenheden og signalerne ud fra processoren (afbrydelsessignaler). Matrix er bygget som programmerbar logisk matrix . Styresignalerne, der genereres af matrixgeneratoren, gives som input til den næste generatormatrix og kombineres med timingssignalerne fra timingenheden, der indeholder rektangulære mønstre.

For at hente ny instruktion bliver styreenheden til et indledende trin til udførelse af ny instruktion. Styreenheden forbliver i den indledende fase eller det første trin, så længe timing-signaler, indgangssignaler og instruktionstilstande for en computer er uændrede. Ændringen i kontrolenhedens tilstand kan hæves, hvis der er nogen ændring i nogen af de genererede signaler.

Når der opstår et eksternt signal eller afbrydelse, går styreenheden til den næste tilstand og udfører behandlingen af afbrydelsessignalet. Flagene og tilstande bruges til at vælge de ønskede tilstande til at udføre instruktionscyklus.

I den sidste tilstand henter styreenheden den næste instruktion og sender output til programtælleren, derefter til hukommelsesadresseregistret, til bufferregistret og derefter til instruktionsregistret for at læse instruktionen. Endelig, hvis den sidste instruktion (som hentes af styreenheden) er slutinstruktion, går den til processorens driftstilstand og venter, indtil brugeren leder det næste program.

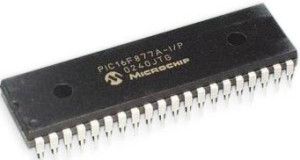

Mikroprogrammeret kontrolenhed

I denne type bruges kontrollageret til at lagre de styresignaler, der er kodet under udførelsen af et program. Styresignalet genereres ikke med det samme og afkodes, fordi mikroprogrammet gemmer adressefeltet i kontrollageret. Hele processen er et enkelt niveau.

Mikrooperationerne udføres til udførelse af mikroinstruktioner i programmet. Blokdiagrammet for den mikroprogrammerede styreenhed er vist ovenfor. Fra diagrammet er adressen på mikroinstruktionen hentet fra kontrolhukommelsesadresseregistret. Al info fra kontrolenheden er permanent gemt i kontrolhukommelsen kaldet ROM.

Mikroprogrammeret baseret kontrolenhed

Mikroinstruktionen fra kontrolhukommelsen holdes af kontrolregistret. Da mikroinstruktionen er i form af kontrolord (indeholder binære kontrolværdier), skal der udføres 1 eller flere mikrooperationer til databehandlingen.

Under udførelsen af mikroinstruktioner beregnede den næste adressegenerator den næste adresse for mikroinstruktionen og sendte derefter til kontroladresseregistret for at læse den næste mikroinstruktion.

Sekvensen af mikrooperationer i et mikroprogram udføres af den næste adressegenerator og fungerer som mikroprogramsekventerer for at få sekvensadressen, dvs. læst fra kontrolhukommelsen.

Verilog-kode til kontrolenheden

Verilog-kode til kontrolenhed er vist nedenfor.

`inkluderer“ prj_definition.v ”

modul CONTROL_UNIT (MEM_DATA, RF_DATA_W, RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2, RF_READ, RF_WRITE, ALU_OP1, ALU_OP2, ALU_OPRN, MEM_ADDR, MEM_READ, MEM_WRITE, RF_DATA_

// Udgangssignaler

// Udgange til registerfil

output [`DATA_INDEX_LIMIT: 0] RF_DATA_W

output [`ADDRESS_INDEX_LIMIT: 0] RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

output RF_READ, RF_WRITE

// Udgange til ALU

output [`DATA_INDEX_LIMIT: 0] ALU_OP1, ALU_OP2

output [`ALU_OPRN_INDEX_LIMIT: 0] ALU_OPRN

// Udgange til hukommelse

output [`ADDRESS_INDEX_LIMIT: 0] MEM_ADDR

output MEM_READ, MEM_WRITE

// Indgangssignaler

input [`DATA_INDEX_LIMIT: 0] RF_DATA_R1, RF_DATA_R2, ALU_RESULT

input ZERO, CLK, RST

// Indgående signal

ud [`DATA_INDEX_LIMIT: 0] MEM_DATA

// Statlige net

wire [2: 0] proc_state

// holder programtællerværdi, gemmer den aktuelle instruktion, stak markørregister

reg MEM_READ, MEM_WRITE

reg MEM_ADDR

reg ALU_OP1, ALU_OP2

reg ALU_OPRN

reg RF_ADDR_W, RF_ADDR_R1, RF_ADDR_R2

reg RF_DATA_W

reg [1: 0] tilstand, næste_stat

PROC_SM state_machine (.STATE (proc_state) ,. CLK (CLK), RST (RST))

altid @ (posedge CLK)

begynde

hvis (RST)

stat<= RST

andet

stat<= next_state

ende

altid @ (tilstand)

begynde

MEM_READ = 1’b0 MEM_WRITE = 1’b0 MEM_ADDR = 1’b0

ALU_OP1 = 1’b0 ALU_OP2 = 1’b0 ALU_OPRN = 1’b0

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0 RF_ADDR_W = 1’b0 RF_DATA_W = 1’b0

sag (tilstand)

`PROC_FETCH: start

next_state = `PROC_DECODE

MEM_READ = 1’b1

RF_ADDR_R1 = 1’b0 RF_ADDR_R2 = 1’b0

RF_ADDR_W = 1'b1

ende

`PROC_DECODE: start

next_state = `PROC_EXE

MEM_ADDR = 1’b1

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

MEM_WRITE = 1’b1

RF_ADDR_R1 = 1’b1 RF_ADDR_R2 = 1’b1

ende

`PROC_EXE: start

next_state = `PROC_MEM

ALU_OP1 = 1’b1 ALU_OP2 = 1’b1 ALU_OPRN = 1’b1

RF_ADDR_R1 = 1'b0

ende

`PROC_MEM: start

næste_stat = `PROC_WB

MEM_READ = 1’b1 MEM_WRITE = 1’b0

ende

`PROC_WB: start

next_state = `PROC_FETCH

MEM_READ = 1’b1 MEM_WRITE = 1’b0

ende

endcase

ende

endmodul

modul PROC_SM (STATE, CLK, RST)

// liste over input

indgang CLK, RST

// liste over output

output [2: 0] STATE

// inputliste

indgang CLK, RST

// outputliste

output STATE

reg [2: 0] TILSTAND

reg [1: 0] tilstand

reg [1: 0] næste_stat

reg PC_REG, INST_REG, SP_REF

`definer PROC_FETCH 3’h0

`definer PROC_DECODE 3’h1

`definer PROC_EXE 3’h2

`definer PROC_MEM 3'h3

`definer PROC_WB 3’h4

// indledning af tilstand

initial

begynde

tilstand = 2'bxx

next_state = `PROC_FETCH

ende

// nulstil signalhåndtering

altid @ (posedge RST)

begynde

tilstand = `PROC_FETCH

next_state = `PROC_FETCH

ende

altid @ (posedge CLK)

begynde

tilstand = næste_stat

ende

altid @ (tilstand)

begynde

hvis (tilstand === `PROC_FETCH)

begynde

next_state = `PROC_DECODE

udskrivningsvejledning (INST_REG)

ende

hvis (tilstand === `PROC_DECODE)

begynde

next_state = `PROC_EXE

ende

hvis (tilstand === `PROC_EXE)

begynde

next_state = `PROC_MEM

udskrivningsvejledning (SP_REF)

ende

hvis (tilstand === `PROC_MEM)

begynde

næste_stat = `PROC_WB

ende

hvis (tilstand === `PROC_WB)

begynde

next_state = `PROC_FETCH

udskrivningsvejledning (PC_REG)

ende

ende

opgave print_instruktion

input [`DATA_INDEX_LIMIT: 0] inst

reg [5: 0] opkode

reg [4: 0] rs

reg [4: 0] rt

reg [4: 0] rd

reg [4: 0] shamt reg [5: 0] funct reg [15: 0] øjeblikkelig reg [25: 0] adresse

begynde

// analyser instruktionen

// R-type

{opcode, rs, rt, rd, shamt, funct} = inst

// I-type

{opcode, rs, rt, umiddelbar} = inst

// J-type

{opcode, adresse} = inst

$ skriv (“@% 6dns -> [0X% 08h]“, $ tid, inst)

sag (opcode) // R-Type

6'h00: start

sag (funktion)

6'h20: $ skriv ('tilføj r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h22: $ skriv ('sub r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h2c: $ skriv (“mul r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6'h24: $ skriv ('og r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6'h25: $ skriv ('eller r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h27: $ skriv (“nor r [% 02d], r [% 02d], r [% 02d]”, rs, rt, rd)

6'h2a: $ skriv ('slt r [% 02d], r [% 02d], r [% 02d]', rs, rt, rd)

6’h00: $ skriv (“sll r [% 02d],% 2d, r [% 02d]”, rs, shamt, rd)

6'h02: $ skriv ('srl r [% 02d], 0X% 02h, r [% 02d]', rs, shamt, rd)

6'h08: $ skriv ('jr r [% 02d]', rs)

standard: $ skriv (“”)

endcase

ende

// I-type

6'h08: $ skriv ('addi r [% 02d], r [% 02d], 0X% 04h', rs, rt, øjeblikkelig)

6'h1d: $ skriv ('muli r [% 02d], r [% 02d], 0X% 04h', rs, rt, øjeblikkelig)

6'h0c: $ skriv ('andi r [% 02d], r [% 02d], 0X% 04h', rs, rt, øjeblikkelig)

6'h0d: $ skriv ('ori r [% 02d], r [% 02d], 0X% 04h', rs, rt, øjeblikkelig)

6’h0f: $ skriv (“lui r [% 02d], 0X% 04h”, rt, øjeblikkelig)

6'h0a: $ skriv ('slti r [% 02d], r [% 02d], 0X% 04h', rs, rt, øjeblikkelig)

6'h04: $ skriv ('beq r [% 02d], r [% 02d], 0X% 04h', rs, rt, øjeblikkelig)

6'h05: $ skriv ('bne r [% 02d], r [% 02d], 0X% 04h', rs, rt, øjeblikkelig)

6'h23: $ skriv ('lw r [% 02d], r [% 02d], 0X% 04h', rs, rt, øjeblikkelig)

6'h2b: $ skriv ('sw r [% 02d], r [% 02d], 0X% 04h', rs, rt, øjeblikkelig)

// J-Type

6'h02: $ skriv ('jmp 0X% 07h', adresse)

6'h03: $ skriv ('jal 0X% 07h', adresse)

6'h1b: $ skriv ('skub')

6'h1c: $ skriv ('pop')

standard: $ skriv (“”)

endcase

$ skriv (“ n”)

ende

slutopgave

slutmodul

Ofte stillede spørgsmål

1). Hvad er en styringsenheds arbejde?

Styringsenhedens arbejde er at styre datastrømmen eller instruktioner til udførelse af processoren af en computer. Det styrer, administrerer og koordinerer hovedhukommelse, ALU, registre, input og outputenheder. Den henter instruktionerne og genererer styresignaler til udførelsen.

2). Hvad er kontrolhukommelsen?

Kontrolhukommelse er normalt RAM eller ROM for at gemme adressen og dataene i kontrolregistret.

3). Hvad er Wilkes kontrolenhed?

Den sekventielle og kombinationskredsløb af den hardwired kontrolenhed erstattes af Wilkes kontrolenheden. Den bruger en lagerenhed til at gemme sekvenserne af instruktionerne i et mikroprogram.

4). Hvad er en hardwired kontrolenhed?

Den kablede styreenhed genererer styresignalerne ved at skifte fra en tilstand til en anden tilstand i hver urpuls uden nogen fysisk ændring i kredsløbet. Dannelsen af styresignaler afhænger af instruktionsregistret, dekoderen og afbrydelsessignaler.

5). Hvad er kontrolhukommelsen?

Oplysningerne om styreenheden eller dataene gemmes midlertidigt eller permanent i kontrolhukommelsen.

Kontrolhukommelse er af to typer. De er Random Access Memory (RAM) og Read-Only Memory (ROM).

Således handler alt om definitionen, komponenter, design, diagram, funktioner og typer kontrolenhed . Her er et spørgsmål til dig, 'Hvad er formålet med kontroladresseregistret?'