Metaloxid-halvledertransistoren eller MOS-transistoren er en grundlæggende byggesten i logiske chips, processorer og moderne digitale hukommelser. Det er en majoritetsbæreranordning, hvor strømmen i en ledende kanal mellem kilden og afløbet moduleres af en påført spænding til porten. Denne MOS-transistor spiller en nøglerolle i forskellige analoge og blandede signal-IC'er. Denne transistor er ret tilpasningsdygtig, så den fungerer som en forstærker, en switch eller en modstand . ikke transistorer er klassificeret i to typer PMOS og NMOS. Så denne artikel diskuterer et overblik over NMOS transistor – fremstilling, kredsløb og arbejde.

Hvad er en NMOS-transistor?

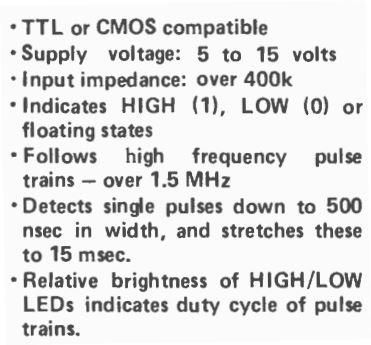

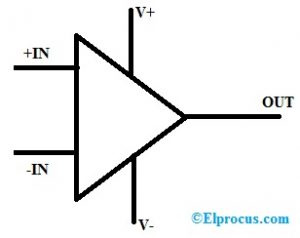

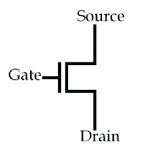

En NMOS-transistor (n-kanal metal-oxid-halvleder) er en type transistor, hvor n-type doteringsmidler anvendes i gate-området. En positiv (+ve) spænding på gateterminalen tænder enheden. Denne transistor bruges hovedsageligt i CMOS (komplementært metal-oxid-halvleder) design & også i logik og hukommelseschips. Sammenlignet med PMOS-transistoren er denne transistor meget hurtigere, så flere transistorer kan placeres på en enkelt chip. NMOS-transistorsymbolet er vist nedenfor.

Hvordan virker NMOS-transistor?

NMOS-transistorens funktion er; når NMOS-transistoren modtager en ikke-ubetydelig spænding, danner den et lukket kredsløb, hvilket betyder, at forbindelsen fra source-terminalen til afløbet fungerer som en ledning. Så strømmen løber fra gateterminalen til kilden. På samme måde, når denne transistor modtager en spænding på ca. 0V, danner den et åbent kredsløb, hvilket betyder, at forbindelsen fra source-terminalen til drænet vil blive brudt, så der strømmer strøm fra gateterminalen til drænet.

Tværsnit af NMOS-transistor

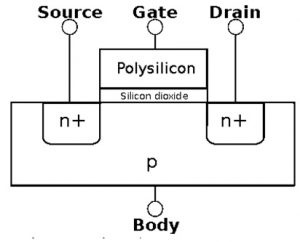

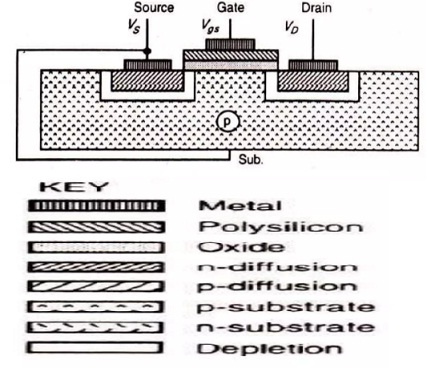

Generelt er en NMOS-transistor simpelthen bygget med en p-type krop af to n-type halvlederområder, der støder op til porten kendt som source & drain. Denne transistor har en kontrollerende gate, der styrer elektronstrømmen mellem source & drain terminalerne.

I denne transistor, da transistorens krop er jordet, er PN-forbindelserne af source & drain mod kroppen omvendt forspændt. Hvis spændingen ved gateterminalen øges, vil et elektrisk felt begynde at stige og tiltrækker frie elektroner til bunden af Si-SiO2-grænsefladen.

Når spændingen er høj nok, vil elektroner vinde op og fylde alle hullerne, og et tyndt område under porten kendt som kanalen vil blive inverteret for at fungere som en n-type halvleder. Dette vil skabe en ledende bane fra kildeterminalen til drænet ved at tillade strømmen, så transistoren vil blive tændt. Hvis gateterminalen er jordet, flyder der ingen strøm i den omvendte forspændingsforbindelse, så transistoren vil blive slukket.

NMOS transistorkredsløb

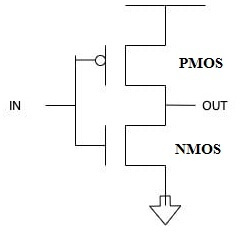

NOT-portdesignet ved hjælp af PMOS- og NMOS-transistorer er vist nedenfor. For at designe en NOT-port skal vi kombinere pMOS- og nMOS-transistorer ved at forbinde en pMOS-transistor til kilden og en nMOS-transistor til jorden. Så kredsløb vil være vores første CMOS transistor eksempel.

NOT-porten er en type logisk port, der genererer et inverteret input som et output. Denne port kaldes også en inverter. Hvis input er '0', vil det inverterede output være '1'.

Når input er nul, så går det til pMOS-transistoren øverst og ned til nMOS-transistoren i bunden. Når inputværdien '0' når pMOS-transistoren, inverteres den til '1'. dermed stoppes forbindelsen til kilden. Så dette vil generere en logisk '1'-værdi, hvis forbindelsen mod afløbet (GND) også er lukket. Vi ved, at nMOS-transistoren ikke inverterer inputværdien, så den tager nulværdien, som den er, og den vil lave et åbent kredsløb til afløbet. Så der genereres en logisk én-værdi for porten.

På samme måde, hvis inputværdien er '1', sendes denne værdi til begge transistorer i ovenstående kredsløb. Når først '1'-værdien modtager pMOS-transistoren, bliver den inverteret til et 'o'. som følge heraf er forbindelsen til kilden åben. Når først nMOS-transistoren modtager '1-værdien, bliver den ikke inverteret. så inputværdien forbliver som én. Når en værdi er modtaget af nMOS-transistoren, lukkes forbindelsen mod GND. Så det vil generere et logisk '0' som et output.

Fremstillingsproces

Der er mange trin involveret i NMOS-transistorfremstillingsprocessen. Den samme proces kan bruges til PMOS- og CMOS-transistorer. Det mest anvendte materiale i denne fremstilling er enten polysilicium eller metal. Trin-for-trin fremstillingsprocessen for NMOS-transistoren diskuteres nedenfor.

Trin 1:

Et tyndt silicium waferlag ændres til P-type materiale ved blot at dope med Boron materiale.

Trin 2:

Et tykt Sio2-lag dyrkes på et komplet p-type substrat

Trin 3:

Nu er overfladen belagt gennem en fotoresist på det tykke Sio2-lag.

Trin 4:

Bagefter udsættes dette lag for UV-lys med en maske, der beskriver de områder, hvor diffusion skal ske sammen med transistorkanaler.

Trin 5:

Disse områder er ætset væk gensidigt med den underliggende Sio2, så waferens overflade er blotlagt inden for vinduet defineret gennem masken.

Trin 6:

Den resterende fotoresist adskilles og tynde Sio2-lag dyrkes 0,1 mikrometer typisk over hele chippens overflade. Dernæst er polysilicium placeret på dette for at danne portstrukturen. En fotoresist placeres på det komplette polysiliciumlag og eksponerer ultraviolet lys i hele masken2.

Trin 7:

Ved at opvarme waferen til den maksimale temperatur opnås diffusioner og passerer gas med ønskede n-type urenheder som fosfor.

Trin 8:

En en-mikrometer tykkelse af siliciumdioxid dyrkes overalt, og fotoresistmateriale er placeret på den. Eksponer det ultraviolette lys (UV) gennem maske3 på de foretrukne områder af gate, kilde- og drænområder er ætset for at lave kontaktskæringerne.

Trin 9:

Nu er et metal som aluminium placeret over dets en mikrometer brede overflade. Endnu en gang dyrkes et fotoresistmateriale over hele metallet og udsættes for UV-lys gennem mask4, som er en ætset form til det obligatoriske sammenkoblingsdesign. Den endelige NMOS-struktur er vist nedenfor.

PMOS vs NMOS transistor

Forskellen mellem PMOS og NMOS transistorer diskuteres nedenfor.

| PMOS transistor | NMOS transistor |

| PMOS transistor står for P-kanal metal-oxid-halvledertransistor. | NMOS transistor står for N-kanal metal-oxid-halvledertransistor. |

| Kilden og afløbet i PMOS-transistorer er simpelthen lavet med n-type halvledere | Kilden og afløbet i NMOS-transistoren er simpelthen lavet med p-type halvledere. |

| Substratet af denne transistor er lavet med en n-type halvleder | Substratet af denne transistor er lavet med p-type halvleder |

| Størstedelen af ladningsbærere i PMOS er huller. | Størstedelen af ladningsbærere i NMOS er elektroner. |

| Sammenlignet med NMOS er PMOS-enheder ikke mindre. | NMOS-enheder er ret mindre sammenlignet med PMOS-enheder. |

| PMOS-enheder kan ikke skiftes hurtigere sammenlignet med NMOS-enheder. | Sammenlignet med PMOS-enheder kan NMOS-enheder skiftes hurtigere. |

| PMOS transistor vil lede, når en lav spænding leveres til porten. | NMOS transistor vil lede, når en højspænding leveres til porten. |

| Disse er mere immune over for støj. | Sammenlignet med PMOS er disse ikke immune over for støj. |

| Tærskelspændingen (Vth) for denne transistor er en negativ størrelse. | Tærskelspændingen (Vth) af denne transistor er en positiv størrelse. |

Egenskaber

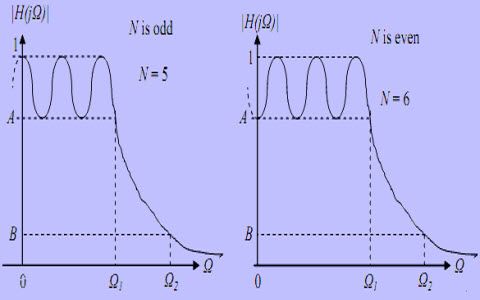

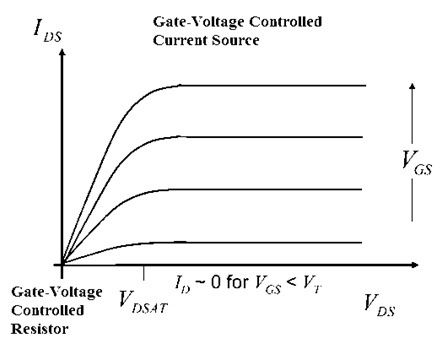

Det I-V karakteristika af NMOS transistoren er vist nedenfor. Spændingen mellem porten og kildeterminalerne 'V GS ' & også mellem kilden og afløbet 'V DS ’. Så kurverne mellem I DS og V DS opnås ved blot at jorde kildens terminal, indstille en initial VGS-værdi og feje V DS fra '0' til den højeste jævnspændingsværdi givet af V DD når du træder V GS værdi fra '0' til V DD . Så for ekstremt lavt V GS , I DS er ekstremt små og vil have en lineær tendens. Når V GS værdi bliver høj, så jeg DS forbedrer & vil have nedenstående afhængighed af V GS & IN DS ;

Hvis V GS er mindre end eller lig med V TH , så er transistoren i OFF tilstand og fungerer som et åbent kredsløb.

Hvis V GS er større end V TH , så er der to driftstilstande.

Hvis V DS er mindre end V GS - IN TH , så arbejder transistoren i lineær tilstand og fungerer som en modstand (R PÅ ).

IDS = u eff C okse W/L [(V GS - IN TH )I DS – ½ V DS ^2]

Hvor,

'µeff' er ladebærerens effektive mobilitet.

'COX' er kapacitansen af gateoxid for hver enhedsareal.

W & L er bredden og længden af kanalen tilsvarende. R PÅ værdi er simpelthen styret af spændingen af porten følger som;

R ON = 1/in n C okse W/L [(V GS - IN TH )I DS – ½ V DS ^2]

Hvis VDS er større end eller lig med V GS - IN TH , så arbejder transistoren inden for mætningstilstanden

jeg DS = u n C okse W/L [(V GS - IN TH )^2 (1+λ V DS ]

I denne region, da jeg DS er højere, så er strømmen minimalt afhængig af V DS værdi, men dens højeste værdi styres blot gennem VGS. Kanallængdemodulationen 'λ' står for stigningen inden for IDS ved en stigning i VDS i transistorer på grund af pinch-off. Denne Pinch-off finder sted, når både V DS og V GS beslutte det elektriske feltmønster tæt på drænområdet, og dermed ændre retningen af de naturlige forsyningsladningsbærere. Denne effekt reducerer den effektive kanals længde og øger I DS . Ideelt set svarer 'λ' til '0', så jeg DS er fuldstændig uafhængig af V DS værdi inden for mætningsområdet.

Det handler altså om en oversigt over en NMOS transistor – fremstilling og kredsløb med arbejde. NMOS transistor spiller en nøglerolle i implementeringen af logiske porte såvel som andre forskellige digitale kredsløb. Dette er et mikroelektronisk kredsløb, der hovedsageligt bruges til design af logiske kredsløb, hukommelseschips og i CMOS-design. De mest populære anvendelser af NMOS-transistorer er switche og spændingsforstærkere. Her er et spørgsmål til dig, hvad er en PMOS-transistor?