Til udførelse af et computerprogram kræver det synkron bearbejdning af mere end en komponent på en computer. For eksempel, Processorer - tilvejebringelse af nødvendige kontroloplysninger, adresser osv., Busser - til at overføre information og data til og fra hukommelse til I / O-enheder ... osv. Den interessante faktor i systemet ville være den måde, det håndterer overførsel af information på mellem processor, hukommelse og I / O-enheder. Normalt kontrollerer processorer hele processen med at overføre data lige fra initiering af overførslen til lagring af data på destinationen. Dette tilfører belastning på processoren, og det meste af tiden forbliver den i den ideelle tilstand, hvilket reducerer systemets effektivitet. For at fremskynde overførslen af data mellem I / O-enheder og hukommelse fungerer DMA-controller som stationsmester. DMA-controller overfører data med minimal indgriben fra processoren.

Hvad er en DMA-controller?

Udtrykket DMA står for direkte hukommelsesadgang. Den hardwareenhed, der bruges til direkte hukommelsesadgang, kaldes DMA-controlleren. DMA controller er en kontrolenhed , en del af I / O-enhedens interface kredsløb , som kan overføre datablokke mellem I / O-enheder og hovedhukommelse med minimal indgriben fra processoren.

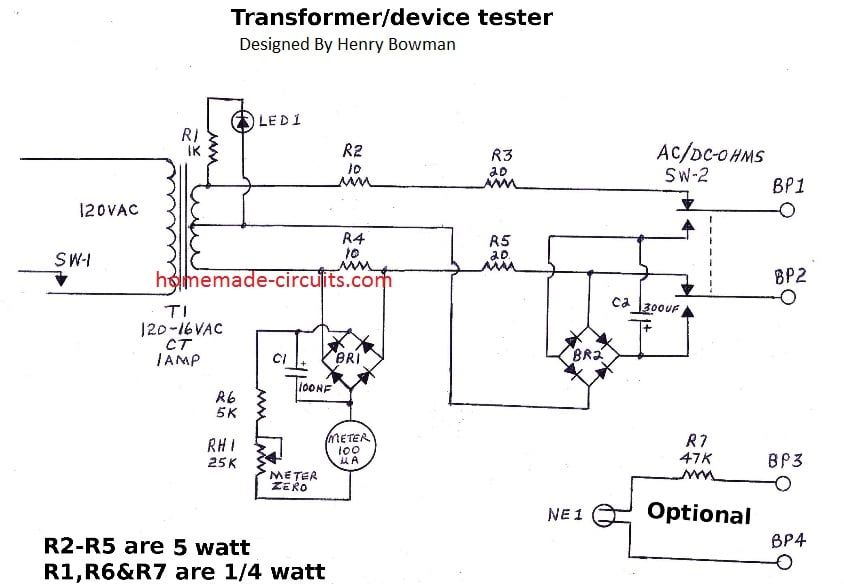

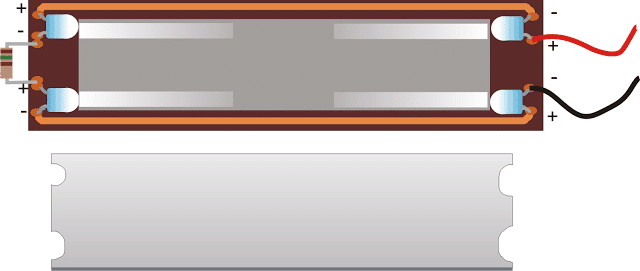

DMA-controller-diagram i computerarkitektur

DMA-controller giver en grænseflade mellem bussen og input-outputenhederne. Selvom det overfører data uden indgriben fra processoren, styres det af processoren. Processoren initierer DMA-controlleren ved at sende startadressen, antallet af ord i datablokken og retningen for overførsel af data, dvs. fra I / O-enheder til hukommelsen eller fra hovedhukommelse til I / O-enheder. Mere end en ekstern enhed kan tilsluttes DMA-controlleren.

DMA i computerarkitektur

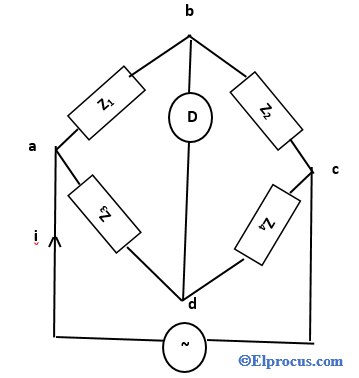

DMA-controller indeholder en adresseenhed til generering af adresser og valg af I / O-enhed til overførsel. Den indeholder også styreenheden og datatællingen til at holde optællinger af antallet af overførte blokke og angive retningen for overførsel af data. Når overførslen er gennemført, informerer DMA processoren ved at hæve en afbrydelse. Det typiske blokdiagram for DMA-controlleren er vist i nedenstående figur.

Typisk blokdiagram for DMA-controller

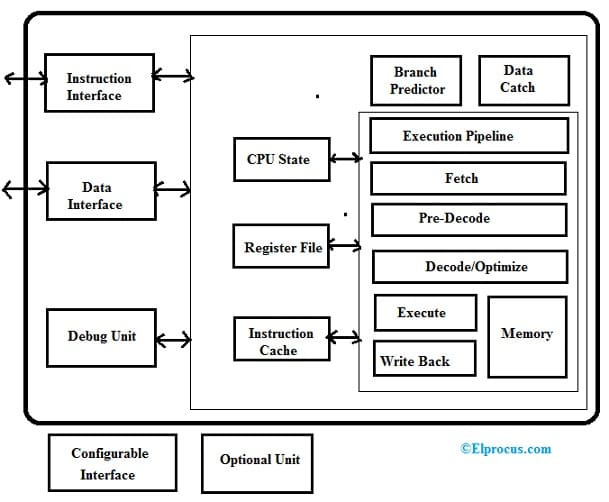

Arbejde med DMA-controller

DMA-controller skal dele bussen med processoren for at foretage dataoverførslen. Enheden, der holder bussen på et givet tidspunkt, kaldes busmaster. Når der skal foretages en overførsel fra I / O-enheden til hukommelsen eller omvendt, stopper processoren udførelsen af det aktuelle program, trinvis programmet tæller, flytter data over stakken og sender derefter et DMA-valgsignal til DMA-controller over adressebussen.

Hvis DMA-controlleren er ledig, anmoder den om styring af bus fra processoren ved at hæve busanmodningssignalet. Processor tildeler bussen til controlleren ved at hæve bustilskudsignalet, nu er DMA-controller busmasteren. Processoren initierer DMA-controlleren ved at sende hukommelsesadresserne, antallet af datablokke, der skal overføres, og retning af dataoverførslen. Efter tildeling af dataoverførselsopgaven til DMA-controlleren, i stedet for ideelt at vente til afslutningen af dataoverførslen, genoptager processoren udførelsen af programmet efter hentning af instruktioner fra stakken.

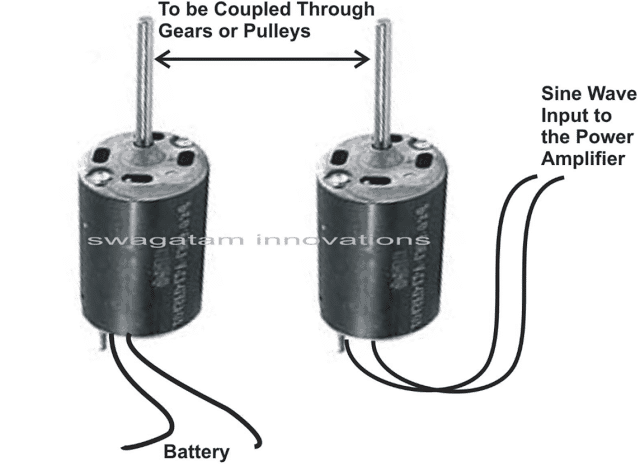

Overførsel af data i computeren med DMA-controller

DMA-controller har nu fuld kontrol over busser og kan interagere direkte med hukommelse og I / O-enheder uafhængigt af CPU. Det foretager dataoverførslen i henhold til kontrolinstruktionerne modtaget af processoren. Efter afslutning af dataoverførsel deaktiverer det busanmodningssignalet, og CPU deaktiverer bustilskudsignalet, hvorved styring af busser flyttes til CPU'en.

Når en I / O-enhed ønsker at starte overførslen, sender den et DMA-anmodningssignal til DMA-controlleren, som controlleren bekræfter for, om den er gratis. Derefter anmoder styreenheden processoren om bussen og hæver busanmodningssignalet. Efter modtagelse af bustilskudsignalet overfører det dataene fra enheden. For n kanaliseret DMA-controller kan antallet af eksterne enheder tilsluttes.

DMA overfører dataene i tre tilstande, som inkluderer følgende.

til) Burst-tilstand : I denne tilstand overleverer DMA kun busser til CPU, når hele dataoverførslen er afsluttet. I mellemtiden, hvis CPU'en kræver bussen, skal den forblive ideel og vente på dataoverførsel.

b) Cyklus stjælingstilstand : I denne tilstand giver DMA kontrol over busser til CPU efter overførsel af hver byte. Den udsender løbende en anmodning om buskontrol, foretager overførsel af en byte og returnerer bussen. Ved denne CPU behøver ikke at vente længe, hvis den har brug for en bus til en højere prioritetsopgave.

c) Gennemsigtig tilstand: Her overfører DMA kun data, når CPU udfører instruktionen, som ikke kræver brug af busser.

8237 DMA-controller

- 8237 har 4 I / O-kanaler sammen med fleksibiliteten til at øge antallet af kanaler.

- Hver kanal kan programmeres individuelt og har en 64k adresse og datafunktion.

- Timingkontrolblokken, Programkommandokontrolblok, Priority Encoder Block er de tre hovedblokke i 8237A.

- Den interne timing og eksterne styresignaler drives af timing-kontrolblokken.

- Forskellige kommandoer, der gives af mikroprocessoren til DMA, afkodes ved hjælp af programkommandokontrolblok.

- Hvilken kanal der skal gives den højeste prioritet, afgøres af prioriteten kodeblok .

8237A har 27 interne registre.

8237A fungerer i to cyklusser - Ideel cyklus og aktiv cyklus, hvor hver cyklus indeholder 7 separate tilstande sammensat af en urperiode hver.

S0- Den første tilstand, hvor controlleren har anmodet om bussen og venter på bekræftelse fra processoren.

S1, S2, S3, S4 kaldes 8237A's arbejdstilstande, hvor den faktiske overførsel af data finder sted. Hvis der er behov for mere tid til overførselsventetilstand, tilføjes SW mellem disse tilstande.

For hukommelse – til- hukommelsesoverførsel skal der foretages læsning fra hukommelse og skrive-til-hukommelse. Otte stater er nødvendige for enkeltoverførsel. De første fire tilstande med abonnement S11, S12, S13, S14 udlæser-fra-hukommelse overførsel, og de næste fire S21, S22, S23, S24 er til skriv-til-hukommelse overførsel.

DMA går i den ideelle tilstand, når ingen kanal anmoder om service og udfører SI-tilstand. SI er en inaktiv tilstand, hvor DMA er inaktiv, indtil den modtager en anmodning. I denne tilstand er DMA i programtilstand, hvor processoren kan programmere DMA.

Når DMA er i den ideelle tilstand og ikke modtager yderligere kanalanmodninger, udsender den et HRQ-signal til processoren og går i aktiv tilstand, hvor den kan starte overførslen af data enten ved burst-tilstand, cyklustjælingstilstand eller gennemsigtig tilstand.

8237 Pin Diagram

8257 DMA-controller

Når den er parret med en enkelt Intel 8212 I / O-portenhed, danner 8257 DMA-controlleren en komplet 4-kanal DMA-controller . Efter modtagelse af en anmodning om overførsel af 8257 controller

- Henter kontrol over systembussen fra processoren.

- Den perifere enhed, der er forbundet med den højeste prioritets kanal, kvitteres.

- De mindst signifikante bits i hukommelsesadressen flyttes over adresselinierne A0-A7 i systembussen.

- Den mest betydningsfulde 8 bits af hukommelsesadressen drives til 8212 I / O-port gennem datalinjer.

- Genererer de relevante kontrolsignaler til overførsel af data mellem perifert udstyr og adresserede hukommelsesplaceringer.

- Når det specificerede antal bytes overføres, informerer controlleren CPU-slutningen af overførslen ved at aktivere terminalantal (TC) -outputtet.

For hver kanal indeholder 8257 to 16-bit-registre - 1) DMA-adresseregister og 2) Terminalantalregister, som skal initialiseres, før en kanal er aktiveret. Adressen på den første hukommelsesplacering, der skal tilgås, indlæses i DMA-adresseregistret. Den nedre orden på 14 bits af den værdi, der er indlæst i terminalregistreringsregistret, angiver antallet af DMA-cyklusser minus en før aktivering af terminaloptællingsoutput. Driftstype for en kanal er angivet med de mest betydningsfulde to bits i terminalregistreringsregistret.

8257 Pin Diagram

Fordele og ulemper ved DMA-controller

Fordele og ulemper ved DMA-controller inkluderer følgende.

Fordele

- DMA fremskynder hukommelsesoperationerne ved at omgå involveringen af CPU'en.

- Arbejdsoverbelastningen på CPU'en falder.

- For hver overførsel kræves kun et par antal urcyklusser

Ulemper

- Problem med cache-kohærens kan ses, når DMA bruges til dataoverførsel.

- Øger prisen på systemet.

DMA ( Direkte hukommelsesadgang ) controller bruges i grafikkort, netværkskort, lydkort osv ... DMA bruges også til overførsel inden for chip i multi-core processorer. DMA fungerer i en af sine tre tilstande og kan reducere processorens belastning betydeligt. I hvilken af DMA-tilstande har du arbejdet med? Hvilken af den tilstand, du anser for at være mere effektiv?