MicroBlaze-processoren blev udviklet i 2002 til at integrere flere komplicerede funktioner for at imødekomme nye såvel som voksende markedsefterspørgsel. Så MicroBlaze-processoren er et væsentligt element i Xilinx Low-End Portfolio for at muliggøre hurtigere systemudvikling, som indeholder Artix®-7 FPGA'er , Spartan®-6, Zynq®-7000 AP SoC'er. Denne processor er ekstremt konfigurerbar, så den kan bruges som en indlejret processor eller mikrocontroller i FPGA'er og også bruges som en co-processor i Zynq-7000 AP SoC'erne baseret på ARM Cortex-A9. Denne artikel giver kort information om MicroBlaze processor – arkitektur og arbejde med applikationer.

Hvad er Microblaze-processor?

Den bløde mikroprocessor, der hovedsageligt er designet til FPGA'er fra Xilinx, er kendt som MicroBlaze-processoren. Denne processor er simpelthen implementeret i den generelle hukommelse og logiske struktur af FPGA'er fra Xilinx. Denne processor ligner DLX-arkitekturen baseret på RISC, og den har et fleksibelt sammenkoblingssystem, så den understøtter forskellige indlejrede applikationer. Hoved-I/O-bussen og AXI-sammenkoblingen af MicroBlaze er en hukommelseskortlagt transaktionsbus med en master-slave-facilitet.

MicroBlaze bruger en dedikeret LMB-bus til at få adgang til lokal hukommelse og giver hurtig on-chip-lagring. Mange dele af denne processor kan brugerkonfigureres som størrelsen af cachen, dybden af pipeline-hukommelsesstyringsenheden, indlejret periferiudstyr og busgrænseflader.

Microblaze funktioner

Det funktioner i Microblaz e inkludere følgende. Det har 32 registre til generelle formål.

- Den har 32-bit instruktionsord inklusive 2 adresseringstilstande og 3 operander.

- Adressebussen er 32-bit.

- Den har en 3-trins rørledning eller en 5-trins rørledning.

- En ALU-blokenhed med en skifter.

- Harvard-arkitekturen inkluderer 32-bit data og adressebus.

- Datainterface & LMB eller lokal hukommelsesbusinstruktion.

- AX14 og AX14 stream grænseflader.

- Flydende komma-enhed og hukommelsesstyringsenhed.

- Den understøtter lockstep.

- Debug & trace interface.

Microbaze arkitektur

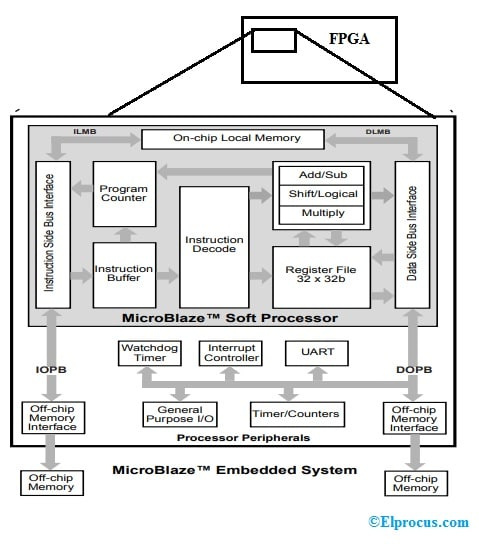

Blokdiagrammet for MicroBlaze-processoren er vist nedenfor. Denne MicroBlaze-processor er ekstremt tilpasselig, og den understøtter over 70 designmuligheder. Denne arkitektur viser permanente hardwarefunktioner såvel som konfigurerbare muligheder som instruktions- eller datacachen, hukommelsesstyringsenheden, flydende punktsenheden osv.

An indlejret system samlet omkring en MicroBlaze-processor omfatter hovedsageligt MicroBlaze Soft Processor Core, On-chip Local Memory, Standard Bus Interconnects og OPB Peripherals (On-chip Peripheral Bus). Et MicroBlaze-processorsystem strækker sig hovedsageligt fra en kerne af processor med en lokal hukommelse til et stort system, der inkluderer flere MicroBlaze processorer , ekstern hukommelse og mange OPB-ydre enheder.

Blød processorkerne

Den bløde processorkerne i MicroBlaze er central for det indlejrede MicroBlaze-system. Dette er en meget hurtig og effektiv 32-bit RISC-processor, som har følgende funktioner.

- Instruktionssættet er ortogonalt.

- Separate data- og instruktionsbusser.

- 32-bit registre til generelle formål.

- Den har en valgfri komplet 32-bit barrel shifter.

- Indbyggede grænseflader til hurtig OCM eller on-chip hukommelse og IBMs industristandard OPB (On-chip Peripheral Bus).

Implementeringer i Virtex-II og efterfølgende enheder understøtter multiplikation af hardware.

On-chip lokal hukommelse

Den synkrone hukommelse er en lokal hukommelse, der hovedsageligt bruges til at tillade on-chip Block RAM.

Standard busforbindelser

Busgrænsefladerne på instruktions- og datasiden inkluderer en grænseflade til lokal hukommelse, som kaldes LMB (Local Memory Bus) og en grænseflade til On-chip Peripheral Bus fra IBM. Så vi kan designe systemer, der nøje holder sig til Harvard-arkitekturen, ellers kan vi, for at dele ressourcer, bruge en enkelt OPB i kombination gennem en bus-arbiter.

Den lokale hukommelsesbus giver sikret en-cyklus entré til on-chip blok RAM. Dette er en meget effektiv, enkel og single-master busprotokol, og den er perfekt til at forbinde hurtig lokal hukommelse. OPB eller On-chip Peripheral Bus er en 32-bit bred multi-master bus, der er perfekt til at forene perifere enheder og udvendig hukommelse til kernen af MicroBlaze processoren.

On-chip perifer bus periferiudstyr

MicroBlaze hardwaresystemet er komplet af OPB periferiudstyr til at give forskellige funktioner som Watchdog Timer eller Timebase, General purpose Timer eller tællere, IC (Interrupt Controller), forskellige controllere som SRAM, Flash Memory, ZBT Memory, BRAM, DDR, SDRAM, UART Lite , SPI, I2C, General purpose I/O, UART 16450/550 og Ethernet 10/100 MAC. Derudover kan vi også tilføje og definere periferiudstyr hovedsageligt til brugerdefinerede funktioner, ellers en grænseflade til et design, der findes i FPGA.

Microblaze instruktionssæt

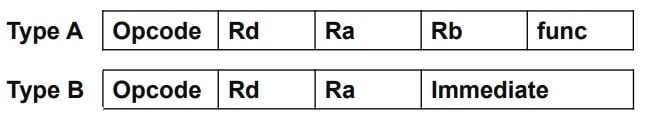

Microblaze instruktionssæt er aritmetik, logik, branch, load/store og andre. Størrelsen på alle instruktionerne er fast. Der kan højst angives 3 registre som operander. Microblaze inkluderer to instruktionsformater Type A og Type B, som er vist nedenfor.

Type A-instruktionsformat bruges hovedsageligt til register-register-instruktioner. Så det inkluderer opcode, enkelt destination og to kilderegistre. Type B-instruktionsformat bruges hovedsageligt til register-umiddelbare instruktioner, som omfatter opcode-, enkeltdestinations- og enkeltkilderegistrene.& en 16-bit umiddelbar værdikilde.

I ovenstående to instruktionsformater er opkoden en operationskode, Rd er et destinationsregister, der er kodet med 5-bit, Ra & Rb er kilderegistre, hvor hver kodet med 5-bit og Immediate er en 16-bit værdi.

Aritmetiske instruktioner

Type A og Type B aritmetiske instruktioner er givet nedenfor.

Type A

|

ADD Rd, Ra, Rb tilføje |

Rd = Ra+Rb, bæreflag påvirket |

|

ADD K Rd, Ra, Rb Tilføj og behold bære |

Rd = Ra+Rb, bæreflag er ikke påvirket |

| RSUB Rd, Ra, Rb Omvendt trække fra |

Rd = R-Rb, bæreflag er ikke påvirket |

Type B

|

ADD I Rd, Ra, Imm tilføje øjeblikkeligt |

Rd = Ra+signExtend32 (Imm) |

|

TILFØJ IK Rd, Ra, Imm tilføje øjeblikkeligt og holde bære |

Rd = Ra+ tegnExtend32 (Imm) |

| RSUBIK Rd, Ra, Imm omvendt trække fra med øjeblikkelig |

Rd = Ra+ tegnExtend32 (Imm) -Ra |

| SRA Rd, Ra aritmetisk skift til højre |

Rd = (Ra>>1) |

Logik instruktioner

Type A og Type B logiske instruktioner er givet nedenfor.

Type A

|

ELLER Rd, Ra, Rb Logisk eller |

Rd = Ra| Rb |

|

OG Rd,Ra,Rb Logisk tilføjelse |

Rd = Ra & Rb |

| XOR Rd, Ra, Rb Logoisk xor |

Rd = Rb ^ Rb |

| ANDN Rd, Ra, Rb Logisk og ikke |

Rd = Ra & (Rb) |

Type B

|

ORI Rd, Ra, Imm logisk ELLER med øjeblikkelig |

Rd = Ra | signExtend32 (Imm) |

| ANDI Rd, Ra, Imm logisk OG med øjeblikkelig |

Rd = Ra & signExtend32 (Imm) |

| XORI Rd, Ra, Imm logoisk XOR med øjeblikkelig |

Rd = Ra ^ tegnExtend32 (Imm) |

| ANDNI Rd, Ra, Imm Logisk OG IKKE med øjeblikkelig |

Rd = Ra & (signExtend32 (Imm)) |

Afdelingsinstruktioner-Ubetinget

Ændre programtællerregistret

| BRID Imm filial øjeblikkelig med øjeblikkelig forsinkelse |

PC = PC+ signExtend32 (Imm) tillade forsinket udførelse af slot |

| BRLID Rd, Imm filial og link øjeblikkeligt med øjeblikkelig forsinkelse (funktionsopkald) |

Rd = PC PC = PC+& signExtend32 (Imm) tillade forsinket udførelse af slot |

| RTSD Ra, Imm tilbage fra subrutine |

PC = Ra + signExtend32 (Imm) tillade forsinket udførelse af slot |

| RTID Ra, Imm tilbage fra afbrydelse |

PC = Ra + signExtend32 (Imm) tillade forsinket udførelse af slot sæt afbrydelsesaktivering i MSR |

Afdelingsinstruktioner-Ubetinget1

Skift programtællerregisteret, når en betingelse er opfyldt

| BEQI Ra, Imm gren hvis lige |

PC = PC+ signExtend32 (Imm) Hvis Ra = = 0 |

| MASH Ra, Imm gren hvis ikke ens |

Rd = PC PC = PC+& signExtend32 (Imm) Hvis Ra! = 0 |

Afdelingsinstruktioner-Ubetinget2

Skift programtællerregisteret, når en betingelse er opfyldt

| BLTI Ra, Imm gren hvis lavere end |

PC = PC+ signExtend32 (Imm) Hvis Ra < 0 |

| BLEI Ra, Imm gren hvis lavere lig end |

Rd = PC PC = PC+& signExtend32 (Imm) Hvis Ra!< = 0 |

| BGTI Ra, Imm gren hvis større end |

PC = PC+ signExtend32 (Imm) Hvis Ra!> 0 |

| BGEI Ra, Imm gren hvis større lig end |

PC = PC+signExtend32 (Imm) Hvis Ra!>= 0 |

Indlæsnings-/opbevaringsvejledning - Type A

| LW Rd, Ra, Rb Indlæs ord |

Adresse = Ra+Rb Rd = *Adresse |

| SW Rd, Ra, Rb Gem ord |

Adresse – Ra+Rb *Adresse = Rd |

Type B

| LWI Rd, Ra, Imn Indlæs ordet med det samme |

Adresse = Ra + signExtend32 (Imm) Rd = *Adresse |

| SW Rd, Ra, Imm Gem ordet med det samme |

Adresse = Ra + signExtend32 (Imm) *Adresse = Rd |

Andre instruktioner

| IMM, Imm umiddelbar |

Udvid Imm for en foregående type B-instruktion til 32-bit. |

| MFS Rd, Sa Flyt fra specialregister |

Rd = Sa Sa- specialformålsregister, kildeoperand

|

| MTS Sd, Ra Flyt til specialregister |

Sd = Ra Sd – specialregister, destinationsoperand |

Registre

Arkitekturen af MicroBlaze-processoren er fuldstændig ortogonal, som inkluderer 32-bit registre til generelle formål og 32-bit registre til specielle formål som programtæller og maskinstatusregister.

Pipeline arkitektur

MicroBlaze bruger en 3-trins pipeline-arkitektur, herunder hente, afkode og komplette stadier. Datavideresendelsen, filialerne og pipeline-standen bestemmes automatisk i hardwaren.

Indlæs eller butiksarkitektur

MicroBlaze understøtter hukommelse i tre datastørrelser 8 bit (Byte), 16 bit (Halfword) og 32 bit (Word). Så hukommelsesadgange er altid tilpasset til datastørrelse. Dette er en Big-Endian-processor, som bruger adressen på Big-Endian-adressen samt mærkningskonventioner, når den først har adgang til hukommelsen.

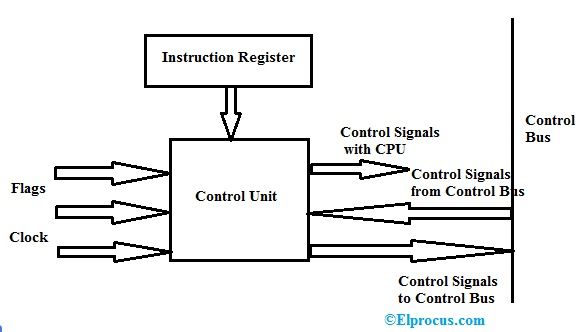

Afbryder

Når først en afbrydelse finder sted, vil denne processor afslutte den nuværende udførelse for at styre afbrydelsesanmodningen gennem forgrening for at afbryde vektoradressen og gemme den instruktionsadresse, der skal udføres. Denne processor vil stoppe fremtidige afbrydelser ved at rydde IE (Interrupt Enable) flaget i MSR (Machine Status Register).

Hvordan virker Microblaze?

MicroBlaze-processoren understøtter 32-bit busbredde, og denne processorkerne er en RISC-baseret motor, der inkluderer en registerfil baseret på 32-bit LUT RAM gennem separate instruktioner til hukommelse og dataadgang.

Denne processor understøtter simpelthen både on-chip BlockRAM og ekstern hukommelse. Svarende til IBM PowerPC; alle perifere enheder bruger den lignende CoreConnect OPB-bus, så; processorens ydre enheder er godt matchet med PowerPC på Virtex-II Pro.

MicroBlaze-processoren leverer fuldstændig fleksibilitet til at vælge kombinationen af hukommelse, periferi- og interfacefunktioner, der vil give dig det præcise system, du har brug for på en enkelt FPGA med færre omkostninger.

Forskel B/W Microblaze vs Risc-V

Det forskel mellem MicroBlaze og RISC v omfatte følgende.

|

Microblaze |

Risc-V |

| Det er en blød mikroprocessorkerne hovedsagelig designet til Xilinx FPGA.

|

RISC-V er en instruktionssætarkitektur, der er forankret i RISC-principper.

|

| Den bruger Harvard RISC-arkitektur. | Den bruger instruktionssætarkitektur. |

| Dets licens er proprietær (Xilinx) | Dens licens er open source. |

| Rørledningens dybde er 3 eller 5. | Rørledningens dybde er 5. |

| Dens ydeevne er 280 DMIPs. | Dens ydeevne er 250 DMIPs. |

| Dens hastighed er 235 MHz. | Dens hastighed er 250 MHz. |

| Den har 1027 LUT'er. | Den har 4125 LUT'er. |

| Implementeringen af den anvendte teknologi er Xilinx FPGA. | Implementeringen af den anvendte teknologi er FPGA/ASIC. |

Microblaze fordele

Det fordelene ved MicroBlaze omfatte følgende.

- Det er økonomisk.

- Det er meget konfigurerbart.

- Dens ydeevne er høj sammenlignet med ARM.

- Det understøttes af et indlejret udviklingskit.

- Det er en blød mikroprocessor kerne.

- For at hjælpe dig med hurtigt at arrangere din applikation inkluderer denne processor tre faste konfigurationer, der er relateret til velkendte processorklasser mikrocontroller, realtid og applikationsprocessor.

Microblaze applikationer

Det anvendelser af MicroBlaze omfatte følgende.

- Denne processor opfylder mange forskellige applikationskrav som industri, bil, medicin og forbruger osv.

- Anvendelserne af MicroBlaze spænder fra simple tilstandsmaskiner baseret på software til komplekse controllere, der bruges i indlejrede applikationer eller internetbaserede apparater.

- Den er optimeret til indlejrede applikationer som industriel kontrol, kontorautomatisering og bilindustrien.

- MicroBlaze er i stand til at kommunikere med et stort sæt periferiudstyr, så det passer til mellemstore applikationer.

- Den bløde natur af denne processor gør den tilpasselig til forskellige applikationer, hvor designere kan udveksle funktioner efter størrelse for at opfylde pris- og ydeevnemål for medicinske, automotive, industrielle og sikkerhedsapplikationer.

Det handler altså om en oversigt over Microblaze processor. Dette er en fuldt udstyret 32-bit programmerbar RISC blød processorkerne. Denne processor opfylder forskellige krav inden for forskellige områder som forbruger-, medicinsk-, industri-, bil- og kommunikationsinfrastrukturmarkeder. Den er ekstremt konfigurerbar, så den bruges som den indlejrede processor eller mikrocontroller i FPGA'er ellers som en co-processor til ARM. Her er et spørgsmål til dig, hvad er FPGA?

![Byg et simpelt Buck Converter-kredsløb [Step Down Converter]](https://electronics.jf-parede.pt/img/3-phase-power/D0/build-a-simple-buck-converter-circuit-step-down-converter-1.jpg)