Udtrykket CMOS står for 'Complementary Metal Oxide Semiconductor'. Dette er en af de mest populære teknologier i computerchipsdesignindustrien, og det bruges bredt i dag til at danne integrerede kredsløb i mange og varierede applikationer. Dagens computerhukommelser, CPU'er og mobiltelefoner bruger denne teknologi på grund af flere vigtige fordele. Denne teknologi bruger både P-kanal og N-kanal halvleder-enheder. En af de mest populære MOSFET-teknologier, der findes i dag, er komplementær MOS- eller CMOS-teknologi. Dette er den dominerende halvlederteknologi til mikroprocessorer, mikrocontrollerchips, minder som RAM, ROM, EEPROM og applikationsspecifikke integrerede kredsløb (ASIC).

Introduktion til MOS-teknologi

I IC-designet er den grundlæggende og mest essentielle komponent transistoren. Så MOSFET er en slags transistor, der bruges i mange applikationer. Dannelsen af denne transistor kan udføres som en sandwich ved at inkludere et halvlederlag, generelt en wafer, et skive fra en enkelt krystal af silicium, et lag af siliciumdioxid og et metallag. Disse lag tillader, at transistorer dannes inden i halvledermaterialet. En god isolator som Sio2 har et tyndt lag med en tykkelse på hundrede molekyler.

Transistorer, som vi bruger polykrystallinsk silicium (poly) i stedet for metal til deres portafsnit. Polysilicon-porten til FET kan udskiftes næsten ved hjælp af metalporte i store IC'er. Undertiden betegnes både polysilicium og metal-FET'er som IGFET'er, hvilket betyder isolerede port-FET'er, fordi Sio2 under porten er en isolator.

CMOS (supplerende metaloxid halvleder)

Det vigtigste fordel af CMOS frem for NMOS og BIPOLAR-teknologi er den meget mindre strømforsyning. I modsætning til NMOS- eller BIPOLAR-kredsløb har et supplerende MOS-kredsløb næsten ingen statisk strømforsyning. Strøm forsvinder kun, hvis kredsløbet faktisk skifter. Dette gør det muligt at integrere flere CMOS-porte på en IC end i NMOS eller bipolar teknologi , hvilket resulterer i meget bedre ydeevne. Supplerende metaloxid halvleder transistor består af P-kanal MOS (PMOS) og N-kanal MOS (NMOS). Se linket for at vide mere om fremstillingsprocessen for CMOS-transistor .

CMOS (supplerende metaloxid halvleder)

NMOS

NMOS er bygget på et p-type substrat med n-type kilde og afløb diffunderet på det. I NMOS er størstedelen af bærere elektroner. Når en høj spænding påføres porten, vil NMOS lede. Tilsvarende, når en lav spænding påføres porten, vil NMOS ikke lede. NMOS anses for at være hurtigere end PMOS, da bærerne i NMOS, som er elektroner, rejser dobbelt så hurtigt som hullerne.

NMOS Transistor

PMOS

P-kanal MOSFET består af P-type kilde og afløb diffunderet på et N-type substrat. De fleste bærere er huller. Når der tilføres en høj spænding til porten, vil PMOS ikke lede. Når en lav spænding påføres porten, vil PMOS lede. PMOS-enhederne er mere immune over for støj end NMOS-enheder.

PMOS Transistor

CMOS-arbejdsprincip

I CMOS-teknologi bruges både N-type og P-type transistorer til at designe logiske funktioner. Det samme signal, der tænder for en transistor af den ene type, bruges til at slukke for en transistor af den anden type. Denne egenskab tillader design af logiske enheder, der kun bruger enkle kontakter uden behov for en pull-up-modstand.

I CMOS logiske porte en samling af n-type MOSFET'er er arrangeret i et pull-down netværk mellem udgangen og lavspændingsforsyningsskinnen (Vss eller ganske ofte jordet). I stedet for belastningsmodstanden for NMOS-logiske porte har CMOS-logiske porte en samling af p-type MOSFET'er i et pull-up-netværk mellem output og højspændingsskinnen (ofte kaldet Vdd).

CMOS ved hjælp af Pull Up & Pull Down

Således, hvis både en p-type og en n-type transistor har deres porte tilsluttet den samme indgang, vil p-typen MOSFET være TIL, når n-typen MOSFET er FRA, og omvendt. Netværkene er arrangeret således, at det ene er TIL og det andet FRA for ethvert inputmønster som vist i nedenstående figur.

CMOS tilbyder relativt høj hastighed, lav effektafledning, høje støjmargener i begge stater og fungerer over en bred vifte af kilde- og indgangsspændinger (forudsat at kildespændingen er fast). For at få en bedre forståelse af det supplerende metaloxid-halvleder-arbejdsprincip er vi desuden nødt til at diskutere kort CMOS-logikporte som forklaret nedenfor.

Hvilke enheder bruger CMOS?

Teknologi som CMOS bruges i forskellige chips som mikrokontroller, mikroprocessorer, SRAM (statisk RAM) og andre digitale logiske kredsløb. Denne teknologi bruges i en bred vifte af analoge kredsløb, som inkluderer datakonvertere, billedsensorer og højt inkorporerede transceivere til flere former for kommunikation.

CMOS inverter

Omformerkredsløbet som vist i nedenstående figur. Det består af PMOS og NMOS FET . Indgangen A fungerer som portspænding for begge transistorer.

NMOS-transistoren har input fra Vss (jord), og PMOS-transistoren har input fra Vdd. Terminal Y sendes ud. Når der gives en højspænding (~ Vdd) ved omformerens indgangsterminal (A), bliver PMOS et åbent kredsløb, og NMOS slukkes, så udgangen trækkes ned til Vss.

CMOS inverter

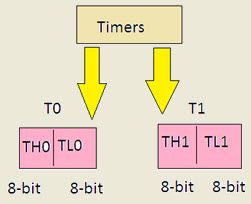

Når en lav spænding ( Nedenstående figur viser en 2-input komplementær MOS NAND gate. Den består af to serier NMOS-transistorer mellem Y og Ground og to parallelle PMOS-transistorer mellem Y og VDD. Hvis enten input A eller B er logisk 0, vil mindst en af NMOS-transistorer være OFF og bryde stien fra Y til jorden. Men mindst en af pMOS-transistorer vil være TIL, hvilket skaber en sti fra Y til VDD. To input NAND Gate Derfor vil output Y være høj. Hvis begge indgange er høje, vil begge nMOS-transistorer være TIL, og begge pMOS-transistorer vil være FRA. Derfor vil output være logisk lavt. Sandhedstabellen for NAND-logikporten angivet i nedenstående tabel. En NOR-port med 2 input er vist i nedenstående figur. NMOS-transistorer er parallelle for at trække udgangen lavt, når begge indgange er høje. PMOS-transistorer er i serie for at trække udgangen højt, når begge indgange er lave, som angivet i nedenstående tabel. Outputtet efterlades aldrig flydende. To-input NOR-port Sandhedstabellen for NOR-logikporten angivet i nedenstående tabel. Fremstillingen af CMOS-transistorer kan udføres på siliciumpladen. Waferens diameter varierer fra 20 mm til 300 mm. I dette er litografiprocessen den samme som trykpressen. På hvert trin kan forskellige materialer deponeres, ætses på anden måde med mønster. Denne proces er meget enkel at forstå ved at se wafers top såvel som tværsnit inden for en forenklet samlingsmetode. Fremstillingen af CMOS kan opnås ved hjælp af tre teknologier, nemlig N-brønd pt P-brønd, Twin brønd, en SOI (Silicon on Insulator). Se dette link for at vide mere om CMOS fabrikation . Den typiske levetid for et CMOS-batteri er cirka 10 år. Men dette kan ændre sig baseret på brugen og omgivelserne, hvor som helst pc'en bor. Når CMOS-batteriet svigter, kan computeren ikke opretholde den nøjagtige tid og dato på computeren, når den er slukket. Når computeren f.eks. Er tændt, kan du muligvis se klokkeslæt og dato som kl. 12.00 og 1. januar 1990. Denne fejl angiver, at CMOS-batteriet mislykkes. De vigtigste egenskaber ved CMOS er lav statisk strømforbrug, enorm støjimmunitet. Når den enkelte transistor fra MOSFET-transistorparet er slukket, bruger seriekombinationen betydelig strøm under hele skiftet blandt de to, der er angivet som ON & OFF. Som et resultat genererer disse enheder ikke spildvarme sammenlignet med andre typer logiske kredsløb såsom TTL eller NMOS-logik, som normalt bruger en vis stående strøm, selvom de ikke ændrer deres tilstand. Disse CMOS-egenskaber giver mulighed for at integrere logiske funktioner med høj densitet på et integreret kredsløb. På grund af dette er CMOS blevet den hyppigst anvendte teknologi, der skal udføres inden for VLSI-chips. Udtrykket MOS er en henvisning til MOSFETs fysiske struktur, som inkluderer en elektrode med en metalport, der er placeret på toppen af en oxidisolator af halvledermateriale. Et materiale som aluminium bruges kun én gang, men materialet er nu polysilicium. Designet af andre metalporte kan udføres ved hjælp af et comeback gennem ankomsten af høj-κ dielektriske materialer inden for processen med CMOS-processen. Billedsensorer som den ladningskoblede enhed (CCD) og komplementær metaloxid-halvleder (CMOS) er to forskellige slags teknologier. Disse bruges til at tage billedet digitalt. Hver billedsensor har sine fordele, ulemper og applikationer. Den største forskel mellem CCD og CMOS er måden at fange rammen på. En ladningskoblet enhed som CCD bruger en global lukker, mens CMOS bruger en rullende lukker. Disse to billedsensorer ændrer opladningen fra lys til elektrisk og behandler den til elektroniske signaler. Fremstillingsprocessen, der anvendes i CCD'er, er speciel til at danne kapacitet til at flytte opladning over IC uden ændringer. Så denne fremstillingsproces kan føre til sensorer af ekstremt høj kvalitet om lysfølsomhed og troskab. I modsætning hertil bruger CMOS-chips faste fremstillingsprocedurer til at designe chippen, og en lignende proces kan også bruges til fremstilling af mikroprocessorer. På grund af forskellene i fremstillingen er der nogle klare forskelle mellem sensorerne som CCD 7 CMOS. CCD-sensorer fanger billederne med mindre støj og enorm kvalitet, mens CMOS-sensorer normalt er mere udsat for støj. Normalt bruger CMOS mindre strøm, mens CCD bruger masser af strøm som mere end 100 gange til CMOS-sensoren. Fremstillingen af CMOS-chips kan udføres på enhver typisk Si-produktionslinje, fordi de har tendens til at være meget billige sammenlignet med CCD'er. CCD-sensorer er mere modne, fordi de masseproduceres i lang tid. Både CMOS- og CCD-kameraerne afhænger af effekten af fotoelektrisk for at frembringe det elektriske signal fra lyset Baseret på ovenstående forskelle bruges CCD'er i kameraer til at målrette billeder af høj kvalitet gennem mange pixels og enestående lysfølsomhed. Normalt har CMOS-sensorer mindre opløsning, kvalitet og følsomhed. En låsning kan defineres som når kortslutningen opstår mellem de to terminaler som strøm og jord, så der kan genereres høj strøm og IC kan blive beskadiget. I CMOS er latch-up forekomsten af lavimpedansspor blandt power rail & jordskinnen på grund af kommunikationen mellem de to transistorer som parasitisk PNP og NPN transistorer . I CMOS-kredsløbet er de to transistorer som PNP & NPN forbundet til to forsyningsskinner som VDD & GND. Beskyttelsen af disse transistorer kan ske gennem modstande. I en latch-up transmission strømmer strømmen fra VDD til GND lige gennem de to transistorer, så der kan opstå kortslutning, og derved strømmer ekstrem strøm fra VDD til jordterminalen. Der er forskellige metoder til forebyggelse af låsen I låseforebyggelse kan høj modstand placeres i sporet for at stoppe strømmen af strøm gennem hele forsyningen og for at gøre β1 * β2 under 1 ved hjælp af følgende metoder. Strukturen af parasitisk SCR vil blive næbbet i omgivelserne af transistorer som PMOS og NMOS gennem et isolerende oxidlag. Teknologien til låsebeskyttelse slukker enheden, når der er lagt mærke til lås-op. Testtjenesterne for latch-up kan udføres af mange leverandører på markedet. Denne test kan udføres ved en række forsøg på at aktivere strukturen af SCR i CMOS IC, mens de relaterede ben kontrolleres, når overstrøm strømmer gennem den. Det tilrådes at få de første prøver fra det eksperimentelle parti og sende dem til et testlaboratorium for Latch-up. Dette laboratorium anvender den bedst mulige strømforsyning og leverer derefter strømforsyningen til chipens indgange og udgange, hver gang der forekommer en Latch-up gennem overvågning af den aktuelle forsyning. Fordelene ved CMOS inkluderer følgende. De vigtigste fordele ved CMOS frem for TTL er god støjmargen såvel som mindre strømforbrug. Dette skyldes ingen lige ledende bane fra VDD til GND, faldtider baseret på inputforholdene, så transmissionen af det digitale signal bliver let og billigt gennem CMOS-chips. CMOS bruges til at forklare mængden af hukommelse på bundkortet på computeren, der gemmes i BIOS-indstillingerne. Disse indstillinger inkluderer hovedsageligt dato, klokkeslæt og indstillinger for hardware Outputs, hvis CMOS kører aktivt på begge måder Ulemperne ved CMOS inkluderer følgende. Supplerende MOS-processer blev implementeret i vid udstrækning og har i grunden erstattet NMOS- og bipolære processer til næsten alle digitale logiske applikationer. CMOS-teknologi er blevet brugt til følgende digitale IC-design. Således er den CMOS transistor er meget berømt fordi de bruger elektrisk strøm effektivt. De bruger ikke strømforsyning, når de skifter fra en tilstand til en anden. De gratis halvledere arbejder også gensidigt for at stoppe o / p-spændingen. Resultatet er et design med lav effekt, der giver mindre varme, på grund af denne grund har disse transistorer ændret andre tidligere designs som CCD'er inden for kamerasensorer og brugt i de fleste af de nuværende processorer. Hukommelsen til CMOS i en computer er en slags ikke-flygtigt RAM, der gemmer BIOS-indstillinger og oplysninger om tid og dato. Jeg tror, at du har fået en bedre forståelse af dette koncept. Desuden er spørgsmål vedrørende dette koncept eller elektronikprojekter , bedes du give dine værdifulde forslag ved at kommentere i kommentarfeltet nedenfor. Her er et spørgsmål til dig, hvorfor CMOS er at foretrække frem for NMOS? INDGANG LOGIKINDGANG PRODUKTION LOGISK UDGANG 0 v 0 Vdd 1 Vdd 1 0 v 0 CMOS NAND-port

TIL B Pull-Down-netværk Pull-up netværk UDGANG Y 0 0 AF PÅ 1 0 1 AF PÅ 1 1 0 AF PÅ 1 1 1 PÅ AF 0 CMOS NOR-port

TIL B Y 0 0 1 0 1 0 1 0 0 1 1 0 CMOS fabrikation

En levetid på CMOS-batteri

Fejlsymptomer på CMOS-batteri

CMOS-egenskaber

CCD mod CMOS

I nogle applikationer forbedres CMOS-sensorer for nylig til det punkt, hvor de når næsten lige med CCD-enheder. Generelt er CMOS-kameraer ikke dyre, og de har en lang levetid på batteriet.Latch-Up i CMOS

Fordele

TTL er et digitalt logisk kredsløb, hvor bipolære transistorer arbejder på jævnstrømsimpulser. Flere transistorlogiske porte består normalt af en enkelt IC.Ulemper

CMOS-applikationer