Multiplikatorer bruges i en bred vifte af digital signalbehandling og andre applikationer. På grund af fremskridt inden for den nuværende teknologi har mange forskere primært koncentreret sig om designfaktorerne for bedre ydeevne. Nogle af designmålene er - høj hastighed, nøjagtighed, lavt strømforbrug, regelmæssigheden af layoutet, mindre areal. DSP-processor har forskellige beregningsblokke, som multiplexere, adders, MAC . Driftshastigheden og udførelsen af disse blokke er avanceret sammenlignet med tidligere versioner. Multiplikatorers udførelseshastighed afhænger af to faktorer, halvlederteknologi og multiplikatorarkitektur. Adders er den grundlæggende byggesten for digitale multiplexere, hvor vi udfører en række gentagne tilføjelser for at fremskynde multiplikatoroperationen, skal adderens driftshastighed øges. Der er mange applikationer til digital signalbehandling, hvor kritisk forsinkelsessti og processorens ydeevne ligger i multiplikatoren. Der er forskellige typer multiplikatorer, blandt hvilke 4 × 4 array multiplikatorer er en avanceret, som er beskrevet i denne artikel.

Multiplikationsordninger i 4 × 4 Array Multiplier

Der er to typer multiplikationsordninger, de er

Seriel multiplikation (Shift – Add): Den serielle multiplikationsoperation kan løses ved at finde delprodukter og derefter tilføje delprodukter sammen. Implementeringerne er primitive med enkel arkitektur

Parallel multiplikation: Parallelle produkter genereres samtidigt i parallel multiplikation og en højtydende maskine Parallelle implementeringer anvendes, ventetid minimeres.

Multiplikationsalgoritme

Multiplikationsprocessen har tre hovedtrin:

- Delvis produktgenerering

- Delvis produktreduktion

- Endelig tilføjelse.

Den almindelige multiplikationsmetode er 'tilføj og skift' -algoritmen. Multiplikationsalgoritmen for en N-bit multiplikator er vist nedenfor.

4-ved-4-multiplikation

4 - ved - 4 - multiplikation 1

eksempel-2

Delvise produkter genereres ved hjælp af AND-porte, hvor

- Multiplikand = N-bits

- Multiplikator = M-bits

- delprodukter = N * M.

Multiplikationen af to 8-bit tal, som genererer 16-bit produktet.

Ligningen for tilsætning er

P (m + n) = A (m). B (n) = i = 0 m-1∑ j = 0n-1∑ ai bj 2i + j ……. 1

A, B = 8 bits

Trin i multiplikation

Følgende er trinene for enhver multiplikation

- Hvis LSB for multiplikator er '1'. tilføj derefter multiplikatoren til en akkumulatormultiplikatorbit forskydes en bit til højre og multiplikandbit forskydes en bit til venstre.

- Stop, når alle bits i multiplikatoren er nul.

- Der anvendes mindre hardware, hvis der tilføjes delprodukter serielt. Vi kan tilføje alle PP med en parallel multiplikator. Det er dog muligt at anvende kompressionsteknik, antallet af delprodukter kan reduceres inden tilsætning udføres.

Forskellige typer multiplikatorer

De forskellige typer multiplikatorer er,

Kabine Multiplikator

Funktionen af kabinenes multiplikator er at multiplicere 2 underskrevne binære tal, som er repræsenteret i 2's komplement form. Fordelene ved kabine-multiplikatorer er minimumskompleks, multiplikation fremskyndes. Ulemperne ved kabine-multiplikatorer er strømforbruget er højt.

Kombinationsmultiplikator

Kombinationsmultiplikatoren udfører multiplikation af to usignerede binære tal. Fordelen ved en kombinationsmultiplikator er, at den let kan generere mellemprodukter. Den største ulempe ved kombinationsmultiplikatoren er, at den optager store områder.

Sekventiel multiplikator

Multiplikation opdeles i sekvensen af trin, hvor det genererede delprodukt føjes til akkumulatorens delvise sum nu flyttes til det næste trin. Fordelen ved dette er, at det optager mindre areal. Ulempen ved en sekventiel multiplikator er, at det er en langsom proces.

Wallace-træmultiplikator

Det reducerer antallet af delprodukter og bruger carry select-addder til tilføjelsen af delprodukter. Fordelen ved Wallace-træmultiplikatoren er et design med høj hastighed og medium kompleks. Den største ulempe ved Wallace-træmultiplikator er layoutdesignet er uregelmæssigt og optager et større område.

Arraymultiplikator

Multiplikatorkredsløbet er baseret på add shift-algoritmen. Den største fordel ved array-multiplikatoren er, at den er enkel i design og regelmæssig i form. Ulempen ved en array-multiplikator er forsinkelsen er høj og højt strømforbrug.

Skift og tilføj multiplikator

Det svarer til den normale multiplikationsproces, som vi gør i matematik, fra array-multiplikator-flowchat, hvor X = Multiplikand Y = Multiplikator A = Akkumulator, Q = Kvotient. For det første kontrolleres Q, om det er 1 eller nej, hvis det er 1, så tilføj A og B, og skift A_Q aritmetisk til højre, ellers hvis det ikke er 1 direkte skift A_Q aritmetisk højre og formindsk N med 1, i næste trin skal du kontrollere, om N er 0 eller nej. Hvis N ikke 0 gentages fra Q = 0, skal du afslutte processen.

skift-og-tilføj-multiplikator

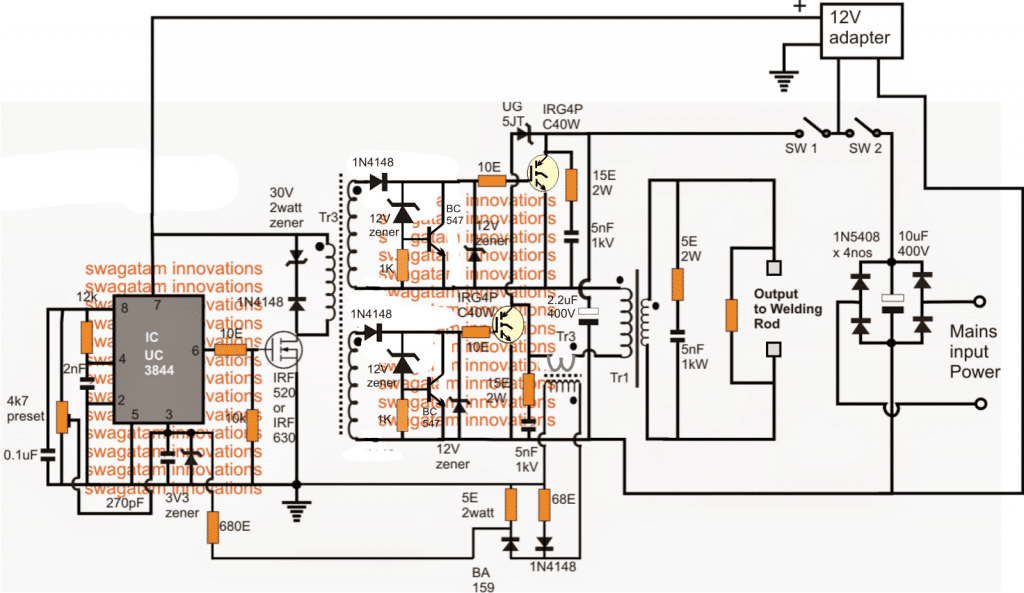

Konstruktion og bearbejdning af en 4 × 4 Array Multiplier

Matrixmultiplikatorens designstruktur er regelmæssig, den er baseret på add shift algoritmeprincippet.

Delprodukt = multiplikand * multiplikatorbit ………. (2)

hvor OG-porte bruges til produktet, foretages opsummeringen ved hjælp af Full Adders og Half Adders, hvor delproduktet forskydes i henhold til deres bitordrer. I en n * n-array-multiplikator beregner n * n OG-porte delprodukterne, og tilføjelsen af delprodukter kan udføres ved hjælp af n * (n - 2) Fuld adders og n Half adders. Den viste 4 × 4 array-multiplikator har 8 indgange og 8 udgange

4-by-4-array-multiplikator

Byggeklodser med 4 × 4 Arraymultiplikator

En fuld optager har tre indgangslinjer og to udgangslinjer, hvor vi bruger dette som en grundlæggende byggesten for en matrixmultiplikator. Følgende er eksemplet på en 4 × 4 array multiplikator. Den venstre bit er LSB bit af delprodukt.

adder-blok-diagram

array-multiplikator-blok-diagram

Den yderste bit er MSB bit af delprodukt. Delprodukterne forskydes nu mod venstre side ved multiplikation, og de tilføjes for at få det endelige produkt. Denne proces gentages, indtil ingen to delprodukter går ud for tilsætning.

4-ved-4-multiplikation-1

logik-diagram-af-4-ved-4 - array - multiplikator

Hvor a0, a1, a2, a3 og b0, b1, b2, b3 er multiplikand og multiplikator, er summering af alle produkter delprodukter. Resultatet af summen af delproduktet er et produkt.

For en 4 × 4 Arraymultiplikator har den brug for 16 AND-porte, 4 Half Adders (HA'er), 8 Full Adders (FA'er). I alt 12 tilføjere.

Fordele ved 4 × 4 Array Multiplier

Fordelene ved array multiplikator er,

- Minimum kompleksitet

- Let skalerbar

- Let rørledning

- Regelmæssig form, let at placere og rute

Ulemper ved 4 × 4 Array Multiplier

Ulemperne ved array-multiplikator er som følger:

- Højt strømforbrug

- Mere digitale porte hvilket resulterer i store områder.

Anvendelser af 4 × 4 Array Multiplier

Anvendelserne af array-multiplikator er angivet,

- Arraymultiplikator bruges til at udføre aritmetisk operation , som filtrering, Fourier-transformation, billedkodning.

- Hurtig drift.

Således handler det hele om 4 × 4 array multiplikator som er en avanceret multiplikator baseret på add and shift-princippet, kan ydelsen let øges ved hjælp af rørledningsteknikken med enkel konstruktion, selvom den bruger flere logiske porte, hvor den kan implementeres ved hjælp af Verilog. Her er et spørgsmål, 'Hvor mange logiske porte kræves for at designe 3 * 3 array multiplikator?'.