Tidligere designede logiske kredsløb kan gøres ved hjælp af SSI (lille skala integration) komponenter som logiske porte, multiplexere , de-multiplexere, FF'er osv. Men nu kan en PLD erstatte alle disse SSI-komponenter. Så dette er grunden til at mindske SSI-branchen sammenlignet med PLD, og disse bruges i flere applikationer. Det programmerbar logisk enhed eller PLD er en slags chip, der bruges til at implementere det logiske kredsløb. Det inkluderer et sæt logiske kredsløbselementer, der kan ændres på flere måder. En PLD ligner en sort boks, der består af programmerbare kontakter samt logiske porte. Omskifternes hovedfunktion er at lade de logiske porte i PLD gensidigt associeres til at udføre logiske kredsløb. PLD'er klassificeres i forskellige typer såsom SPLD-simpel PLD ( PLA & PAL ), CPLD-kompleks PLD , FPGA- feltprogrammerbare portarrays . Denne artikel diskuterer, hvad der er et PAL og PLA, design og deres forskelle.

Hvad er PAL og PLA?

Begge Programmerbar Array Logic og Programmerbar logikarray er typer PLD'er (programmerbare logiske enheder), og disse bruges hovedsageligt til at designe kombinationslogik indbyrdes ved hjælp af sekventiel logik. Hovedforskellen mellem disse to er, at PAL kan designes med en samling af AND-porte og fast samling af ELLER-porte, mens PLA kan designes med et programmerbart array af AND, selvom en fast samling af OR-port. En programmerbar logisk enhed tilbyder en enkel såvel som fleksibel logisk kredsløbskonstruktion.

Programmerbar Array Logic

Tidligere til programmerbare logiske enheder, kombinationslogiske kredsløb kan designes med multiplexere, og disse kredsløb var stive såvel som sammensatte, så udvikles PLD'er. Den oprindelige programmerbare logiske enhed var ROM, men den lykkedes ikke på grund af hardware-spildsproblemer samt eksponentiel vækstforbedring i hver hardware-applikation. For at løse dette problem blev PAL og PLA brugt. Disse to er programmerbare og bruger effektivt hardware.

Programmerbar logikarray

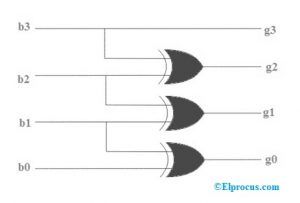

Design af programmerbar matrixlogik (PAL)

Det definition af begrebet PAL eller Programmable Array Logic er en type PLD, der er kendt som Programmable Logic Device circuit, og arbejdet med denne PAL er den samme som PLA. Designet af den programmerbare array-logik kan udføres med faste ELLER porte såvel som programmerbare OG-porte. Ved at bruge dette kan vi implementere to nemme funktioner, hvor associerede OG porte til hver ELLER port angiver det højeste antal produktbetingelser, der kan produceres i form af SOP (sum af produkt) af en nøjagtig funktion.

Da de logiske porte som OG konstant er forbundet med ELLER-porte, og det indikerer, at det producerede produktudtryk ikke distribueres med outputfunktionerne. Den største opfattelse bag PLD-udvikling er at fremstille en sammensat boolsk logik på en enkelt chip ved at fjerne den defekte ledning, undgå det logiske design samt reducere strømforbruget.

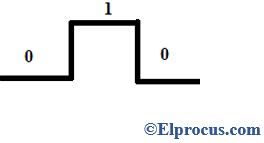

Eksempel på PAL

Gennemfør følgende Boolsk udtryk med hjælp fra programmerbar matrixlogik (PAL)

X = AB + AC '

Y = AB '+ BC'

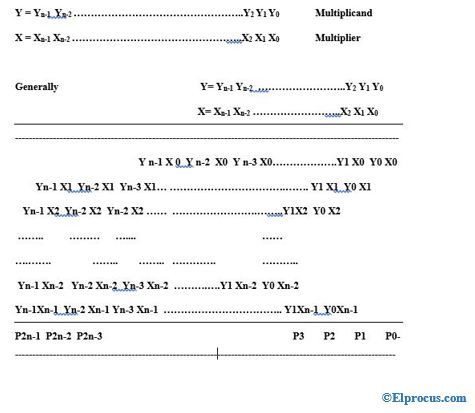

Ovenstående givet to Boolske funktioner er i form af SOP (sum af produkter) . Produktbetegnelserne i de boolske udtryk er X & Y, og et produktudtryk, der er AC, er almindeligt i hver ligning. Så de samlede nødvendige logiske porte til at generere de ovennævnte to ligninger er OG porte-4 ELLER programmerbare porte-2. Det tilsvarende PAL-logikdiagram er vist nedenfor.

PAL Logic Circuit

AND-porte, der er programmerbare, har ret til indgang for normale såvel som supplerede variable indgange. I ovenstående logikdiagram er de tilgængelige indgange for hver AND-port A, A ’, B, B’, C, C ’. Så for at generere et enkelt produktudtryk med hver AND-gate kræves programmet.

Alle produktbetingelser kan fås ved indgangene til hver ELLER-port. Her kan de programmerbare forbindelser på logikporten betegnes med symbolet 'X'.

Her er ELLER gateindgangene faste. Således er de krævede produktbetingelser knyttet til hver ELLER gate-input. Som et resultat vil disse porte generere bestemte boolske ligninger. Det '.' Symbolet repræsenterer permanente forbindelser.

Design af programmerbar logikarray (PLA)

Definitionen af udtrykket PLA præsenterer den boolske funktion i form af en sum af produktet (SOP). Designet af dette programmerbare logiske array kan udføres ved hjælp af de logiske porte som AND, OR og IKKE ved at fremstille på chippen, hvilket gør enhver input såvel som dens kompliment tilgængelig mod hver AND-gate.

Hver OG-portens output er forbundet til hver ELLER-port. Endelig genererer output fra OR-porten output fra chippen. Det er således, hvordan en passende tilknytning er færdig til at bruge udtryk for produktets sum. I det programmerbare logiske array er forbindelserne mellem logiske porte som AND & OR programmerbare. PLA er dyrt og svært at sammenligne med PAL. PAL bruger to forskellige udviklede metoder, der kan bruges til et programmerbart logisk array til forbedring af ubesværet ved programmering. I denne form for metode kan enhver forbindelse udføres ved hjælp af en sikring på hvert skæringspunkt, uanset hvor de unødvendige forbindelser kan løsnes ved, at sikringen blæser. Den sidste teknik involverer oprettelse af forbindelse, mens fremstillingsprocessen ved hjælp af det passende dæksel tilbydes til den nøjagtige samtrafikmodel.

Eksempel på PLA

Implementér følgende boolske udtryk ved hjælp af PLA (Programmable Logic Array)

X = AB + AC '

Y = AB '+ BC + AC'

Ovenstående to boolske funktioner er i form af SOP (sum af produkter). Produktbetegnelserne i de boolske udtryk er X & Y, og et produktudtryk, der er AC, er almindeligt i hver ligning. Så de samlede krævede logiske porte til generering af ovenstående to ligninger er OG porte-4, ELLER programmerbare ELLER porte-2. Det tilsvarende PLA-logikdiagram er vist nedenfor.

PLA Logic Circuit

AND-porte, der er programmerbare, har ret til indgang for normale såvel som supplerede variable indgange. I ovenstående logikdiagram er de tilgængelige indgange for hver AND-port A, A ’, B, B’, C, C ’. Så for at generere et enkelt produktudtryk med hver AND-gate kræves programmet.

Alle produktbetingelser kan fås ved indgangene til hver ELLER-port. Her kan de programmerbare forbindelser på logikporten betegnes med symbolet 'X'.

Forskel mellem PAL og PLA

Det Forskel mellem PAL og PLA i tabelform inkluderer hovedsageligt PAL og PLA fuld form , konstruktion, tilgængelighed, fleksibilitet, pris, antal funktioner og hastighed, som diskuteres nedenfor.

| Programmerbar Array Logic (PAL) | Programmable Logic Array (PLA) |

| Den fulde form for PAL er programmerbar array-logik | PLA's fulde form er et programmerbart logisk array |

| Konstruktionen af PAL kan udføres ved hjælp af den programmerbare samling af AND & OR-porte | Konstruktionen af PLA kan udføres ved hjælp af den programmerbare samling af OG & fast samling af ELLER porte. |

| Tilgængeligheden af PAL er mindre produktiv | Tilgængeligheden af PLA er mere |

| Fleksibiliteten ved PAL-programmering er mere | PLA's fleksibilitet er mindre |

| Omkostningerne ved en PAL er dyre | Omkostningerne ved PLA er mellemklasse |

| Antallet af funktioner implementeret i PAL er stort | Antallet af funktioner implementeret i PLA er begrænset |

| PAL-hastigheden er langsom | PLA's hastighed er høj |

Således handler det kun om PAL og PLA. Af ovenstående oplysninger kan vi endelig konkludere, at disse er de programmerbare logiske enheder (PLD'er), hvor programmerbar logisk matrix er mere fleksibel end programmerbar array-logik. Men programmerbar array-logik kan ubesværet generere et kombinationslogisk kredsløb. Her er et spørgsmål til dig, hvad er rollen som PAL og PLA inden for digital elektronik ?