Instruktions sæt eller instruktions sæt arkitektur er strukturen på computeren, der giver kommandoer til computeren til at guide computeren til behandling af databehandling. Instruktions sæt består af instruktioner, adresseringstilstande, native datatyper, registre, afbrydelse, undtagelseshåndtering og hukommelsesarkitektur. Instruktionssæt kan emuleres i software ved hjælp af en tolk eller indbygget i processorens hardware. Instruktions sætarkitektur kan betragtes som en grænse mellem softwaren og hardware. Klassificering af mikrokontroller og mikroprocessorer kan udføres baseret på RISC og CISC instruktions sæt arkitektur.

Instruktions sæt af processor

Instruktionssæt specificerer processorfunktionalitet inklusive de operationer, der understøttes af processoren, lagringsmekanismer for processoren og måden at kompilere programmerne til processoren på.

Hvad er RISC og CISC?

Det RISC og CISC kan udvides som følger:

RISC repræsenterer den reducerede instruktionssætcomputer og

CISC repræsenterer den komplekse instruktionscomputer.

RISC (Reduced Instruction Set Computer) Arkitektur

RISC Arkitektur

Det mikrokontroller arkitektur der bruger små og meget optimerede sæt instruktioner kaldes Reduced Instruction Set Computer eller simpelthen kaldet RISC. Det kaldes også som LOAD / STORE-arkitektur.

I slutningen af 1970'erne og begyndelsen af 1980'erne blev RISC-projekter primært udviklet fra Stanford, UC-Berkley og IBM. John Coke fra IBM-forskerteamet udviklede RISC ved at reducere antallet af instruktioner, der kræves til behandling af beregninger hurtigere end CISC. RISC-arkitekturen er hurtigere, og de chips, der kræves til fremstilling af RISC-arkitektur, er også billigere sammenlignet med CISC-arkitekturen.

Typiske træk ved RISC-arkitektur

- Rørledningsteknik for RISC udfører flere dele eller trin af instruktioner samtidigt, så hver instruktion på CPU'en er optimeret. Derfor har RISC-processorer ur pr. Instruktion af en cyklus, og dette kaldes som en cyklusudførelse.

- Det optimerer brug af register med mere antal registre i RISC og mere antal interaktioner i hukommelsen kan forhindres.

- Enkle adresseringstilstande, selv kompleks adressering kan udføres ved hjælp af aritmetik OG / ELLER logiske operationer .

- Det forenkler compilerdesignet ved hjælp af identiske generelle formålsregistre, der gør det muligt for ethvert register at blive brugt i enhver sammenhæng.

- For effektiv brug af registre og optimering af rørledningsanvendelserne kræves der reduceret instruktionssæt.

- Antallet af bits, der bruges til opkoden, reduceres.

- Generelt er der 32 eller flere registre i RISC.

Fordele ved RISC-processorarkitektur

- På grund af det lille sæt instruktioner fra RISC kan sprogkompilatorer på højt niveau producere mere effektiv kode.

- RISC giver frihed til at bruge rummet på mikroprocessorer på grund af dets enkelhed.

- I stedet for at bruge Stack bruger mange RISC-processorer registre til at sende argumenter og holde de lokale variabler.

- RISC-funktioner bruger kun nogle få parametre, og RISC-processorer kan ikke bruge opkaldsinstruktionerne og bruger derfor en instruktion med fast længde, som er let at pipeline.

- Operationshastigheden kan maksimeres, og udførelsestiden kan minimeres.

- Meget mindre antal instruktionsformater (mindre end fire), et par antal instruktioner (omkring 150) og et par adresseringsindstillinger (mindre end fire) er nødvendige.

Ulemper ved RISC-processorarkitektur

- Med stigningen i længden af instruktionerne øges kompleksiteten for RISC-processorer at udføre på grund af dens karaktercyklus pr. Instruktion.

- RISC-processorenes ydelse afhænger hovedsageligt af compileren eller programmøren, da kompilatorens viden spiller en vigtig rolle, mens CISC-koden konverteres til en RISC-kode, derfor afhænger kvaliteten af den genererede kode af compileren.

- Under omlægning af CISC-koden til en RISC-kode, betegnet som en kodeudvidelse, øges størrelsen. Og kvaliteten af denne kodeudvidelse afhænger igen af compileren og også af maskinens instruktions sæt.

- Det første niveau cache for RISC-processorer er også en ulempe ved RISC, hvor disse processorer har store hukommelsescacher på selve chippen. For at fodre instruktionerne kræver de meget hurtige hukommelsessystemer .

CISC (Complex Instruction Set Computer) Arkitektur

Hovedformålet med CISC-processorarkitekturen er at fuldføre opgaven ved at bruge færre antal samlebånd. Til dette formål er processoren bygget til at udføre en række operationer. Kompleks instruktion betegnes også som MULT, som fungerer hukommelsesbanker på en computer direkte uden at få compileren til at udføre lagrings- og indlæsningsfunktioner.

CISC Arkitektur

Funktioner i CISC Architecture

- For at forenkle computerarkitekturen understøtter CISC mikroprogrammering.

- CISC har flere antal foruddefinerede instruktioner, der gør sprog på højt niveau let at designe og implementere.

- CISC består af færre antal registre og mere antal adresseringstilstande, generelt 5 til 20.

- CISC-processor tager varierende cyklustid til udførelse af instruktioner - multi-ur-cyklusser.

- På grund af CISC's komplekse instruktionssæt er rørledningsteknikken meget vanskelig.

- CISC består af flere antal instruktioner, generelt fra 100 til 250.

- Særlige instruktioner bruges meget sjældent.

- Operander i hukommelsen manipuleres med instruktioner.

Fordele ved CISC-arkitektur

- Hver maskinsproginstruktion er grupperet i en mikrokodeinstruktion og udført i overensstemmelse hermed og lagres derefter indbygget i hovedprocessorens hukommelse, betegnet som implementering af mikrokoder.

- Da mikrokodehukommelsen er hurtigere end hovedhukommelsen, kan mikrokodeinstruksionssættet implementeres uden betydelig hastighedsreduktion i forhold til hard kablet implementering.

- Hele nye instruktionssæt kan håndteres ved at ændre mikroprogrammets design.

- CISC, antallet af instruktioner, der kræves for at implementere et program, kan reduceres ved at opbygge rige instruktionssæt og kan også fås til at bruge langsom hovedhukommelse mere effektivt.

- På grund af det overordnede sæt af instruktioner, der består af alle tidligere instruktioner, gør dette mikrokodning let.

Ulemper ved CISC

- Mængden af ur tid, der tages af forskellige instruktioner, vil være forskellig - på grund af dette - maskinens ydelse sænkes.

- Instruktionssættets kompleksitet og chiphardwaren stiger, da hver nye version af processoren består af en delmængde af tidligere generationer.

- Kun 20% af de eksisterende instruktioner bruges i en typisk programmeringsbegivenhed, selvom der findes mange specialiserede instruktioner, som ikke engang bruges ofte.

- De betingede koder indstilles af CISC-instruktionerne som en bivirkning af hver instruktion, der tager tid for denne indstilling - og da den efterfølgende instruktion ændrer betingelseskodebitene, skal compileren undersøge betingelseskodebitene, før dette sker.

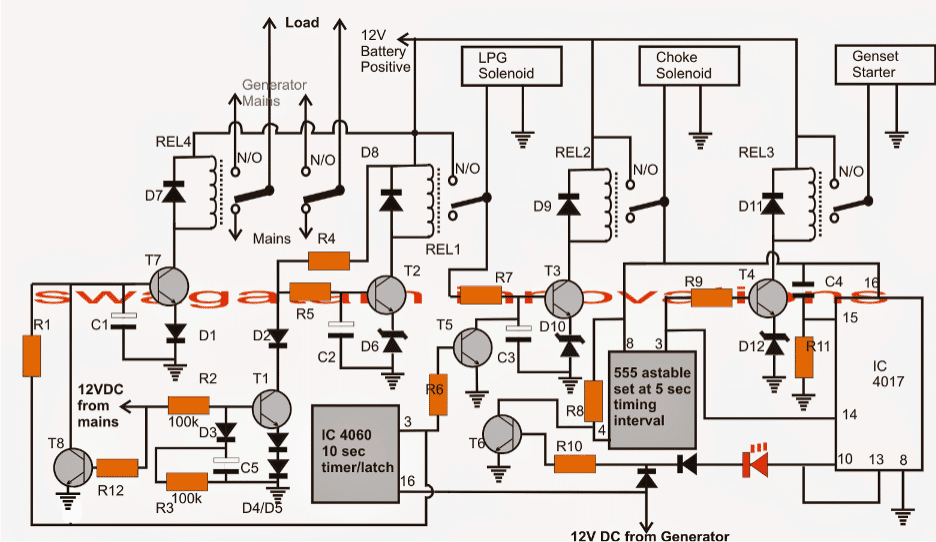

RISC Vs. CISC

- Spildecyklusser kan forhindres af programmøren ved at fjerne den unødvendige kode i RISC, men mens du bruger CISC-koden, fører det til spildecyklusser på grund af ineffektiviteten af CISC.

- I RISC er hver instruktion beregnet til at udføre en lille opgave, således at der til at udføre en kompleks opgave anvendes flere små instruktioner sammen, mens kun få instruktioner er nødvendige for at udføre den samme opgave ved hjælp af CISC - da den er i stand til at udføre en kompleks opgave da instruktionerne ligner en højsprogskode.

- CISC bruges typisk til computere, mens RISC bruges til smartphones, tablets og andre elektroniske enheder.

Den følgende figur viser flere forskelle mellem RISC og CISC

RISC Vs. CISC

Således diskuterer denne artikel om RISC- og CISC-arkitekturfunktionerne i RISC- og CISC-processorer arkitekturfordele og ulemper ved RISC og CISC og forskelle mellem RISC- og CISC-arkitekturer med en kort idé. For mere information om RISC og CISC arkitekturer, bedes du sende dine forespørgsler ved at kommentere nedenfor.

Fotokreditter:

- Instruktionssæt af Processor af arstechnica

- RISC Architecture af LSI-konkurrence

- RISC vs. CISC af ctildeling