Denne første del af den foreslåede 4kva synkroniserede stablet inverter kredsløb diskuterer, hvordan man implementerer den afgørende automatiske synkronisering på tværs af de 4 omformere med hensyn til frekvens, fase og spænding for at holde omformerne i gang uafhængigt af hinanden og alligevel opnå en udgang, der er på niveau med hinanden.

Idéen blev anmodet om af Mr. David. Følgende e-mail-samtale mellem ham og mig beskriver de vigtigste specifikationer for den foreslåede synkroniserede 4kva stabelbare inverter kredsløb.

E-mail nr. 1

Hej Swagatam,

For det første ville jeg sige tak for dit bidrag til verden som helhed, informationen og vigtigst af alt din vilje til at dele din viden til at hjælpe andre mennesker efter min mening er uvurderlig af mange grunde.

Jeg vil gerne forbedre nogle af de kredsløb, du har delt, så de passer til mine egne formål, desværre mens jeg forstår, hvad der foregår i kredsløbene, mangler jeg kreativitet og viden til selv at foretage ændringerne.

Jeg kan generelt følge kredsløb, hvis de er små, og jeg kan se, hvor de slutter / forbinder til større skemaer.

Hvis jeg må, vil jeg prøve at forklare, hvad jeg gerne vil opnå, selvom jeg ikke er under en illusion om, at du er en meget travl person og ikke gerne vil tage din dyrebare tid unødigt.

Det endelige mål ville være, at jeg gerne vil bygge (samle komponenterne) af et multikilde-vedvarende energimikronet ved hjælp af solcelleanlæg, vindmøller og biodieselgeneratorer.

Det første trin er forbedringerne af solcelleomformeren.

Jeg vil gerne bruge dit 48 volt rene sinusbølge inverter kredsløb, der er i stand til at opretholde en konstant 2kW 230V output, den skal være i stand til at levere mindst 3 gange denne output i en meget kort varighed.

Den nøgleændring, som jeg ønsker at opnå det for at oprette et antal af disse invertere enheder til at arbejde parallelt og tilsluttet en AC bus bar.

Jeg vil gerne have, at hver inverter uafhængigt og konstant prøver AC-busbjælken for frekvens, spænding og strøm (belastning).

Jeg vil kalde disse invertere slaveenheder.

Ideen om at vende modulerne er 'plug and play'.

Inverteren, når den først er tilsluttet vekselstrømsbjælken, vil konstant prøve / måle frekvensen på vekselstrømsbjælken og bruge denne information til at drive indgangen på en 4047 IC, således at dens urudgang kan fremføres eller forsinkes, indtil den nøjagtigt kloner frekvensen på AC-busbjælken, når de to bølgeformer er synkroniseret, vil inverteren lukke en kontaktor eller et relæ, der forbinder det inverterede udgangstrin med AC-busbjælken.

I tilfælde af at frekvensen på bjælken eller spændingen bevæger sig uden for en forudbestemt tolerance, skal invertermodulet åbne relæet eller kontaktoren på udgangstrinnet og effektivt afbryde omformerens udgangstrin fra vekselstrømsbjælken for at beskytte sig selv.

Når slavenhederne først er tilsluttet til AC-busbjælken, går de i dvale, eller i det mindste vil omformerens outputtrin sove, mens belastningen på baren er mindre end summen af alle slaveomformerne. Forestil dig, at hvis du vil, er der 3 slaveomformere knyttet til AC-busstangen, men belastningen på stangen er kun 1,8 kW, så de to andre slaver går i dvale.

Det gensidige ville også være sandt, at hvis belastningen på bjælken hoppede til at sige 3kW, ville en af de sovende invertere straks vågne (allerede være synkroniseret) for at levere den yderligere krævede energi.

Jeg forestiller mig, at nogle store kondensatorer på hvert output-trin vil levere den krævede energi, mens inverteren har det meget korte øjeblik, mens den vågner op.

Det ville være at foretrække (kun efter min mening) ikke at forbinde hver inverter direkte til hinanden, men snarere at de er uafhængige autonome.

Jeg vil forsøge at undgå mikrokontroller eller enhedsfejl eller fejlkontrol af hinanden eller enhederne har 'adresse' på systemet.

I mine tanker kan jeg forestille mig, at den første tilsluttede enhed på AC-busstangen ville være en meget stabil referenceomformer, der konstant er tilsluttet.

Denne referenceinverter ville give den frekvens og spænding, som de andre slaveenheder ville bruge til at generere deres egne respektive udgange.

Desværre kan jeg ikke få hovedet omkring, hvordan du kunne forhindre en feedback-loop, hvor slaveenhederne potentielt ender med at blive referencenheden.

Ud over omfanget af denne e-mail har jeg nogle små generatorer, som jeg gerne vil oprette forbindelse til AC-busbjælken, der synkroniseres med referenceomformeren for at levere energi i tilfælde af, at belastningen overstiger DC max-udgangskapaciteten.

Den overordnede forudsætning er, at den belastning, der præsenteres for vekselstrømsbjælken, vil bestemme, hvor mange invertere og i sidste ende hvor mange generatorer, der enten autonomt tilslutter eller afbryder for at imødekomme efterspørgslen, da dette forhåbentlig ville spare energi eller i det mindste ikke spilde energi.

Systemet, der er komplet bygget af flere moduler, vil så være udvideligt / kontraktibelt såvel som robust / elastisk, så hvis nogen eller måske to enheder skulle fejle, ville systemet fortsat fungere alt sammen ved reduceret kapacitet.

Jeg har vedhæftet et blokdiagram og udelukkede foreløbigt batteriopladningen.

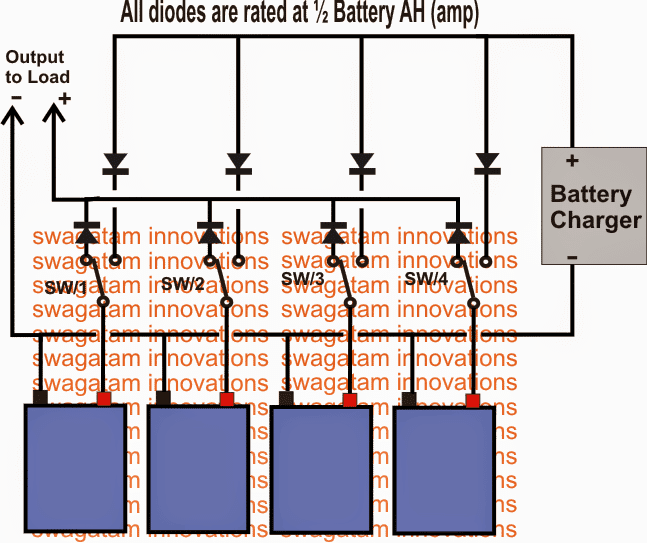

Jeg planlægger at oplade batteribanken fra vekselstrømsbussen og rette op til 48V jævnstrøm på denne måde, jeg kan oplade fra generatorerne eller de vedvarende energikilder, jeg erkender, at dette måske ikke er så effektivt som at bruge jævnstrøm mppt, men jeg tror, hvad jeg taber i effektivitet Jeg vinder i fleksibilitet. Jeg bor langt fra byen eller forsyningsnettet.

Til reference vil der være en minimum konstant belastning på vekselstrømsbjælken på 2 kW, selvom spidsbelastningen kunne stige med så meget som 30 kW.

Min plan er, at de første 10 til 15 kW leveres af solcelleanlæggene og to 3kW (peak) vindmøller, vindmøllerne er vilde AC rettet til DC og en 1000 Ah 48 volt batteribank. (Som jeg gerne vil undgå at dræne / aflade mere end 30% af dets kapacitet til at sikre batterilevetid) vil det resterende sjældne og meget intermitterende energibehov blive opfyldt af mine generatorer.

Denne sjældne og intermitterende belastning kommer fra mit værksted.

Jeg har tænkt på, at det kan være klogt at opbygge en kondensatorbank til at håndtere eller samle systemets slæk på enhver induktiv belastningsstartstrøm som motoren på min luftkompressor og bordsav.

Men jeg er ikke sikker på dette tidspunkt, om der ikke er en bedre / billigere måde.

Dine tanker og kommentarer vil blive meget værdsat og værdsat. Jeg håber du har tid til at komme tilbage til mig.

Tak for din tid og opmærksomhed på forhånd.

Med venlig hilsen David sendt fra min trådløse BlackBerry®-enhed

Mit svar

Hej David,

Jeg har læst dit krav og har forhåbentlig forstået det korrekt.

Ud af de 4 invertere ville kun en have sin egen frekvensgenerator, mens andre kørte ved at udtrække frekvensen fra denne hovedinverterudgang, og dermed ville alle være synkroniseret med hinanden og med denne masterinverter's specifikationer.

Jeg vil prøve at designe det og håbe, det fungerer som forventet, og i henhold til dine nævnte specifikationer skal implementeringen dog udføres af en ekspert, der skal være i stand til at forstå konceptet og ændre / tilpasse det til perfektion, uanset hvor det måtte være krævet .... ellers kan det blive ekstremt vanskeligt at få succes med dette rimeligt komplekse design.

Jeg kan kun præsentere det grundlæggende koncept og den skematiske ... hvile skal ingeniørerne udføre fra din side.

Det kan tage mig noget tid at gennemføre dette, da jeg allerede har mange ventende anmodninger i køen ... Jeg informerer dig som søn, når den er sendt

Med venlig hilsen Swag

E-mail nr. 2

Hej Swagatam,

Mange tak for dit meget hurtige svar.

Det er ikke helt, hvad jeg havde i tankerne, men repræsenterer bestemt et alternativ.

Min tanke var, at hver enhed ville have to frekvensmåling-delkredsløb, en der ser på frekvensen på AC-busbjælken, og denne enhed bruges til at skabe urepulsen til inverterens sinusbølgenerator.

Det andet underfrekvensmålekredsløb vil se på output fra inverterens sinusbølgenerator.

Der ville være et sammenligningskredsløb, der muligvis bruger et opamp-array, der ville strømme tilbage til inverterens sinusbølgeneratorpuls for at fremme uretsignalet eller forsinke uretsignalet, indtil output fra sinusbølgeneratoren nøjagtigt matchede sinusbølgen på vekselstrømsbjælken. .

Når frekvensen af omformerens udgangstrin matchede frekvensen af vekselstrømsbjælken, ville der være en SSR, der ville lukke forbinde omformerens udgangstrin til vekselstrømsbjælken, fortrinsvis ved nul kryds over punktet.

På denne måde kan ethvert invertermodul mislykkes, og systemet fortsætter med at fungere. Formålet med masterinverteren var, at det for alle invertermoduler aldrig ville gå i dvale og ville give den indledende AC-frekvens. men hvis det mislykkedes, ville de andre enheder ikke blive berørt, så længe en var 'online'

Slavenhederne skal lukke eller starte, når belastningen ændres.

Din iagttagelse var korrekt. Jeg er ikke en 'elektronik' mand. Jeg er en mekanisk og elektrisk ingeniør. Jeg arbejder med store anlægsgenstande som kølere og generatorer og kompressorer.

Efterhånden som dette projekt skrider frem, og begynder at blive mere håndgribeligt, ville du være vild / åben for at modtage en pengegave? Jeg har ikke meget, men jeg kan måske give nogle penge via PayPal for at hjælpe med at understøtte dine webhostingomkostninger.

Tak igen.

Jeg ser frem til at høre fra dig.

namaste

David

Mit svar

Tak David,

Dybest set vil du have, at omformerne skal være synkroniseret med hinanden med hensyn til frekvens og fase, og at hver og en har evnen til at blive masterinverter og overtage opladningen, hvis den forrige mislykkes på grund af en eller anden grund. Ret?

Jeg vil prøve at ordne dette med den viden, jeg har, og med en sund fornuft og ikke ved at anvende komplekse IC'er eller konfigurationer.

Varmeste hilsen Swag

E-mail nr. 3

Hej Swag,

Det er det i en møtrikskal, idet man tager et ekstra krav i betragtning.

Når belastningen falder, går omformerne i en øko- eller standbytilstand, og når belastningen stiger eller øges, vågner de for at imødekomme efterspørgslen.

Jeg elsker den tilgang, du går med ...

Mange tak, din overvejelse over for mig er meget værdsat.

Namaste

Venligste hilsen

David

Designet

Som anmodet af Mr. David, skal de foreslåede 4 kva stabelbare inverter-kredsløb være i form af 4 separate inverter-kredsløb, som kan stables korrekt i synkronisering med hinanden for at levere den korrekte mængde selvregulerende strøm til den tilsluttede belastninger, afhængigt af hvordan disse belastninger tændes og slukkes.

OPDATERING:

Efter nogle overvejelser indså jeg, at designet faktisk ikke behøver at være for kompliceret, men kunne implementeres ved hjælp af et simpelt koncept som vist nedenfor.

Kun IC 4017 sammen med dens tilknyttede dioder, transistorer og transformeren skal gentages for det krævede antal invertere.

Oscillatoren vil være et enkelt stykke og kan deles med alle invertere ved at integrere dens pin3 med pin14 i IC 4017.

Feedback-kredsløbet skal justeres nøjagtigt for de enkelte omformere, så afskæringsområdet er nøjagtigt matchet for alle invertere.

Følgende designs og forklaringerne kan ignoreres, da en meget lettere version allerede er opdateret ovenfor

Synkronisering af omformerne

Den største udfordring her er at gøre det muligt for hver af slaveomformerne at være synkroniseret med master-inverteren, så længe master-inverteren er i drift, og i en tilfælde (selvom det er usandsynligt), at master-inverteren svigter eller holder op med at arbejde, overtager den efterfølgende inverter oplades og bliver selve masterinverteren.

Og hvis den anden inveter også fejler, tager den tredje inverter kommandoen og spiller rollen som masterinverter.

Det er faktisk ikke svært at synkronisere omformerne. Vi ved, at det let kan gøres ved hjælp af IC'er som SG3525, TL494 osv. Den svære del af designet er dog at sikre, at hvis masterinverteren svigter, er en af de andre invertere i stand til hurtigt at blive master.

Og dette skal udføres uden at miste kontrollen over frekvens, fase og PWM selv i et split sekund og med en jævn overgang.

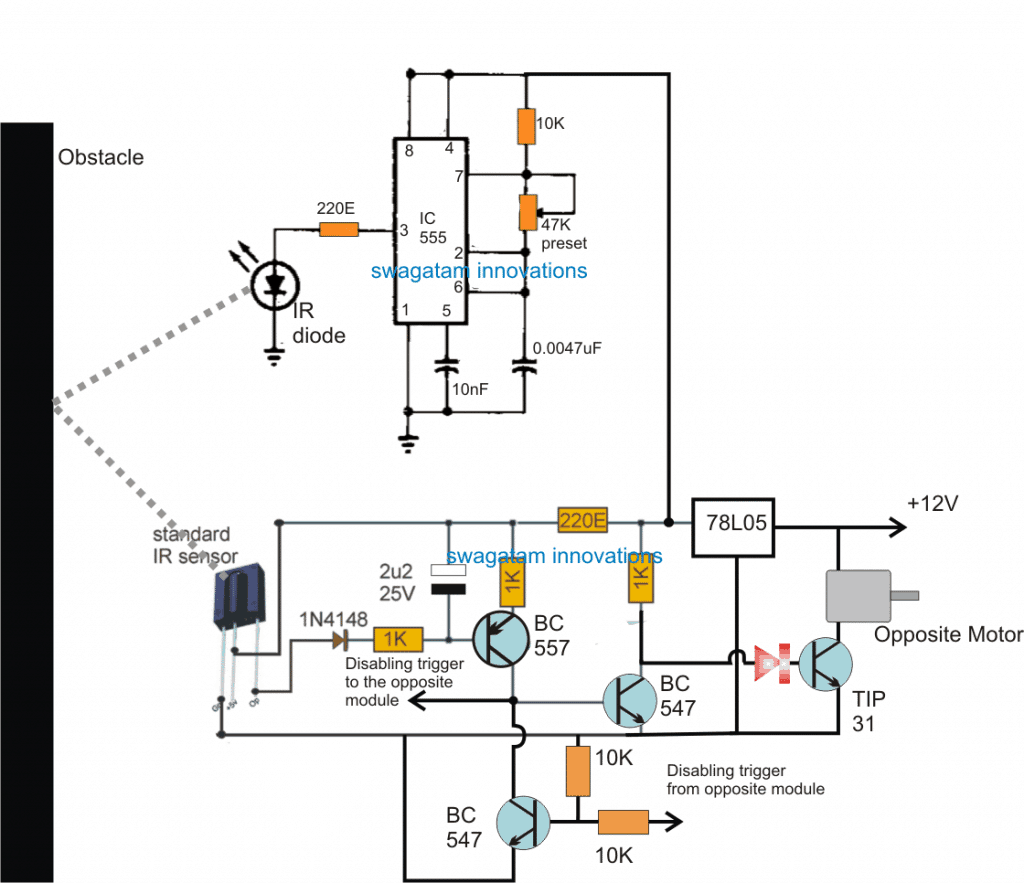

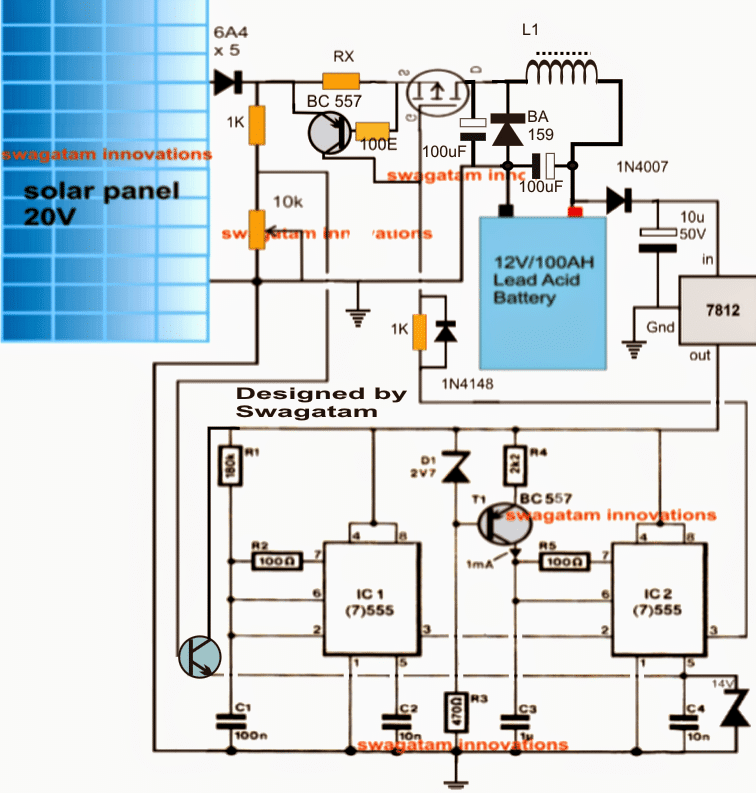

Jeg ved, at der kan være meget bedre ideer, det mest grundlæggende design til opfyldelse af de nævnte kriterier er vist i følgende diagram:

I figuren ovenfor kan vi se et par identiske trin, hvor den øvre inverter nr. 1 danner masterinverteren, mens den nedre inverter nr. 2 er slaven.

Flere trin i form af inverter # 3 og inverter # 4 formodes at blive tilføjet til opsætningen på samme identiske måde ved at integrere disse invertere med deres indivuduelle optokoblingstrin, men opamp-trinnet behøver ikke gentages.

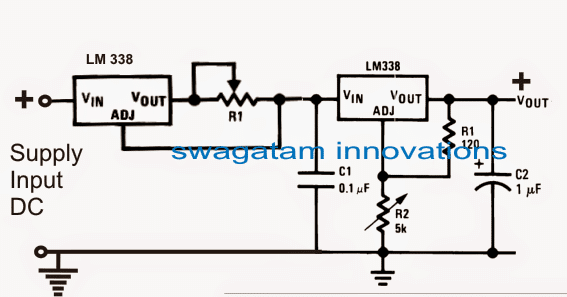

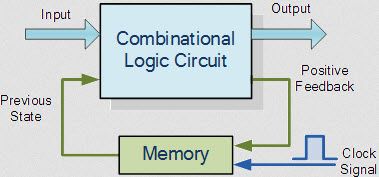

Designet består primært af en IC 555-baseret oscillator og et IC 4013-flip-flop-kredsløb. IC 555 er rigget til at generere urfrekvenser med en hastighed på 100Hz eller 120Hz, der føres til urindgangen på IC 4013, som derefter konverterer den til de krævede 50Hz eller 60Hz ved skiftevis at vende dens udgange med logik højt over pin # 1 og pin nr. 2.

Disse alternerende udgange bruges derefter til at aktivere strømforsyningerne og transformeren til at generere den tilsigtede 220V eller 120V AC.

Som diskuteret tidligere er det afgørende problem her at synkronisere de to invertere, så disse er i stand til at køre nøjagtigt synkroniseret med hensyn til frekvens, fase og PWM.

Oprindeligt justeres alle involverede moduler (stabelbare inverterkredsløb) separat med nøjagtigt identiske komponenter, så deres adfærd er perfekt på niveau med hinanden.

Men selv med de nøjagtigt matchede attributter, kan invertere ikke forventes at køre perfekt synkroniseret, medmindre disse er bundet på en unik måde.

Dette gøres faktisk ved at integrere 'slave' -omformerne gennem et opamp / optocoupler-trin som angivet i ovenstående design.

Oprindeligt er masterinverter nr. 1 tændt, hvilket gør det muligt for opamp 741-trinnet at blive tændt og initialisere frekvensen og fasesporing af udgangsspændingen.

Når dette er startet, tændes de efterfølgende omformere alle for at tilføje strøm til netledningen.

Som det kan ses, er opamp-udgangen forbundet med timingkondensatoren for alle slaveomformerne gennem en optokobler, der tvinger slaveomformerne til at følge frekvensen og fasevinklen på masterinverteren.

Men det interessante her er opampens låsefaktor med den øjeblikkelige fase- og frekvensinformation.

Dette sker, da alle invertere nu leverer og kører ved den angivne frekvens og fase fra masterinverteren, hvilket betyder, at hvis nogen af inverteren svigter inklusive masterinverteren, er opampen i stand til hurtigt at spore og injicere den øjeblikkelige frekvens / faseinfo og tvinge de eksisterende invertere til at køre med disse specifikationer, og inverteren er til gengæld i stand til at opretholde tilbagemeldingerne til opamp-scenen for at gøre overgange problemfri og selvoptimerende.

Derfor tager forhåbentlig opamp-scenen sig af den første udfordring at holde alle de foreslåede stabelbare omformere perfekt synkroniseret gennem en LIVE-sporing af den tilgængelige netspecifikation.

I den næste del af artiklen lærer vi synkroniseret PWM sinusbølgetrin , som er det næste afgørende træk ved det ovenfor diskuterede design.

I ovenstående del af denne artikel lærte vi hovedsektionen i det 4kva synkroniserede stabelbare inverterkredsløb, der forklarede synkroniseringsoplysningerne i designet. I denne artikel studerer vi, hvordan man gør designet til en sinusbølgeækvivalent og også sikrer korrekt synkronisering af PWM'erne på tværs af de involverede invertere.

Synkronisering af Sine Wave PWM på tværs af omformerne

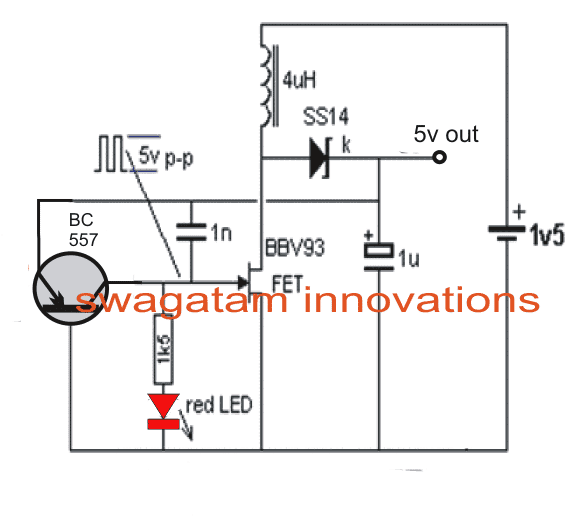

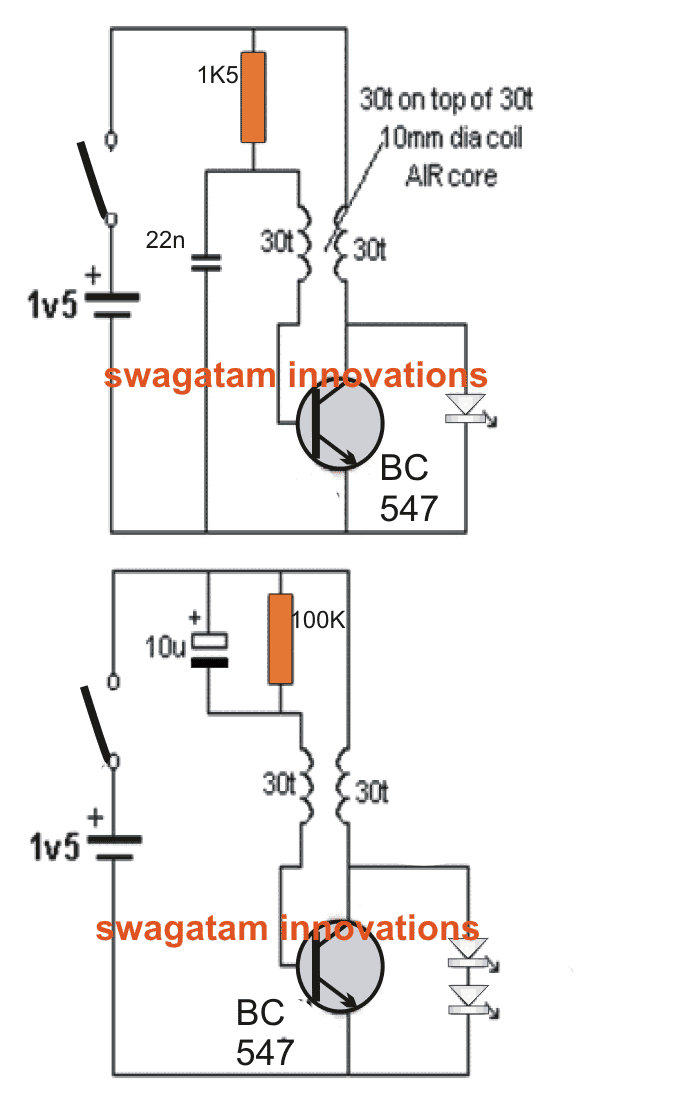

En simpel RMS-matchet PWM-ækvivalent sinusbølgeformgenerator kan fremstilles ved hjælp af en IC 555 og IC 4060, som vist i den følgende figur.

Dette design kan derefter bruges til at gøre det muligt for invertere at producere en sinusbølgeækvivalent bølgeform ved deres udgange og over den tilsluttede netledning.

Hver af disse PWM-processorer ville være påkrævet for hvert af de stabelbare invertermoduler individuelt.

OPDATERING: Det ser ud til, at en enkelt PWM-processor kan bruges til at hugge alle transistorbaser, forudsat at hver MJ3001-base forbinder med den specifikke BC547-opsamler gennem en individuel 1N4148-diode. Dette forenkler designet i høj grad.

De forskellige faser involveret i ovennævnte PWM geneartor kredsløb kan forstås ved hjælp af følgende punkt:

Brug af IC 555 som PWM-generator

IC 555 er konfigureret som det grundlæggende PWM-generator kredsløb. For at være i stand til at generere en justerbar PWM-ækvivalent impulser ved den ønskede RMS kræver IC'et hurtige trekantbølger ved sin pin7 og et referencepotentiale ved sin pin5, der bestemmer PWM-niveauet ved sin output pin # 3

Brug IC 4060 som Triangle Wave Generator

For at generere trekantsbølgerne kræver IC 555 firkantede bølger ved sin pin nr. 2, som er erhvervet fra IC 4060 oscillatorchippen.

IC 4060 bestemmer frekvensen af PWM eller simpelthen antallet af 'søjler' i hver af vekselstrømshalvcyklerne.

IC 4060 anvendes hovedsageligt til at multiplicere prøven med lavt frekvensindhold fra inverterudgangen til en relativt høj frekvens fra dens pin # 7. Prøvefrekvensen sørger grundlæggende for, at PWM-huggen er ens og synkroniseret for alle indtrængermoduler. Dette er hovedårsagen til, at IC 4060 er inkluderet, ellers kunne en anden IC 555 let have gjort jobbet i stedet.

Referencepotentialet ved pin nr. 5 i IC 555 opnås fra en opamp spændingsfølger vist yderst til venstre for kredsløbet.

Som navnet antyder, leverer denne opamp nøjagtigt den samme størrelsesorden spænding ved sin pin # 6, som vises ved dens pin # 3 .... dog er pin # 6-replikering af dens pin # 3 pænt bufret og er derfor rigere end dens pin3-kvalitet, og det er den nøjagtige grund til at medtage dette trin i designet.

Den 10 k forudindstilling, der er tilknyttet pin3 på denne IC, bruges til at justere RMS-niveauet, som i sidste ende finindstiller IC 555-output-PWM'erne til det ønskede RMS-niveau.

Denne RMS påføres derefter baserne på strømindretningerne for at tvinge dem til at arbejde på de specificerede PWM RMS-niveauer, hvilket igen får output AC til at erhverve en ren sinusbølgelignende egenskab gennem et korrekt RMS-niveau. Dette kan forbedres yderligere ved at anvende et LC-filter på tværs af outputviklingen af alle transformatorerne.

Den næste og sidste del af dette 4 kva stabelbare synkroniserede inverter-kredsløb beskriver den automatiske belastningskorrektionsfunktion, der gør det muligt for invertere at levere og opretholde den korrekte mængde watt på tværs af udgangsnettet i overensstemmelse med de forskellige belastningsomskiftninger.

Vi har hidtil dækket de to hovedkrav til det foreslåede synkroniserede 4kva stabelbare inverter kredsløb, som inkluderer synkronisering af frekvens, fase og PWM på tværs af invertere, så svigt af nogen af invertere havde ingen effekt på resten med hensyn til ovenstående parametre .

Automatisk belastningskorrektionsfase

I denne artikel vil vi forsøge at finde ud af den automatiske belastningskorrektionsfunktion, som muligvis kan tænde eller slukke for inverteren sekventielt som reaktion på de forskellige belastningsforhold på tværs af udgangsnettet.

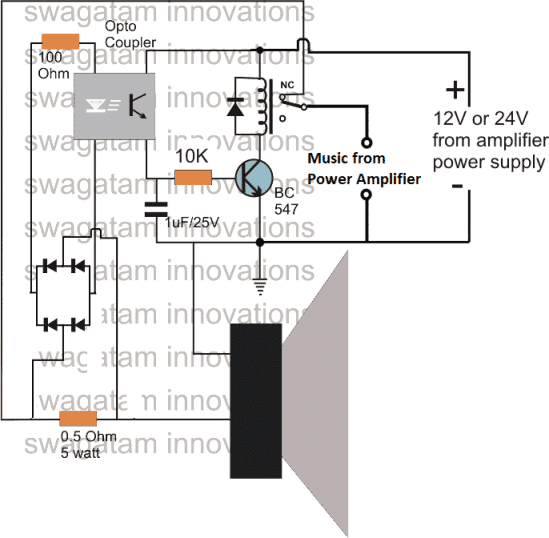

En simpel quad-komparator ved hjælp af LM324 IC kan bruges til at implementere en automatisk sekventiel belastningskorrektion som angivet i følgende diagram:

I figuren ovenfor kan vi se fire opamper fra IC LM324 konfigureret som fire separate komparatorer med deres ikke-inverterende indgange rigget med individuelle forudindstillinger, mens deres inverterende indgange alle refereres til med en fast zenerspænding.

De relevante forudindstillinger justeres simpelthen således, at opamperne producerer høje udgange i en rækkefølge, så snart netspændingen går over den tilsigtede tærskel ..... og omvendt.

Når dette sker, skifter de relevante transistorer i overensstemmelse med opampaktivering.

Samlerne af de respektive BJT'er er forbundet med stift nr. 3 på spændingsfølgeren opamp IC 741, som er anvendt i PWM-styretrinnet, og dette tvinger opampudgangen til at blive lav eller nul, hvilket igen får en nulspænding til at vises ved pin nr. 5 i PWM IC 555 (som diskuteret i del 2).

Med pin nr. 5 i IC 555 anvendes med denne nul-logik, tvinger PWM'erne til at blive smalleste eller ved minimumsværdien, hvilket får output fra den pågældende inverter til næsten at lukke ned.

Ovenstående handlinger gør et forsøg på at stabilisere output til en tidligere normal tilstand, som igen tvinger PWM til at blive bredere, og denne trækkamp eller en konstant omskiftning af opamps fortsætter konsekvent med at holde output så stabilt som muligt som reaktion på variationerne af de vedhæftede belastninger.

Med denne automatiske belastningskorrektion implementeret inden for det foreslåede 4kva stabelbare inverter kredsløb gør designet næsten komplet med alle de funktioner, som brugeren anmoder om i artikel 1, del.

Forrige: Lav denne SleepWalk-advarsel - Beskyt dig selv mod Sleepwalking-farer Næste: IC 555 pinouts, astable, monostable, bistable kredsløb med formler udforsket