Artiklen forklarer et solid state switch-mode netspændingsstabilisator kredsløb uden relæer ved hjælp af en ferritkerne boostkonverter og et par halvbro-mosfet driver kredsløb. Ideen blev anmodet om af Mr. McAnthony Bernard.

Tekniske specifikationer

For sent begyndte jeg at se på spændingsstabilisatorer, der bruges i husholdningen, til at regulere forsyningsforsyningen , boost spænding, når forsyningsspændingen er lav, og træder ned, når forsyningsspændingen er høj.

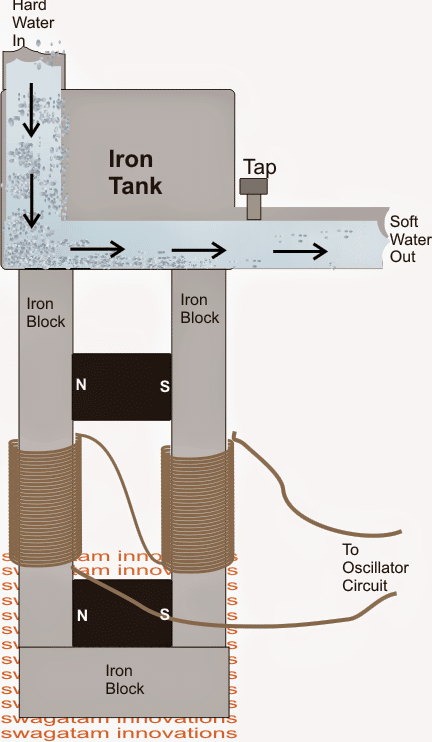

Den er bygget omkring strømtransformator (jernkerne) viklet i auto transformer stil med mange vandhaner på 180v, 200v, 220v, 240v 260v osv.

kontrolkredsløbet ved hjælp af et relæ vælger det rigtige tryk for output. Jeg antager, at du kender denne enhed.

Jeg begyndte at tænke på at implementere denne enheds funktion med SMPS. Hvilket har fordelen ved at give konstant 220vac og stabil frekvens på 50Hz uden brug af relæer.

Jeg har vedhæftet i denne mail blokdiagrammet for konceptet.

Lad mig vide, hvad du synes, hvis det giver mening at gå den rute.

Vil det virkelig fungere og tjene det samme formål? .

Jeg har også brug for din hjælp i sektionen med højspænding DC til DC-konverter.

Hilsen

McAnthony Bernard

Designet

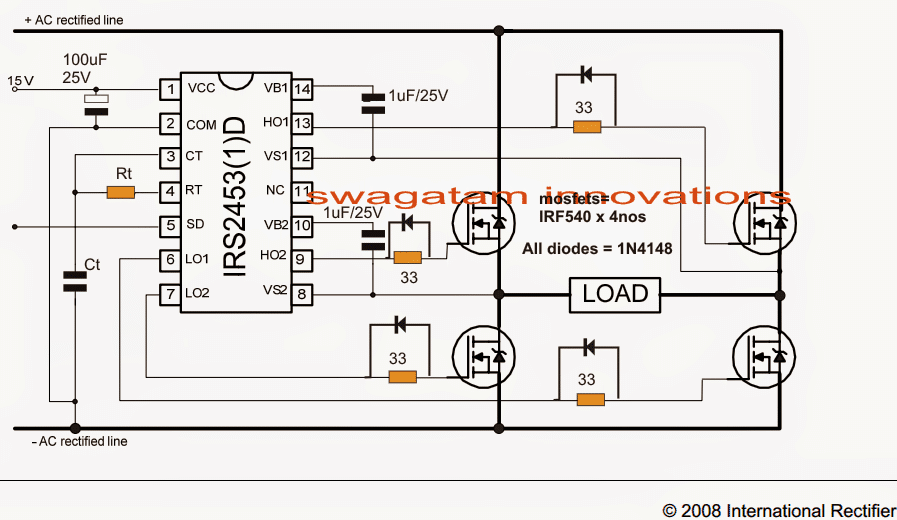

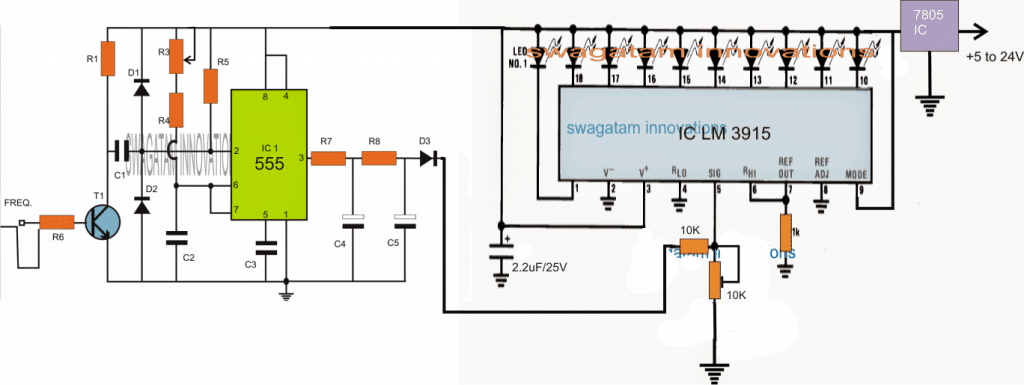

Det foreslåede solid state ferrit-kerne-baserede netspændingsstabiliseringskredsløb uden relæer kan forstås ved at henvise til det følgende diagram og den efterfølgende forklaring.

RVCC = 1K.1watt, CVCC = 0.1uF / 400V, CBOOT = 1uF / 400V

Ovenstående figur viser den faktiske konfiguration til implementering af en stabiliseret 220V eller 120V output uanset indgangssvingningerne eller en overbelastning ved hjælp af et par ikke-isolerede boostkonverterprocessortrin.

Her bliver to halvbrodriver-mosfet-IC'er de afgørende elementer i hele designet. De involverede IC'er er den alsidige IRS2153, der blev designet specielt til at drive mosfeter i halvbrotilstand uden behov for komplekse eksterne kredsløb.

Vi kan se to identiske halvbrodriverfaser indarbejdet, hvor venstre sides driver bruges som boost-driver-trin, mens højre side er konfigureret til behandling af boostspændingen til en 50Hz eller 60Hz sinusbølgeoutput i forbindelse med en ekstern spændingskontrol kredsløb.

IC'erne er internt programmeret til at producere en fast 50% arbejdscyklus på tværs af output pinouts gennem en totempoletopologi. Disse pinouts er forbundet med power mosfets til implementering af de tilsigtede konverteringer. IC'erne er også udstyret med en intern oscillator til aktivering af den krævede frekvens ved udgangen, frekvensens hastighed bestemmes af et eksternt tilsluttet Rt / Ct-netværk.

Brug af funktionen Luk ned

IC'en har også en nedlukningsfacilitet, som kan bruges til at stoppe output i tilfælde af overstrøm, overspænding eller enhver pludselig katastrofal situation.

For mere info om th er halvbro-driver IC'er, kan du henvise til denne artikel: Half-Bridge Mosfet Driver IC IRS2153 (1) D - Pinouts, Explained Application Notes

Outputene fra disse IC'er er ekstremt afbalancerede på grund af en meget sofistikeret intern bootstrapping og dead time-behandling, der sikrer en perfekt og sikker drift af de tilsluttede enheder.

I det diskuterede SMPS-netspændingsstabiliseringskredsløb bruges venstre sidetrin til at generere omkring 400V fra en 310V-indgang afledt ved at rette på 220V-netindgangen.

For en 120V-indgang kan scenen indstilles til at generere omkring 200V gennem den viste induktor.

Spolen kan vikles over en hvilken som helst standard EE-kerne / spoleenhed ved hjælp af 3 parallelle (bifilare) tråde af 0,3 mm superemaljeret kobbertråd og ca. 400 omdrejninger.

Valg af frekvens

Frekvensen bør indstilles ved korrekt at vælge værdierne for Rt / Ct, således at der opnås en høj frekvens på ca. 70 kHz for det venstre boostkonvertertrin over den viste induktor.

Højre driver IC er positioneret til at arbejde med ovennævnte 400V DC fra boostkonverteren efter passende afhjælpning og filtrering, som det kan ses i diagrammet.

Her er værdierne for Rt og Ct valgt til at erhverve ca. 50Hz eller 60Hz (i henhold til landespecifikationerne) på tværs af den tilsluttede mosfetsudgang

Outputtet fra højre drivertrin kan dog være så højt som 550V, og dette skal reguleres til de ønskede sikre niveauer på omkring 220V eller 120V

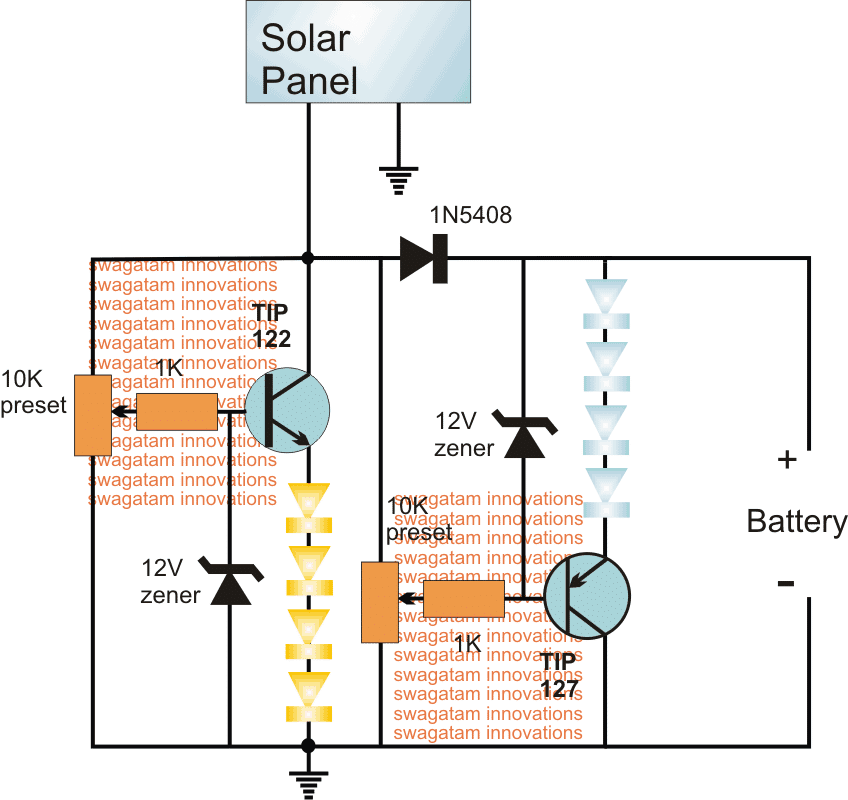

Til dette er en simpel opamp-fejlforstærkerkonfiguration inkluderet som vist i det følgende diagram.

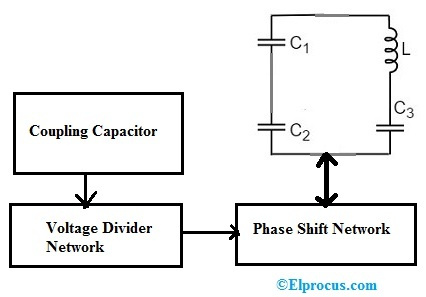

Overspændingskorrektionskredsløb

Som vist i ovenstående diagram anvender spændingskorrektionstrinnet en simpel opamp-komparator til detektion af overspændingstilstanden.

Kredsløbet skal kun indstilles en gang for at nyde en permanent stabiliseret spænding på det indstillede niveau uanset indgangssvingningerne eller en overbelastning, men disse overskrides muligvis ikke over en specificeret acceptabel grænse for designet.

Som illustreret er forsyningen til fejlforstærkeren afledt af udgangen efter passende afhjælpning af AC til en ren lavstrøm stabiliseret 12V DC til kredsløbet.

pin nr. 2 er udpeget som sensorindgangen til IC, medens den ikke-inverterende pin nr. 3 henvises til en fast 4.7V gennem et fastspændende zenerdiodenetværk.

Registreringsindgangen ekstraheres fra et ustabiliseret punkt i kredsløbet, og udgangen fra IC'en er tilsluttet med Ct-stiften på højre driver IC.

Denne pin fungerer som lukkestiften til IC'en, og så snart den oplever en lav under 1/6 af dens Vcc, tømmer den øjeblikkeligt outputfeeds til mosfeterne, der lukker proceduren for at stå stille.

Forudindstillingen, der er knyttet til opamp nr. 2, justeres korrekt, således at udgangsnettet vender sig ned til 220 V fra den tilgængelige 450 V eller 500 V udgang, eller til 120 V fra en 250 V udgang.

Så længe pin nr. 2 oplever en højere spænding med henvisning til pin nr. 3, fortsætter den med at holde sin output lav, hvilket igen beordrer driver IC til at lukke ned, men 'lukning' korrigerer øjeblikkeligt opamp-input og tvinger det for at trække sit lave signal ud, og cyklussen holder selvkorrigering af udgangen til de nøjagtige niveauer, som bestemt af forudindstillet pin nr. 2.

Fejlforstærkerkredsløbet fortsætter med at stabilisere dette output, og da kredsløbet har fordelen ved en signifikant 100% margen mellem inputkildens spænding og de regulerede spændingsværdier, selv under ekstremt lave spændingsforhold, formår udgangene at levere den faste stabiliserede spænding til belastningen. uanset spænding bliver det samme tilfældet, når en umatchet belastning eller en overbelastning er forbundet ved udgangen.

Forbedring af ovenstående design:

En omhyggelig undersøgelse viser, at ovennævnte design kan modificeres og forbedres meget for at øge effektiviteten og outputkvaliteten:

- Spolen er faktisk ikke påkrævet og kan fjernes

- Outputtet skal opgraderes til et komplet brokredsløb, så effekten er optimal til belastningen

- Outputtet skal være en ren sinusbølge og ikke en modificeret, som det kan forventes i ovenstående design

Alle disse funktioner er blevet overvejet og taget hånd om i den følgende opgraderede version af solid state stabilisator kredsløb:

Kredsløb

- IC1 fungerer som et normalt, stabilt multivibratoroscillatorkredsløb, hvis frekvens kan justeres ved at ændre værdien på R1 korrekt. Dette bestemmer antallet af 'søjler' eller 'huggning' for SPWM-output.

- Frekvensen fra IC 1 ved sin pin nr. 3 tilføres til pin nr. 2 i IC2, som er kablet som en PWM-generator.

- Denne frekvens konverteres til trekantbølger ved pin # 6 i IC2, som sammenlignes med en prøvespænding ved pin nr. 5 i IC2

- Stift nr. 5 i IC2 påføres med sinusprøve ved 100 Hz frekvens, der er erhvervet fra broensretteren efter passende nedtrapping af lysnettet til 12 V.

- Disse sinusbølgeprøver sammenlignes med pin nr. 7 trekantbølger af IC2, hvilket resulterer i en proportionalt dimesnioneret SPWM ved pin nr. 3 i IC2.

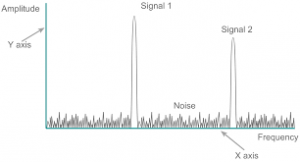

- Nu afhænger pulsbredden af denne SPWM af amplituden af prøven sinusbølger fra broensretteren. Med andre ord, når AC-netspændingen er højere, producerer bredere SPWM'er, og når AC-netspændingen er lavere, reducerer den SPWM-bredden og gør den mindre proportionalt.

- Ovenstående SPWM inverteret af en BC547-transistor og anvendt på portene til de lave sidemosfeter til et fuldt brodrivernetværk.

- Dette indebærer, at når AC-strømniveauet falder, vil reaktionen på mosfet-porte være i form af forholdsmæssigt bredere SPWM'er, og når AC-netspændingen stiger, vil portene opleve en forholdsvis forværret SPWM.

- Ovenstående anvendelse vil resultere i en proportional spændingsforøgelse på tværs af den belastning, der er forbundet mellem H-bridge-netværket, når indgangsstrømmen falder, og omvendt vil belastningen gå igennem et proportionalt spændingsfald, hvis AC har tendens til at stige over fareniveauet.

Sådan opsættes kredsløbet

Bestem det omtrentlige centerovergangspunkt, hvor SPWM-responset muligvis kan være identisk med lysnettet.

Antag at du vælger, at den skal være ved 220V, og derefter justerer 1K-forudindstillingen, så den belastning, der er forbundet med H-broen, modtager ca. 220V.

Det er alt, opsætningen er færdig nu, og resten bliver automatisk taget hånd om.

Alternativt kan du rette ovenstående indstilling mod det lavere spændingstærskelniveau på samme måde.

Antag, at den nedre tærskel er 170V, i så fald skal du føre en 170V til kredsløbet og justere 1K-forudindstillingen, indtil du finder cirka 210V på tværs af belastningen eller mellem H-broarmene.

Disse trin afslutter opsætningsproceduren, og resten justeres automatisk i henhold til input-AC-niveauændringerne.

Vigtig : Tilslut venligst en højværdiskondensator i størrelsesordenen 500uF / 400V på tværs af den vekselstrømsrettet ledning, der føres til H-bridge-netværket, så den udbedrede jævnstrøm er i stand til at nå op til 310V jævnstrøm over H-broens BUS-linjer.

Forrige: Oprettelse af 3.3V, 5V spændingsregulator kredsløb med dioder og transistorer Næste: Simple Musical Door Bell Circuit