I denne artikel vil vi diskutere mange forskellige kredsløbsidéer bygget ved hjælp af NAND-porte fra IC'er som IC 7400, IC 7413, IC 4011 og IC 4093 osv.

IC 7400, IC 7413 Specifikationer

I.C.s 7400 og 7413 er 14-pin DIL ICs eller '14 pin Dual In Line Integrated Circuits ', hvor pin 14 er den positive forsyning V + og pin 7 er den negative, jord eller 0 V pin.

Forsyningsindgange til ben 14 og 7 er ikke vist på tegningerne for enkelheds skyld, men du rådes til ikke at glemme at forbinde disse ben, ellers ville kredsløbet simpelthen ikke fungere!

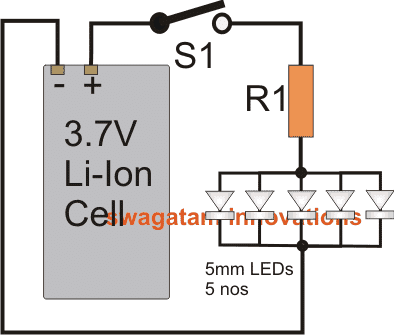

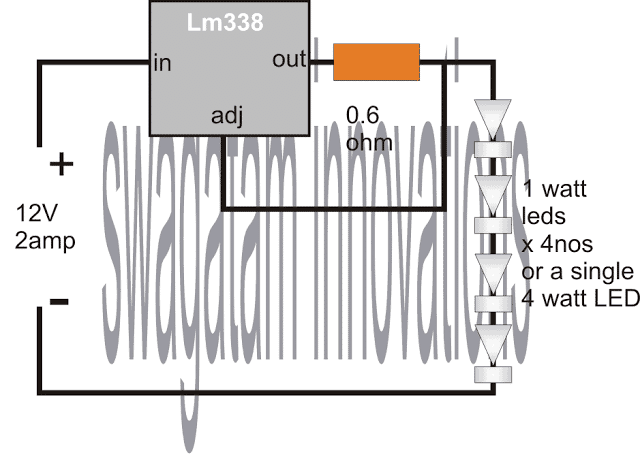

Alle kredsløb fungerer ved hjælp af en 4,5 V eller 6 V DC forsyning, men den typiske spænding kan være 5 volt. En netdrevet 5 V reguleret forsyning kan opnås gennem en række muligheder.

De 4 porte til en 7400 er nøjagtig de samme med deres specifikationer:

- Gate A ben 1, 2 indgange, pin 3 udgang

- Gate B ben 4, 5 indgange, pin 6 udgang

- Gate C-ben 10, 9 indgange, pin 8-udgang

- Gate D-ben 13, 12 indgange, pin 11-udgang

Du kan finde et specifikt kredsløb, der angiver en oscillator, der anvender porte A og B, men dette betyder også, at det samme kan designes ved hjælp af porte A og C, B og C eller C og D også uden problemer.

Figur 1 viser det logiske kredsløb på din 7400 I.C. Figur 2 viser den logiske symbolske repræsentation for kun en port, hver enkelt gate normalt en '2 Input NAND Gate'.

Den interne konfiguration med en individuel port vises i figur 3. 7400 er en TTL-logik, der betyder, at den fungerer ved hjælp af 'Transistor-Transistor-Logic'. Hver eneste gate beskæftiger fire transistorer, hver 7400 består af 4 x 4 = 16 transistorer.

De logiske porte inkluderer et par tilstande, afhængigt af det binære system, 1 eller 'Høj' typisk 4 volt og 0 (nul) eller 'Lav' typisk 0 volt. Hvis en portterminal ikke bruges. der kan svare til 1 input.

Det betyder, at en åben portstift er på 'højt' niveau. Når en gateindgangsstift er forbundet med jorden eller 0 volt-linjen, bliver indgangen derefter 0 eller logisk lav.

En NAND gate er faktisk en blanding af 'NOT og AND' gate når begge dens indgange (og funktion) er ved logik 1, output er en IKKE gate output, som er 1.

Outputtet fra en IKKE gate vil være 0V som svar på et 1 indgangssignal eller + forsyningsindgang, hvilket betyder, at udgangen vil være logisk nul, når indgangen er på + forsyningsniveau.

For en NAND-gate, når begge indgange er logisk 0, bliver output til logik 1, hvilket er nøjagtigt som et IKKE gate-svar. Det kan se svært ud at forstå nøjagtigt, hvorfor output er 1, når input holdes på 0, og omvendt.

Det kan forklares på denne måde

For en omskiftning af tilstand skal en AND-funktion opstå, det vil sige hver indgang skal transformeres for at skifte tilstand.

Dette sker udelukkende, når de to indgange skifter mellem 0 og 1. 7400 porte er 2 input NAND porte, men 3 input NAND porte 7410 IC, 4 input NAND porte 7420 og også en 8 input NAND gate 7430 kan også købes let fra markedet. .

Med hensyn til 7430 skifter dens 8 indgangsport kun tilstand, når hver af de 8 indgange enten er 1 eller 0.

Når de 74 indgange fra 7430 er 1,1,1,1,1,1,1,0, vil udgangen fortsat være 1. Tilstandsændringen sker ikke, så længe alle 8 indgange ikke har de samme logik .

Men så snart den sidste indgang skifter fra 0 til 1, ændres udgangen fra 1 til 0. Teknikken, der forårsager 'skift af tilstand', er et afgørende aspekt for at forstå funktionaliteten i logiske kredsløb.

Antallet af ben, som en logisk IC almindeligvis kan have, er 14 eller 16. En 7400 består af fire NAND-porte, med 2 indgangsben og 1 udgangsstift til hver af portene, og også et par ben til strømforsyningsindgange, pin 14 og pin 7.

IC 7400 familie

De andre medlemmer af 7400-familien kan komme med et højere antal input-pins såsom 3 input NAND-porte, 4 input NAND-porte og 8 input NAND-gate med flere indgangskombinationsmuligheder for hver gate. Som eksempel er IC 7410 en variant af 3 input NAND-porte eller en 'Triple 3 input NAND gate'.

IC 7420 er en variant af 4 input NAND-porte og kaldes også 'Dual 4 input NAND gate', mens IC 7430 er et medlem, der har 8 indgange og er kendt som 8-input NAND gate.

Grundlæggende NAND-portforbindelser

Mens IC 7400 kun har NAND-porte, er det muligt at forbinde NAND-porte på en række måder.

Dette giver os mulighed for at konvertere dem til andre former for gate som:

(1) en inverter eller 'IKKE' port

(2) en AND-port

(3) en ELLER-port

(4) NOR-port.

IC 7402 ligner 7400, selvom den består af 4 NOR-porte. På samme måde som NAND er en kombination af 'IKKE plus OG', er NOR blanding af 'IKKE plus ELLER'.

7400 er en ekstremt tilpasningsbar IC, som det kan findes fra rækkefølgen af kredsløb i applikationsguiden.

For at hjælpe dig med fuldt ud at forstå funktionaliteten af en NAND-gate, vises en SANDHED-tabel ovenfor for en 2-input NAND-gate.

Ækvivalente sandhedstabeller kunne evalueres for næsten enhver logisk gate. Sandhedstabellen til en 8-indgangsport som 7430 er noget mere kompleks.

Sådan testes en NAND-port

For at kontrollere en 7400 IC kan du anvende strøm på tværs af ben 14 og 7. Hold ben 1 og 2 tilsluttet til positiv forsyning, dette viser output som 0.

Derefter tilsluttes pin 1 til 0 volt uden at skifte pin 2-forbindelse. Dette gør det muligt for indgangene at blive 1, 0. Dette får udgangen til at dreje 1, hvilket lyser LED. Nu skal du blot skifte pin 1 og pin 2-forbindelser, så indgangene bliver 0, 1, dette skifter output til logik 1 og slukker for LED.

I det sidste trin skal du tilslutte begge indgangsstifterne 1 og 2 til jord eller 0 volt, så indgangene er på logik 0, 0. Dette vil endnu en gang slå output til logisk højt eller 1, når LED'en tændes. Lysdioden lyser betegner det logiske niveau 1.

Når LED er slukket, antyder dette logisk niveau 0. Analysen kan gentages for portene B, C og D.

Bemærk: hvert af de kredsløb, der er bevist her, fungerer med 1 / 4W 5% modstande - alle elektrolytkondensatorer er generelt 25V nominelle.

Hvis et kredsløb ikke fungerer, kan du se på forbindelserne, muligheden for en defekt IC kan være meget usandsynlig sammenlignet med en forkert tilslutning af stifterne. Disse forbindelser til en NAND-port vist nedenfor kan være de mest basale og fungerer kun ved hjælp af 1 gate på en 7400.

1) IKKE port fra en NAND-port

Når indgangsstifterne a i en NAND-port kortsluttes med hinanden, fungerer kredsløbet som en inverter, hvilket betyder, at outputlogikken altid viser det modsatte af indgangen.

Når portens kortsluttede indgangsstifter er forbundet til 0V, bliver udgangen til 1 og omvendt. Fordi 'IKKE' konfigurationen giver et modsat svar på tværs af input og output pins, deraf navnet NOT gate. Denne sætning er faktisk en teknisk passende.

2) Oprettelse OG port fra en NAND-port

Da en NAND-port også er en slags 'IKKE OG' -port, så hvis en 'IKKE' -port indføres efter en NAND-port, bliver kredsløbet til en 'IKKE IKKE OG' -port.

Et par negativer giver et positivt (en forestilling, der også er populær i matematiske begreber). Kredsløbet er nu blevet en OG-port som vist ovenfor.

3) Oprettelse ELLER Gate fra NAND Gates

Indsættelse af en IKKE-port før hver NAND-gateindgang genererer en ELLER-port som vist ovenfor. Dette er normalt en 2-input ELLER gate.

4) Oprettelse af NOR Gate fra NAND Gates

I det forrige design oprettede vi en ELLER-port fra NAND-porte. En NOR-port bliver faktisk en IKKE ELLER port, når vi tilføjer en ekstra IKKE-port lige efter en ELLER-port som vist ovenfor.

5) Logisk niveau tester

Dette logiske niveau testede kredsløb kan oprettes gennem en enkelt 7400 NAND gate som en inverter eller IKKE gate til at indikere logiske niveauer. Et par røde lysdioder anvendes til at skelne mellem logiske niveauer på tværs af LED 1 og LED 2.

LED-stiften, der er længere, bliver katoden eller den negative stift på LED-en. Når indgangen er på logisk niveau 1 eller HIGH, lyser LED 1 naturligt.

Stiften 3, som er udgangsstiften, er det modsatte af indgangen ved logik 0, hvilket får LED 2 til at forblive slukket. Når indgangen får en logisk 0, slukker LED 1 naturligt, men LED 2 lyser nu på grund af det modsatte svar fra porten.

6) BISTABEL LATCH (S.R. FLIP-FLOP)

Dette kredsløb gør brug af et par NAND-porte, der er krydskoblet, for at fremstille et SR-bistabilt låsekredsløb.

Udgangene er markeret som Q og 0. Linjen over Q betyder IKKE. De 2 udgange Q og 0 fungerer som komplementer af hinanden. Betydning, når Q når logisk niveau 1, bliver Q 0, når Q er 0, Q bliver 1.

Kredsløbet kunne aktiveres i begge de 2 stabile tilstande gennem en passende indgangspuls. I det væsentlige giver dette kredsløbet en 'hukommelsesfunktion' og skaber dette til en super let 1 bit (et binært ciffer) datalagringschip.

De to indgange er mærket S og R eller Set and Reset, så dette kredsløb er normalt kendt som S.R.F.F. ( Indstil Reset Flip-Flop ). Dette kredsløb kan være ret nyttigt, og det anvendes i et antal kredsløb.

S-R FLIP-FLOP Rektangulær bølgegenerator

SR Flip-Flop-kredsløbet kan konfigureres til at fungere som en firkantbølgenerator. Hvis F.F. påføres med en sinusbølge, lad os sige fra en 12V AC fra en transformer, med minimum 2 volt peak til peak-område, vil output reagere ved at generere firkantede bølger, der har peak til peak svarende til Vcc-spændingen.

Disse firkantbølger kan forventes at have perfekt firkantet form på grund af IC's ekstremt hurtige stignings- og faldtider. Inverteren eller IKKE gate-udgang, der tilfører R-indgangen, resulterer i at skabe komplementære ON / OFF-indgange på tværs af R- og S-indgangene på kredsløbet.

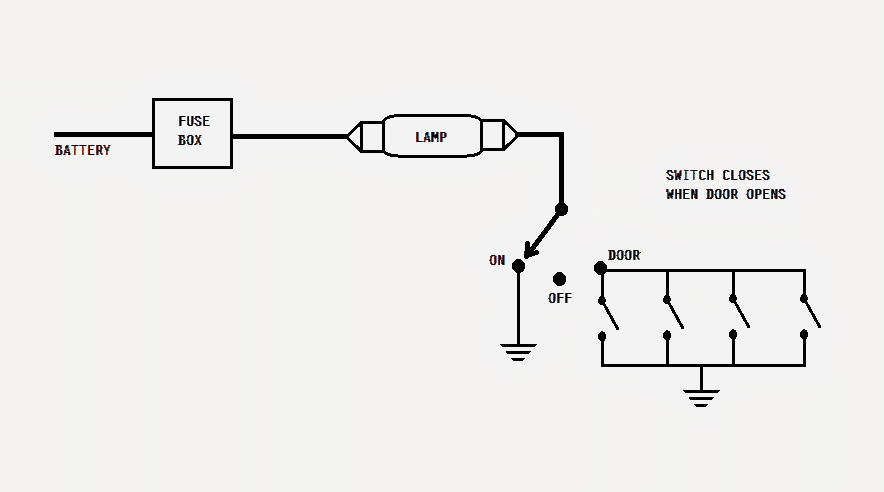

8) ELIMINATOR TIL KONTAKTBUNK

I dette kredsløb kan en SR FLIP-FLOP ses anvendt som en afbryderkontaktudspring eliminator.

Når kontaktkontakter lukkes, følges det normalt af kontakterne, der hopper hurtigt et par gange mellem på grund af mekanisk stress og tryk.

Dette resulterer for det meste i dannelsen af falske spidser, som kan forårsage interferens og uregelmæssig kredsløbsdrift.

Ovenstående kredsløb eliminerer denne mulighed. Når kontakterne oprindeligt lukkes, låser det kredsløbet, og på grund af dette kan interferens fra kontaktspring ikke skabe nogen effekt på flip-flop.

9) MANUEL UR

Dette er en anden variant af kredsløb otte. For at eksperimentere med kredsløb som halv adder eller andre logiske kredsløb er det virkelig nødvendigt at være i stand til at analysere kredsløbet, da det fungerer med en enkelt puls ad gangen. Dette kunne opnås ved anvendelse af et hånddrevet ur.

Når kontakten er slået til, vises en enslig udløser ved udgangen. Kredsløbet fungerer meget godt med en binær tæller. Når kontakten skiftes, tillades kun en enkelt puls ad gangen at ske på grund af anti-bounce-funktionen i kredsløbet, hvilket gør det muligt for optællingen at skride frem en trigger ad gangen.

10) S-R FLIP-FLOP MED HUKOMMELSE

Dette kredsløb er designet ved hjælp af den grundlæggende SR Flip-Flop. Outputtet bestemmes af den sidste input. D angiver DATA-indgangen.

En 'aktiverende' puls bliver nødvendig for at aktivere portene B og C. Q danner det samme logiske niveau som D, hvilket betyder, at dette antager værdien af D og fortsætter med at være i denne tilstand (se billede 14).

Pin-numrene er ikke angivet for enkelheds skyld. Alle 5 porte er 2 input NAND, et par 7400'er er nødvendige. Diagrammet ovenfor angiver kun et logisk kredsløb, men kan dog hurtigt omdannes til et kredsløbsdiagram.

Dette strømline diagrammer, der inkluderer store mængder logiske porte til at arbejde med. Aktiveringssignalet kan være en puls fra det 'tidligere manuelle urkredsløb'.

Kredsløbet fungerer, når der anvendes et 'CLOCK'-signal, dette er normalt et grundlæggende princip, der anvendes i alle computerrelaterede applikationer. De par kredsløb, der er forklaret ovenfor, kan bygges ved hjælp af kun to 7400 IC'er, der er forbundet med hinanden.

11) URKONTROLLERET FLIP-FLOP

Dette er faktisk en anden type SR-flip-flop med hukommelse. Dataindgangen styres med et urssignal, output via SR Flip-Flop reguleres ligeledes af uret.

Denne Flip-Flop fungerer godt som et lagerregister. Uret er faktisk en master controller til input og output bevægelse af impulser.

12) PULSINDIKATOR OG DETEKTOR MED HØJ HASTIGHED

Dette specifikke kredsløb er designet ved hjælp af SR Flip -Flop og er vant til at registrere og vise en bestemt puls i et logisk kredsløb.

Denne puls låser kredsløbet, udgangen påføres derefter inverterinput, hvilket får rød LED til at lyse.

Kredsløbet fortsætter med at være i denne særlige tilstand, indtil det elimineres ved at skifte mellem enkeltpolet afbryder, nulstillingskontakt .

13) 'SNAP!' INDIKATOR

Dette kredsløb viser, hvordan du bruger S-R Flip -Flop på en anden måde. Her to klipklapper er inkorporeret gennem 7 NAND-porte.

Den grundlæggende teori i dette kredsløb er anvendelsen af SR-flip-flops og INHIBIT-linjerne. SI og S2 danner de kontakter, der styrer flip-flops.

I det øjeblik flip-flop låser den pågældende LED tændes, og den komplementære flip-flop forhindres i at låse. Når afbryderne er i form af trykknapper, forårsager nulstilling af knappen nulstilling af kredsløbet. De anvendte dioder er 0A91 eller andre vil gøre som 1N4148.

- Portene A, B, C danner scenen for S1 og LED 1.

- Porte D, E, F udgør scenen for S2 og LED 2.

- Gate G bekræfter, at INHIBIT- og INHIBIT-linjerne fungerer som komplementære par.

14) LAVFREKVENS AUDIO OSCILLATOR

Kredsløbet bruger to NAND-porte, der er forbundet som invertere og krydskoblet for at danne en astabel multivibrator.

Frekvensen kan ændres ved at øge værdien af CI og C2 (lavere frekvens) eller formindske værdien for C1 og C2 (højere frekvens). Som elektrolytkondensatorer Sørg for, at polaritetsforbindelsen er korrekt.

Kredsløb femten, seksten og sytten er også typer af lavfrekvente oscillatorer oprettet fra kredsløb fjorten. Imidlertid er output i disse kredsløb konfigureret til at få lysdioderne til at blinke.

Vi kan se, at alle disse kredsløb ligner hinanden ret tæt. Men i dette kredsløb, hvis en LED anvendes ved udgangen, vil det medføre, at LED'en blinker med en meget hurtig hastighed, som næsten ikke kan skelnes af vores øjne på grund af vedvarende syn. Dette princip bruges i lommeregnere .

15) TWIN LED-FLASHER

Her inkorporerer vi et par NAND-porte til oprettelse af en meget lavfrekvent oscillator. Det design styrer to røde lysdioder hvilket får lysdioderne til at blinke med skiftevis ON OFF.

Kredsløbet fungerer med to NAND-porte, de resterende to porte af IC kan desuden anvendes inden for det samme kredsløb. Forskellige kondensatorværdier kunne bruges til dette andet kredsløb til at generere et alternativt LED-blitzstrin. Kondensatorer med højere værdi får LED'erne til at blinke langsommere og omvendt.

16) ENKEL LED STROBOSKOP

Dette specifikke design er produceret af kredsløb femten, som fungerer som et stroboskop med lav effekt. Kredsløbet er faktisk en høj hastighed LED blinklys . Den røde LED rykker hurtigt, men øjet kæmper for at skelne mellem de specifikke blink (på grund af synets vedholdenhed).

Det kan ikke forventes, at outputlyset er for kraftigt, hvilket betyder, at stroboskopet muligvis kun fungerer bedre, når det er mørkt og ikke om dagen.

De bøjede variable modstande bruges til at variere frekvensen af stroben, således at stroboskop kan let justeres til enhver ønsket strobehastighed.

Stroboskop fungerer meget godt ved højere frekvenser ved at ændre timing-kondensatorværdien. LED'en, der faktisk er en diode, er i stand til let at understøtte meget høje frekvenser. Vi anbefaler, at det muligvis kan anvendes til at tage ekstremt hurtige billeder gennem dette kredsløb.

17) LAV HYSTERESIS SCHMITT TRIGGER

To NAND-portefunktioner kan konfigureres som en Schmitt-udløser at skabe dette specifikke design. For at eksperimentere med dette kredsløb kan du tilpasse R1, som er positioneret til hysterese effekt .

18) FUNDAMENTAL FREQUENCY CRYSTAL OSCILLATOR

Dette kredsløb er rigget som en krystalstyret oscillator. Et par porte er forbundet som invertere, modstandene giver den korrekte mængde forspænding for de tilknyttede porte. Den tredje port er konfigureret som en 'buffer', der forhindrer overbelastning af oscillatorstadiet.

Husk, at når en krystal anvendes i dette bestemte kredsløb, vil den svinge ved sin grundlæggende frekvens, hvilket betyder, at den ikke svinger ved sin harmoniske eller overtonefrekvens.

Hvis kredsløbet fungerer med en betydeligt reduceret frekvens end estimeret, ville det antyde, at krystalfrekvensen fungerer ved en overtone. Med andre ord kan det fungere med flere grundlæggende frekvenser.

19) TO BIT DEKODER

Dette kredsløb udgør en simpel to-bit dekoder. Indgangene er på tværs af linien A og B, output er på tværs af linjen 0, 1, 2, 3.

Input A kan være som logisk 0 eller 1. Input B kan være som logisk 0 eller 1. Hvis A og B begge anvendes med logik 1, bliver dette en binær optælling på 11, der er lig med denier 3 og output på tværs af linje 3 er 'høj'.

Ligeledes A, 0 B, 0 outputlinje 0. Det højeste antal er baseret på mængden af input. Den største tæller ved hjælp af 2 indgange er 22 - 1 = 3. Det kan være muligt at udvide kredsløbet yderligere, for eksempel hvis fire indgange blev anvendt A, B, C og D, i så fald vil det højeste antal være 24 - 1 = 15 og udgangene er fra 0 til 15.

20) FOTOFØLSOMMENDE LATCHING CIRCUIT

Dette er simpelt fotodetektorbaseret kredsløb som anvender et par NAND-porte til at udløse en mørkeaktiveret låsefunktion.

Når det omgivende lys er højere end den indstillede tærskel, forbliver output upåvirket og ved nul logik. Når mørket falder under den indstillede tærskel, skifter potentialet ved indgangen til NAND-porten det til høj logik, hvilket igen fastlåser output til en høj logik permanent.

Fjernelse af dioden fjerner låsefunktionen, og nu fungerer portene sammen med lysresponserne. Det betyder, at output skiftevis går højt og lavt som svar på lysintensiteterne på fotodetektoren.

21) TWIN TONE AUDIO OSCILLATOR

Det næste design viser, hvordan man bygger en a to-tone oscillator ved hjælp af to par NAND-porte. To oscillatortrin er konfigureret ved hjælp af denne NAND-porte, hvor den ene har en høj frekvens ved hjælp af 0,22 µF, mens den anden har en lavfrekvent oscillator 0,47 uF kondensatorer.

Oscillatorerne koblet sammen med hinanden på en måde, så lavfrekvensoscillatoren modulerer højfrekvensoscillatoren. Dette producerer en klingende lydoutput hvilket lyder mere behageligt og interessant end en monotone produceret af en 2-port oscillator.

22) KRYSTALUR OSCILLATOR

Dette er en anden krystalbaseret oscillatorkredsløb til brug med en L.S.I. IC-ur 'chip' til en 50 Hz base. Outputtet justeres til 500 kHz, så for at få 50 Hz skal denne output tilsluttes fire 7490 I.C.'er i kaskademåde. Hver 7490 deler derefter den efterfølgende produktion med 10, hvilket muliggør en samlet opdeling på 10.000.

Dette producerer endelig et output svarende til 50 Hz (500.000 10 ÷ 10 ÷ 10+ 10 = 50). 50 Hz-referencen erhverves normalt fra netledningen, men ved hjælp af dette kredsløb kan uret være uafhængigt af netledningen og også få en lige så præcis 50 Hz tidsbase.

23) SWITCHED OSCILLATOR

Dette kredsløb består af en tonegenerator og et skiftetrin. Tonegeneratoren fungerer non-stop, men uden nogen form for output på ørestykket.

Men så snart en logik 0 vises ved indgangsporten A, vender den port A om til en logik 1. Logikken 1 åbner port B, og lydfrekvensen får lov til at nå ørestykket.

Selvom der er anvendt et lille krystalørestykke her, er det stadig i stand til at generere en utrolig høj lyd. Kredsløbet kan muligvis anvendes som en summer med et elektronisk alarmur I.C.

24) FEJLSPÆNDDETEKTOR

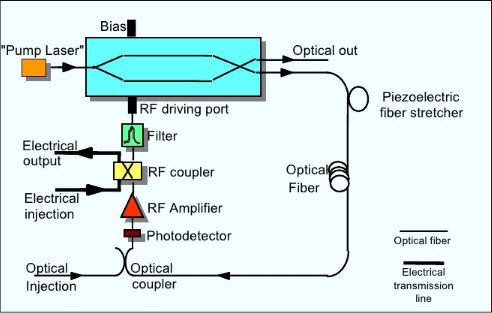

Dette kredsløb er designet til at fungere som en fasedetektor gennem fire NAND-porte. Fasedetektoren analyserer to indgange og genererer en fejlspænding, der er proportional med forskellen mellem de to indgangsfrekvenser.

Detektoroutputtet konverterer signalet gennem et RC-netværk bestående af en 4k7-modstand og en 0,47uF kondensator for at frembringe en DC-fejlspænding. Fasedetektor kredsløbet fungerer ekstremt godt i en P.L.L. (faselåsesløjfe) applikationer.

Ovenstående diagram viser et blokdiagram over en fuld P.L.L. netværk. Fejlspændingen genereret af fasedetektoren forstærkes for at regulere V.C.O.'s multivibratorfrekvens. (spændingsstyret oscillator).

P.L.L. er en utrolig nyttig teknik og er meget effektiv i F.M-demodulation ved 10,7 MHz (radio) eller 6 MHz (TV-lyd) eller til at genoprette 38 KHz subcarrier inden for en stereo-multiplex-dekoder.

25) RF-dæmper

Designet indeholder 4 NAND-porte og anvender dem i en helikoptertilstand til styring af diodebroen.

Diodebroen skifter enten til at muliggøre ledning af RF eller til at blokere RF.

Hvor meget RF der er tilladt gennem kanalen bestemmes i sidste ende af gatesignalet. Dioderne kan være alle siliciumdioder med høj hastighed, eller endda vores egen 1N4148 fungerer (se diagram 32).

26) REFERENCEFREKVENS-SWITCH

Kredsløbet fungerer med fem NAND-porte til udvikling af en 2-frekvensafbryder. Her anvendes et bistabilt låsekredsløb sammen med en enkeltpolet afbryder til neutralisering af afgivelseseffekten fra SPDT-kontakten. Den endelige output kan være f1 eller f2, afhængigt af placeringen af SPDT.

27) TO BIT DATA CHECK

Dette kredsløb fungerer med et computertypekoncept og kan bruges til at lære de grundlæggende logiske funktioner, der opstår i en computer, hvilket fører til fejl.

Kontrol af fejl udføres med tilføjelsen af en supplerende bit (binært ciffer) i 'ord', således at det endelige beløb, der vises i et computers 'ord', konsekvent er ulige eller lige.

Denne teknik kaldes en 'PARITY CHECK'. Kredsløbet undersøger ulige eller lige paritet for 2 bit. Vi kan finde ud af, at designet ligner fasefejldetektor kredsløbet.

28) BINÆR HALVTILHÆNGERKredsløb

Dette kredsløb anvender syv NAND-porte til at skabe en halvt adder kredsløb . A0, B0 udgør de binære cifferindgange. S0, C0 repræsenterer summen og bærelinjerne. For at være i stand til at lære, hvordan disse typer kredsløb fungerer, forestil dig, hvordan grundlæggende matematik uddannes til børn. Du kan henvise til den halve adderer SANDHED Tabel nedenfor.

- 0 og 0 er 0

- I og 0 er jeg sum 1 bærer 0.

- 0 og 1 er jeg sum 1 bærer 0.

- Jeg og jeg er 10 sum 0 bærer 1.

1 0 skal ikke forveksles med 'ti', men det udtages som 'et nul' og symboliserer 1 x 2 ^ 1 + (0 x 2 ^ 0). To hele halvt adderkredsløb ud over en 'ELLER' port giver anledning til et fuldt adderingskredsløb.

I det følgende diagram A1 og B1 er de binære cifre, C0 er bæringen fra det forrige trin, S1 bliver summen, C1 er bæringen til næste trin.

29) NOR GATE HALF ADDER

Dette kredsløb og de næste nedenfor er konfigureret ved kun at bruge NOR-porte. 7402 IC leveres med fire 2-input NOR-porte.

Halvaddern fungerer ved hjælp af fem NOR-porte som vist ovenfor.

Udgangslinjer:

30) NOR GATE FULL ADDER

Dette design viser et fuldt adder-kredsløb ved hjælp af et par NOR-gate-halvaddere sammen med et par ekstra NOR-porte. Kredsløbet fungerer med i alt 12 NOR-porte og behov i alle 3-numre af 7402 I.C.s. Udgangslinjerne er:

Indgangslinjer A, B og K.

K er faktisk det ciffer, der fremføres fra den forrige linje. Vær opmærksom på, at output er implementeret ved hjælp af et par NOR-porte, der er lig med en enkelt ELLER-port. Kredsløbet sætter sig tilbage til to halvføjere ud over en ELLER-port. Vi kan sammenligne dette med vores tidligere diskuterede kredsløb.

31) ENKEL SIGNALINJEKTOR

En grundlæggende signalinjektor som kan bruges til test af lydudstyrsfejl eller andre frekvensrelaterede problemer, kunne oprettes ved hjælp af to NAND-porte. Enheden bruger 4,5V volt gennem 3nor 1,5V AAA celler i serie (se diagram 42).

Et andet signalinjektorkredsløb kan bygges som vist nedenfor ved hjælp af en halv 7413 IC. Dette er mere pålideligt, da det anvender en Schmitt-udløser som en multivibrator

32) ENKEL FORSTÆRKER

Et par NAND-porte designet som invertere kunne kobles i serie til udvikling af en enkel lydforstærker . 4k7-modstanden bruges til at generere en negativ feedback i kredsløbet, selvom dette ikke hjælper med at eliminere alle forvrængninger.

Forstærkerudgangen kan bruges med en hvilken som helst højttaler, der er klassificeret til 25 til 80 ohm. En 8 Ohm højttaler kan afprøves, selvom det kan få IC til at blive meget varmere.

Lavere værdier for 4k7 kunne også forsøges, men det kan føre til lavere lydstyrke ved output.

33) UR MED LAV HASTIGHED

Her bruges en Schmitt-trigger i forbindelse med en lavfrekvent oscillator, RC-værdier bestemmer frekvensen af kredsløbet. Urfrekvensen er ca. 1 Hz eller 1 puls pr. Sekund.

34) NAND Gate Touch Switch Circuit

Bare et par NAND kan bruges til at lave en berøringsbetjent relæ kontrolafbryderen som vist ovenfor. Grundkonfigurationen er den samme som RS-flip-flip forklaret tidligere, hvilket udløser dens output som reaktion på de to berøringspads ved deres indgange. Berøring af berøringspladen 1 får udgangen til at gå højt ved at aktivere relædriverfasen, så den tilsluttede belastning tændes.

Når den nederste berøringsplade berøres, nulstiller den udgangen, hvilket drejer den tilbage til logisk nul. Denne handling slukker for relædriver og belastningen.

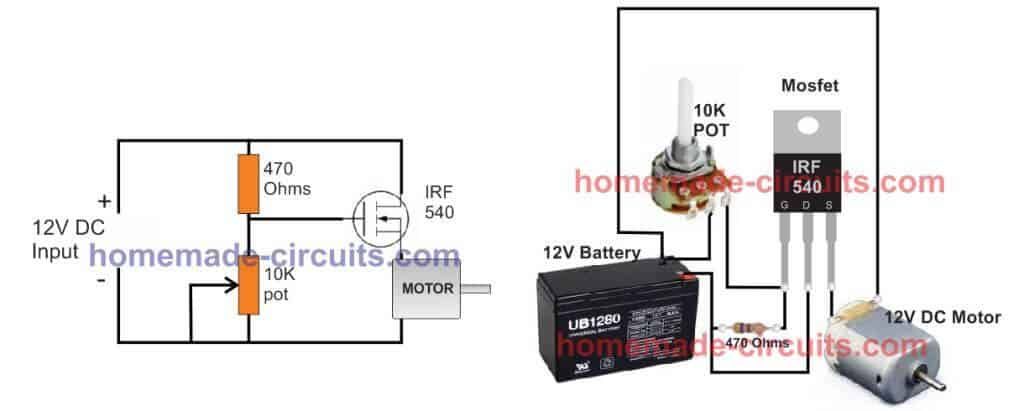

35) PWM-kontrol ved hjælp af en enkelt NAND-port

NAND-porte kan også bruges til at opnå en effektiv PWM-styret output fra minimum til maksimum.

NAND-porten vist på venstre side gør to ting, den genererer den krævede frekvens og giver også brugeren mulighed for at ændre ON-tiden og OFF-tiden for frekvensimpulserne separat via to dioder, der styrer kondensatorens opladning og afladningstid C1.

Dioderne isolerer de to parametre og muliggør opladning og afladningskontrol af C1 separat via pottejusteringerne.

Dette tillader igen output PWM at blive styret diskret gennem pottejusteringerne. Denne opsætning kan bruges til at kontrollere jævnstrømsmotorhastighed nøjagtigt med minimale komponenter.

Spændingsdobler ved hjælp af NAND-porte

NAND-porte kan også anvendes til effektivisering dobbeltkredsløb til spænding som vist ovenfor. Nand N1 er konfigureret som en urgenerator eller frekvensgenerator. Frekvensen forstærkes og bufres gennem de resterende 3 Nand-porte, der er kablet parallelt.

Outputtet føres derefter til et diode-kondensator-spændingsdobler- eller multiplikator-trin for endelig at opnå 2X spændingsniveauændring ved udgangen. Her fordobles 5V til 10V, men andet spændingsniveau op til 15V maksimalt og bruges også til at få den krævede spændingsmultiplikation.

220V inverter ved hjælp af NAND-porte

Hvis du tænker, at NAND gate kun kan bruges til at lave lavspændingskredsløb, kan du tage fejl. En enkelt 4011 IC kan hurtigt anvendes til at fremstille en kraftfuld 12V til 220V inverter som vist ovenfor.

N1-port sammen med RC-elementer danner den grundlæggende 50 Hz-oscillator. RC-dele skal vælges passende for at opnå den tilsigtede 50 Hz eller 60 Hz frekvens.

N2 til N4 er arrangeret som buffere og invertere, således at den endelige udgang ved transistorenes baser producerer skiftevis strøm for den krævede push pull-handling på transformeren via transistorsamlerne.

Piezo Summer

Da NAND-porte kan konfigureres som effektive oscillatorer, er de relaterede applikationer enorme. En af disse er piezo summer , som kan bygges ved hjælp af en enkelt 4011 IC.

NAND-gateoscillatorer kan tilpasses til implementering af mange forskellige kredsløbsidéer. Dette indlæg er endnu ikke afsluttet og vil blive opdateret med flere NAND gate-baserede designs efter tid. Hvis du har noget interessant relateret til NAND gate kredsløb, så lad os vide, at din feedback vil blive meget værdsat.

Forrige: Rød LED LightStim Circuit til fjernelse af ansigtsrynker Næste: Easy Two Transistor Projects for School Students