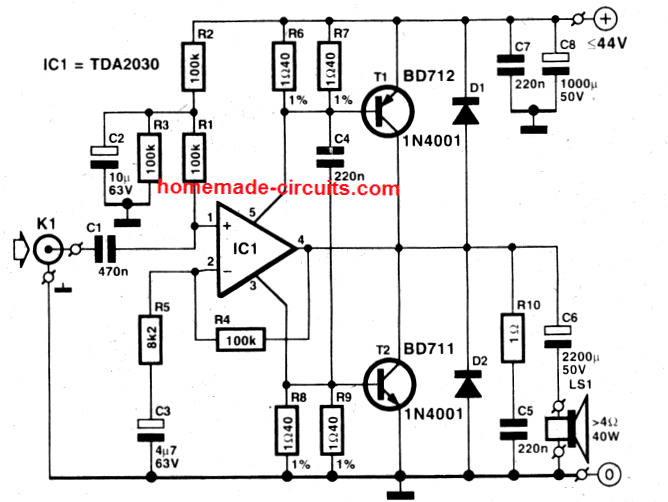

I dette indlæg lærer vi, hvordan man bygger NOT, AND, NAND, OR og NOR logiske porte ved hjælp af diskrete transistorer. Den største fordel ved at bruge transistorlogiske porte er, at de kan fungere selv med spændinger så lave som 1,5 V.

I nogle elektroniske applikationer kan den tilgængelige spænding være utilstrækkelig til at forsyne TTL eller endda CMOS IC'er. Dette gælder især for gadgets, der kører på batterier. Ingen tvivl om, du har altid 3-volt logisk IC mulighed. Disse er dog ikke altid let tilgængelige for entusiasten eller eksperimentatoren, og de fungerer ikke under deres definerede spændingsspecifikationer (generelt under 2,5 volt DC).

Desuden er der muligvis kun plads til et enkelt 1,5 volt batteri i en batteridrevet applikation. Nå, hvad skal du så gøre? Som regel IC logiske porte kunne erstattes af transistoriserede logiske porte. For hver bestemt logisk gate kræves der generelt kun et par transistorer, og for en typisk NOT gate inverter-logik kræves der kun en transistor.

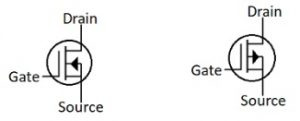

FET'er kontra bipolær transistor

Felteffekttransistorer (FET'er) vs bipolære transistorer : Hvilken er den bedre mulighed for lavspændingslogiske kredsløb? Et fantastisk træk ved FAKTA er, at deres 'på' modstand er utrolig lav. Derudover har de brug for meget lav gate-turn-on strøm.

De har dog en begrænsning i ekstremt lavspændingsapplikationer. Typisk er gatespændingsgrænsen en volt eller deromkring. Ydermere kan den tilgængelige spænding falde under FET'ens optimale arbejdsområde, hvis en strømbegrænsende eller pull-down modstand er forbundet til porten.

Omvendt har bipolære koblingstransistorer en fordel i ekstremt lav spænding, enkeltbatteriapplikationer, da de kun behøver 0,6 til 0,7 volt for at tænde.

Desuden er størstedelen af almindelige FET'er, som normalt sælges i boblepakker i din nærmeste elektronikbutik, ofte dyrere end bipolære transistorer. Også en bulkpakke af bipolære transistorer kunne generelt købes til prisen for et par FET'er.

FET-håndtering kræver væsentlig mere omhu end bipolær transistorhåndtering. Elektrostatisk og generel eksperimentel misbrug gør FET'er særligt tilbøjelige til at blive beskadiget. Brændte komponenter kan ødelægge en fornøjelig, kreativ aften med eksperimentering eller innovation, for ikke at glemme den følelsesmæssige smerte ved fejlretning.

Grundlæggende om at skifte transistorer

De logiske kredsløbseksempler, der er forklaret i denne artikel, gør brug af bipolære NPN-transistorer, da de er overkommelige og ikke behøver speciel håndtering. For at undgå at beskadige enheden eller de dele, der understøtter den, skal der træffes passende sikkerhedsforanstaltninger, før du tilslutter dit kredsløb.

Selvom vores kredsløb overvejende er centreret om Bipolar Junction Transistor (BJT'er), kunne de lige så godt have været konstrueret ved hjælp af FET-teknologi.

Det grundlæggende switch-kredsløb er en simpel transistorapplikation, som er en af de nemmeste designs.

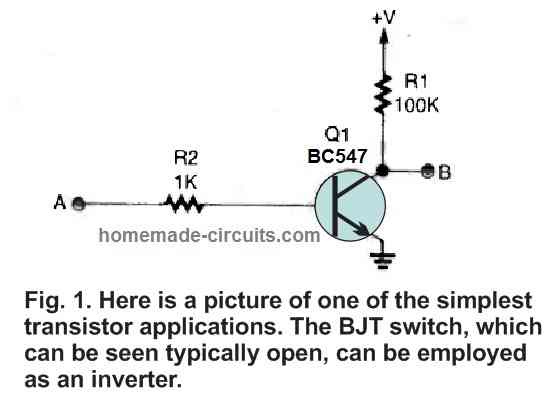

Fremstilling af en NOT-port med en enkelt transistor

Et skematisk billede af transistorkontakten er vist i figur 1. Afhængigt af, hvordan den er implementeret i en bestemt applikation, kan kontakten ses som enten holdt lav eller normalt åben.

En simpel NOT gate inverter logisk gate kan skabes af det ligefremme koblingskredsløb vist i fig. 1 (hvor punkt A er input). En NOT-gate fungerer på en sådan måde, at hvis der ikke leveres DC-forspænding til transistorens basis (punkt A; Q1), vil den forblive afbrudt, hvilket resulterer i et højt eller logisk 1 (lig med V+-niveau) ved udgangen ( punkt B).

Imidlertid aktiveres transistoren, når den korrekte forspænding er tilvejebragt til bunden af Q1, og skubber kredsløbets output lavt eller til logisk 0 (næsten lig med nul potentiale). Transistoren, betegnet Q1, er en bipolær transistor til generelle formål, eller en BC547, som typisk bruges i laveffektskoblings- og forstærkerapplikationer.

Enhver transistor, der svarer til det (såsom 2N2222, 2N4401 osv.) ville fungere. R1 og R2's værdier blev valgt for at skabe et kompromis mellem lavt strømforbrug og kompatibilitet. I alle designs er modstandene alle 1/4 watt, 5% enheder.

Forsyningsspændingen er justerbar mellem 1,4 og 6 volt DC. Bemærk, at kredsløbet kan fungere som en buffer, når belastningsmodstanden og udgangsforbindelsen flyttes til transistorens emitter.

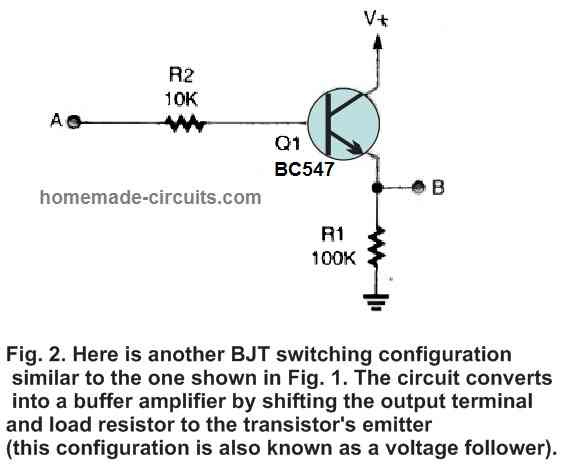

Fremstilling af en bufferport ved hjælp af en enkelt BC547 BJT

En spændingsfølger, eller bufferforstærker, er en type logisk koblingskonfiguration, der er identisk med den, der er vist i figur 2. Det skal bemærkes, at belastningsmodstanden og udgangsterminalen er blevet forskudt fra transistorens kollektor til dens emitter i dette kredsløb, som er den primære forskel mellem dette design og det, der er vist i fig.

Transistorens funktion kan også 'vendes' ved at flytte belastningsmodstanden og udgangsterminalen til den anden ende af BJT'en.

Med andre ord, når der ikke er tilvejebragt nogen forspænding til kredsløbets input, forbliver outputtet af kredsløbet lavt; men når en forspænding af tilstrækkelig spænding leveres til kredsløbets input, bliver kredsløbets output høj. (Det er præcis det modsatte af, hvad der sker i det tidligere kredsløb.)

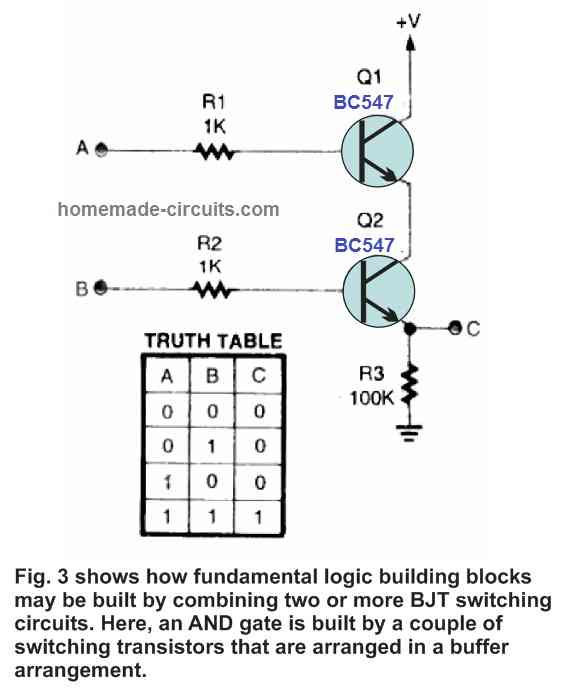

Design af logiske porte med to indgange ved hjælp af transistorer

OG Gate ved hjælp af to transistorer

Figur 3 illustrerer, hvordan en grundlæggende AND-gate med to indgange kan skabes ved brug af et par buffere, sammen med sandhedstabellen for denne gate. Sandhedstabellen illustrerer, hvad outputresultaterne ville være for hvert enkelt sæt af input. Punkterne A og B bruges som kredsløbets input, og punkt C tjener som kredsløbets output.

Det er vigtigt at bemærke fra sandhedstabellen, at kun ét sæt inputparametre resulterer i et logisk-højt outputsignal, hvorimod alle andre inputkombinationer resulterer i et logisk-lavt output. Outputtet fra AND-porten i figur 3 forbliver lidt under V+, når det først bliver højt.

Dette sker på grund af spændingsfaldet mellem de to transistorer (Q1 og Q2).

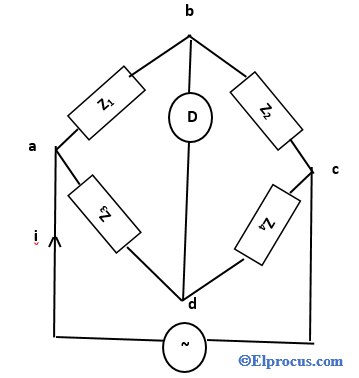

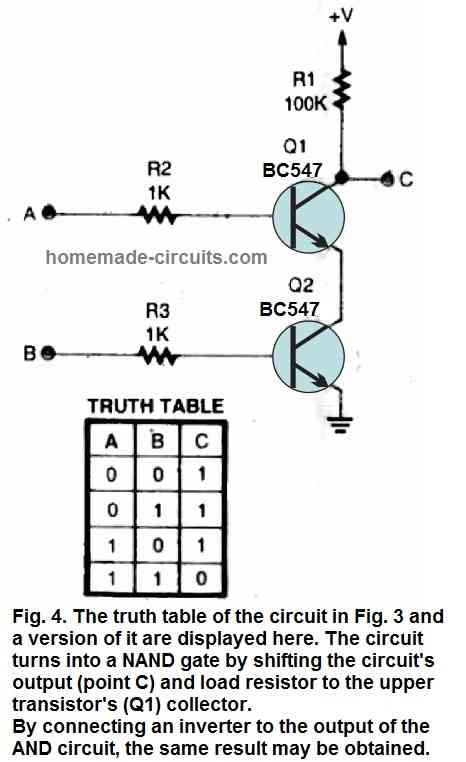

NAND Gate ved hjælp af to transistorer

En anden variant af kredsløbet i figur 3 og tilhørende sandhedstabel er vist i figur 4. Kredsløbet bliver til en NAND-gate ved at flytte output (punkt C) og udgangsmodstand til den øvre transistorens (Q1) kollektor.

Da både Q1 og Q2 skal tændes for at trække den lave side af R1 til jord, er spændingstabet ved udgang C ubetydeligt.

Hvis transistoren OG- eller transistorens NAND-porte har brug for mere end to indgange, kan flere transistorer godt forbindes i de viste designs for at give tre, fire osv. indgangs- OG eller NAND-porte.

For at kompensere for de enkelte transistors spændingstab bør V+ dog øges tilsvarende.

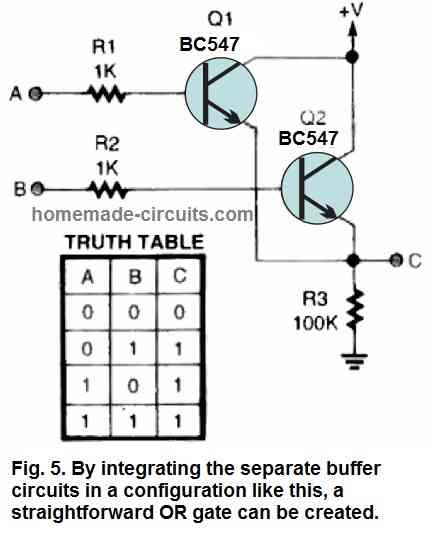

ELLER Gate ved hjælp af to transistorer

En anden form for logisk kredsløb med to indgange kan ses i figur 5 sammen med OR-gatekredsløbets sandhedstabel.

Udgangen af kredsløbet er høj, når enten indgang A eller indgang B skubbes højt, men på grund af kaskadetransistorerne er spændingsfaldet over 0,5 volt. Endnu en gang indikerer de viste tal, at der er nok spænding og strøm til at betjene den efterfølgende transistorgate.

NOR-port ved hjælp af to transistorer

Figur 6 viser den næste port på vores liste, en NOR-port med to indgange, sammen med dens sandhedstabel. På samme måde som AND- og NAND-porte reagerer på hinanden, gør OR- og NOR-kredsløb det samme.

Hver af de viste porte er i stand til at levere nok drev til at aktivere mindst en eller flere tilstødende transistorporte.

Transistor Logic Gate-applikationer

Hvad gør du med de ovenfor forklarede digitale kredsløb, som du nu besidder? Alt, hvad du kan opnå med konventionelle TTL- eller CMOS-porte, men uden at bekymre dig om forsyningsspændingsbegrænsningerne. Her er et par anvendelser af transistor-logiske porte i aktion.

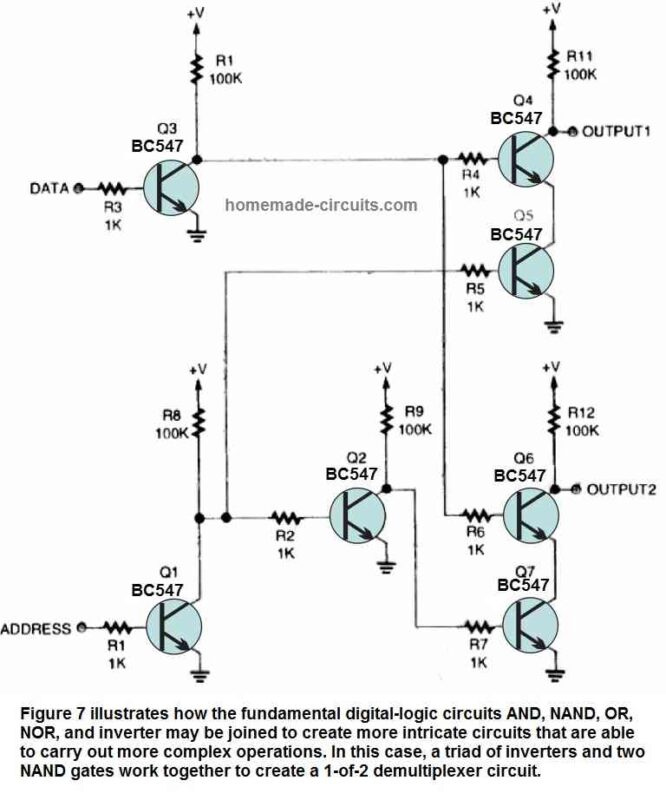

Demultiplekser kredsløb

En 1-af-2 demultiplekser med tre IKKE-porte og to NAND-kredsløb ses i figur 7. Det passende output vælges ved hjælp af en-bit 'adresseinput', som kan være enten OUTPUT1 eller OUTPUT2, mens kørselsinformationen anvendes til kredsløbet ved hjælp af DATA-indgangen.

Kredsløbet fungerer mest effektivt, når datahastigheden holdes under 10 kHz. Kredsløbets funktionalitet er ligetil. DATA-indgangen forsynes med det nødvendige signal, som tænder for Q3 og inverterer de indkommende data på Q3's opsamler.

Udgangen af Q1 drives højt, hvis ADRESSE-indgangen er lav (jordet eller intet signal tilvejebragt). Ved Q1's opsamler er det høje output opdelt i to baner. I den første sti tilføres Q1's output til Q5's base (et af benene på en NAND-port med to indgange), og tænder for det og 'aktiverer' derfor NAND-porten, der består af Q4 og Q5.

I den anden vej tilføres Q1's høje output samtidigt til indgangen på en anden IKKE-port (Q2). Efter at have gennemgået en dobbelt inversion, bliver Q2's output lav. Denne lave forsynes med Q7's base (en terminal på en anden NAND-gate, der består af Q6 og Q7), hvilket afbryder NAND-kredsløbet.

Enhver information eller signal, der påføres DATA-indgangen, ankommer til OUTPUT1 under disse omstændigheder. Alternativt vendes situationen, hvis der gives et højt signal til ADRESSE-indgangen. Det betyder, at enhver information, der leveres til kredsløbet, vises ved OUTPUT2, da Q4/Q5 NAND-porten er deaktiveret, og Q6/Q7 NAND-porten er aktiveret.

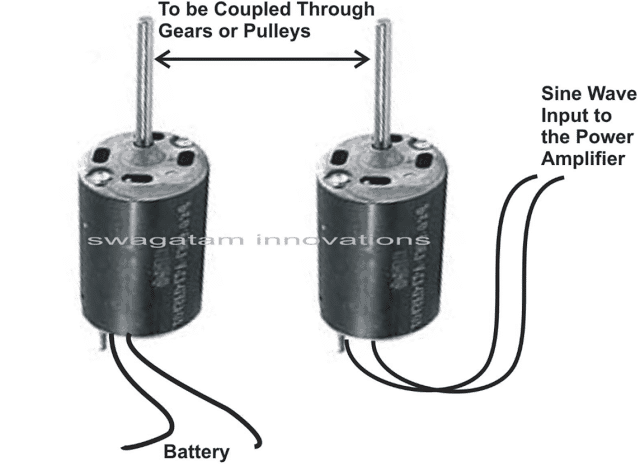

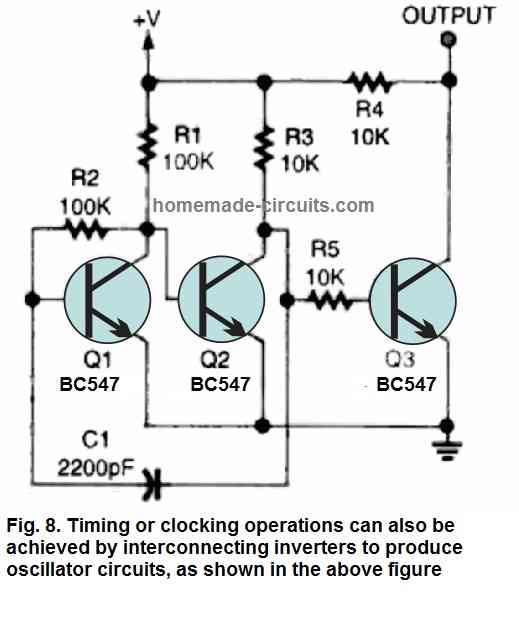

Oscillatorkredsløb (urgenerator)

Vores næste transistorlogiske gate-applikation, illustreret i fig. 8, er en grundlæggende clockgenerator (også kendt som en oscillator) lavet af tre almindelige NOT-gate-invertere (hvoraf den ene er forspændt ved hjælp af en tilbagekoblingsmodstand, R2, som sætter den i det analoge område).

For at udligne outputtet er der inkluderet en tredje NOT-gate (Q3), der leverer komplementet til oscillatorudgangen. C1-værdien kan øges eller sænkes for at ændre kredsløbets driftsfrekvens. Udgangsbølgeformen har en frekvens på omkring 7 kHz med V+ ved 1,5 volt DC, ved brug af de angivne komponentværdier.

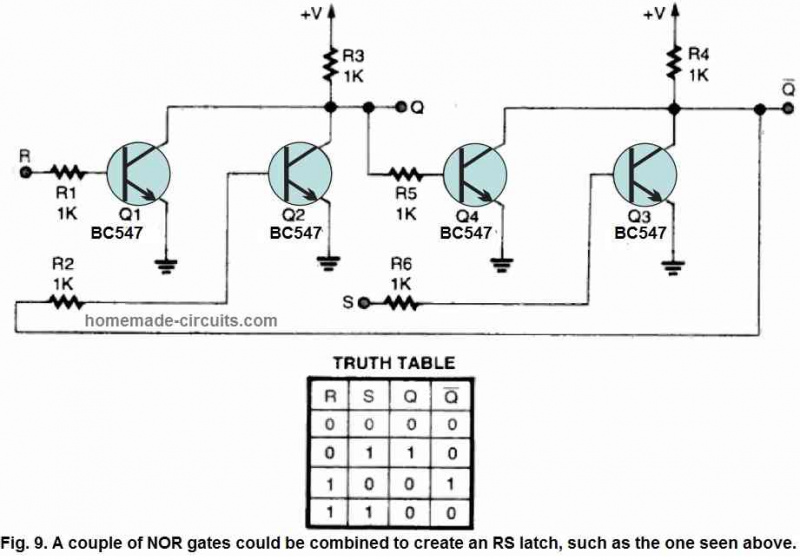

RS låsekredsløb

Fig. 9 viser vores endelige anvendelseskredsløb, en RS-lås bestående af to NOR-porte. For at sikre et sundt udgangsdrev ved Q- og Q-udgangene er modstande R3 og R4 justeret til 1k ohm.

RS-låsens sandhedstabel vises sammen med det skematiske design. Dette er blot nogle få illustrationer af de adskillige pålidelige, lavspændings-, digitale, logiske gate-kredsløb, der kan skabes ved hjælp af individuelle transistorer.

Kredsløb, der bruger transistoriseret logik, har brug for for mange dele

Mange problemer kan løses ved hjælp af alle disse lavspændingstransistoriserede logiske kredsløb. Anvendelse af for mange af disse transistoriserede porte kan dog føre til nye problemer.

Antallet af transistorer og modstande kan blive ret stort, hvis den applikation, du bygger, indeholder en stor mængde porte, der optager værdifuld plads.

Brug af transistor-arrays (mange transistorer indesluttet i plastik) og SIP-modstande (Single Inline Package) i stedet for individuelle enheder er en måde at løse dette problem på.

Ovenstående tilgang kan spare et ton plads på et print, samtidig med at ydeevnen bibeholdes svarende til deres ækvivalenter i fuld størrelse. Transistor-arrays tilbydes i overflademonteret, 14-bens gennemgående hul og quad-emballage.

For de fleste kredsløb kan blandingstransistortyper være ganske acceptabelt.

Ikke desto mindre er det tilrådeligt, at eksperimentatoren arbejder med en enkelt type transistor til at bygge de transistoriserede logiske kredsløb (hvilket betyder, at hvis du opretter en sektion af en gate ved hjælp af BC547, så prøv at bruge den samme BJT til at lave de andre resterende porte også).

Begrundelsen er, at forskellige transistorvarianter kan have noget forskellige egenskaber og derfor kan opføre sig anderledes.

For eksempel, for nogle transistorer kan base switch-ON-grænsen være større eller mindre end en anden, eller man kunne have en samlet strømforstærkning, der er en smule højere eller lavere.

På den anden side kan omkostningerne ved at købe en bulkboks af en enkelt type transistor også være lavere. Ydeevnen af dine kredsløb vil forbedres, hvis dine logiske porte er bygget ved hjælp af matchende transistorer, og projektet i sin helhed vil i sidste ende være mere givende.