Forøgelse af programmets eksekveringshastighed øger følgelig hastigheden på processoren. Der er mange måder opfundet, både hardwareimplementering og softwarearkitektur, for at øge udførelseshastigheden. Det blev observeret, at ved at udføre instruktioner samtidigt kan den tid, der kræves til udførelse, reduceres. Begrebet parallelitet i programmering blev foreslået. Ifølge dette kan mere end en instruktion udføres pr. Urcyklus. Dette koncept kan praktiseres af en programmør gennem forskellige teknikker såsom Rørledning, flere udførelsesenheder og flere kerner . Blandt alle disse paralleliseringsmetoder praktiseres rørledning mest. Så hvordan kan en instruktion udføres i pipelining-metoden? Hvordan øger det eksekveringshastigheden?

Hvad er rørledning?

For at forstå begrebet pipelining, lad os se på rodniveauet for, hvordan programmet udføres. Instruktion er den mindste eksekveringspakke i et program. Hver instruktion indeholder en eller flere operationer. Enkle skalarprocessorer udfører en eller flere instruktioner pr. Urcyklus, hvor hver instruktion kun indeholder en operation. Instruktioner udføres som en sekvens af faser for at producere de forventede resultater. Denne sekvens er angivet nedenfor

Instruktionsudførelsessekvens

- IF: Henter instruktionen i instruktionsregistret.

- ID: Instruktionsafkodning, afkoder instruktionen til opkoden.

- AG: Adressegenerator, genererer adressen.

- DF: Data Fetch, henter operanderne i dataregistret.

- EX: Udførelse, udfører den angivne operation.

- WB: Skriv tilbage, skriver resultatet tilbage til registret.

Ikke alle instruktioner kræver alle ovenstående trin, men de fleste gør det. Disse trin bruger forskellige hardwarefunktioner. I rørledningen udføres disse forskellige faser samtidigt. I rørledningen betragtes disse faser som uafhængige mellem forskellige operationer og kan overlappes. Således kan flere operationer udføres samtidigt, hvor hver operation er i sin egen uafhængige fase.

Instruktionsrørledning

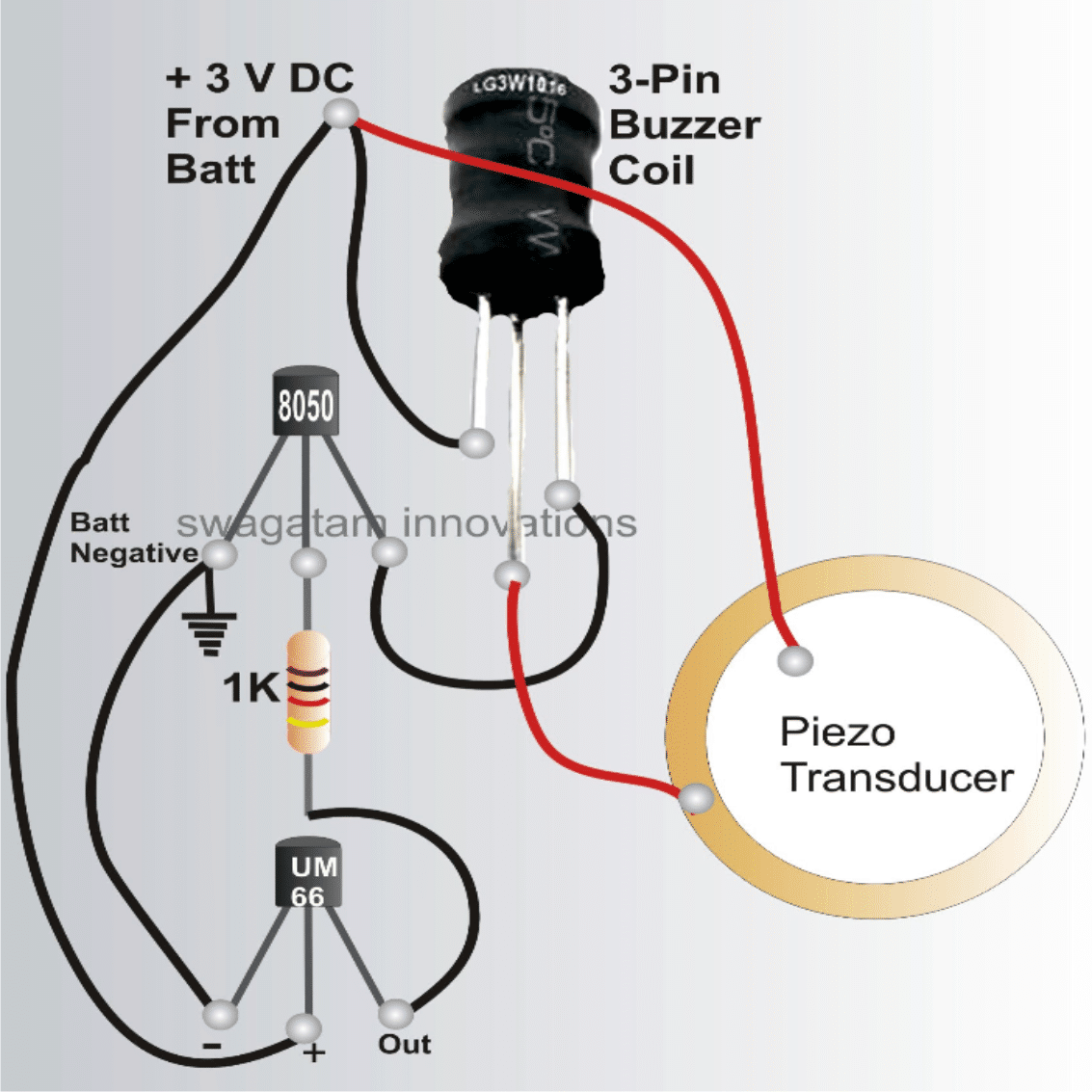

Lad os se, hvordan instruktionerne behandles i rørledningen. Dette kan let forstås ved nedenstående diagram.

Instruktionsrørledning

Antag, at instruktionerne er uafhængige. I en simpel rørledningsprocessor er der på et givet tidspunkt kun en operation i hver fase. Den indledende fase er IF-fasen. Så ved den første urcyklus hentes en operation. Når den næste urpuls ankommer, går den første operation ind i ID-fasen og efterlader IF-fasen tom. Nu tildeles denne tomme fase til den næste operation. Så under den anden urpuls er den første operation i ID-fasen, og den anden operation er i IF-fasen.

I den tredje cyklus vil den første operation være i AG-fase, den anden operation vil være i ID-fasen, og den tredje operation vil være i IF-fasen. På denne måde udføres instruktioner samtidigt, og efter seks cyklusser udsender processoren en fuldstændig udført instruktion pr. Urcyklus.

Er denne instruktion udført sekventielt, oprindeligt skal den første instruktion gennemgå alle faser, så vil den næste instruktion blive hentet? Så til udførelse af hver instruktion ville processoren kræve seks urcyklusser. Men i en pipelined processor, da udførelsen af instruktioner finder sted samtidigt, er det kun den indledende instruktion, der kræver seks cyklusser, og alle de resterende instruktioner udføres som en pr. Cyklus, hvorved udførelsestiden reduceres og processorens hastighed øges.

Rørledningsarkitektur

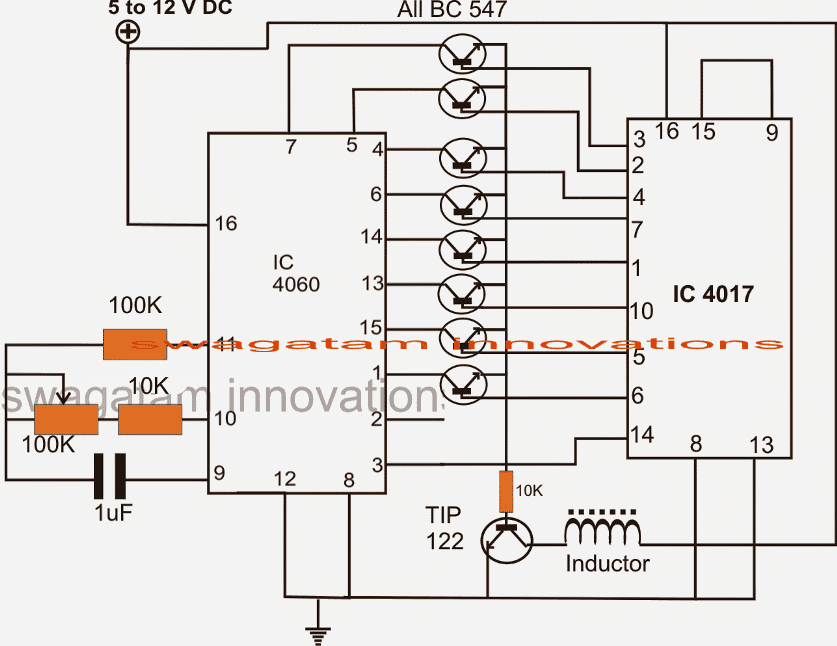

Parallelisme kan opnås med hardware-, compiler- og softwareteknikker. At udnytte begrebet pipelining i computerarkitektur mange processorenheder er sammenkoblet og fungerer samtidigt. I pipelined processorarkitektur er der adskilte processorenheder til rådighed for heltal og flydende instruktioner. Mens der i sekventiel arkitektur tilvejebringes en enkelt funktionel enhed.

Rørledningsprocessorenhed

Ved statisk rørledning skal processoren føre instruktionen gennem alle faser af rørledningen uanset instruktionskravet. I en dynamisk rørledningsprocessor kan en instruktion omgå faserne afhængigt af dens krav, men skal bevæge sig i rækkefølge. I en kompleks dynamisk rørledningsprocessor kan instruktionen omgå faserne såvel som vælge faserne ude af rækkefølge.

Rørledning i RISC-processorer

Den mest populære RISC-arkitektur ARM-processor følger 3-trins og 5-trins rørledning. I 3-trins pipelining er trinene: Fetch, Decode og Execute. Denne pipelining har 3 cyklenser latenstid, da en individuel instruktion tager 3 urcyklusser at gennemføre.

ARM 3-trins rørledning

For korrekt implementering af pipelining bør hardware arkitektur også opgraderes. Hardwaren til 3-trins rørledning inkluderer en registerbank, ALU, Barrel shifter, Adressegenerator, en inkrementer, Instruktions dekoder og dataregistre.

ARM 3 Stage Pipelining Datapath

I 5 faser pipelining er trinene: Fetch, Decode, Execute, Buffer / data og Write back.

Risiko for rørledning

I et typisk computerprogram er der foruden enkle instruktioner greninstruktioner, afbryde operationer, læse og skrive instruktioner. Rørledning er ikke egnet til alle slags instruktioner. Når nogle instruktioner udføres under rørledning, kan de stoppe rørledningen eller skylle den helt. Denne type problemer forårsaget under rørledning kaldes rørledningsrisici.

I de fleste computerprogrammer bruges resultatet af den ene instruktion som en operand af den anden instruktion. Når sådanne instruktioner udføres i rørledning, opstår nedbrydning, da resultatet af den første instruktion ikke er tilgængelig, når instruktion to begynder at samle operander. Så instruktion to skal stoppe, indtil instruktion en udføres, og resultatet genereres. Denne type fare kaldes Read-after-write pipelining hazard.

Læs efter skrivning Rørledningsfare

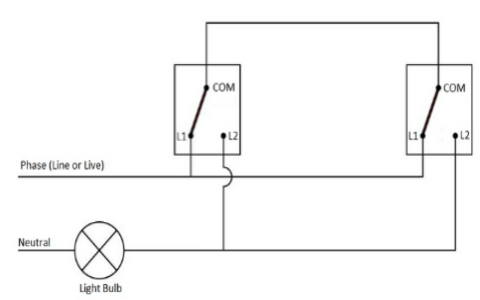

Udførelse af filialinstruktioner medfører også en rørledningsfare. Filialinstruktioner under udførelse i rørledning påvirker hentningsstadierne i de næste instruktioner.

Rørledet grenadfærd

Fordele ved rørledning

- Instruktionsgennemstrømningen øges.

- Stigning i antallet af rørledningsfaser øger antallet af instruktioner, der udføres samtidigt.

- Hurtigere ALU kan designes, når der anvendes rørledning.

- Pipelined CPU fungerer ved højere urfrekvenser end RAM.

- Rørledning øger CPU's samlede ydeevne.

Ulemper ved rørledning

- Design af den pipelined processor er kompleks.

- Instruktions latenstid øges i pipelined processorer.

- Gennemstrømningen af en pipelined processor er vanskelig at forudsige.

- Jo længere rørledningen er, desto værre er problemet med fare for filialinstruktioner.

Pipelining gavner alle instruktionerne, der følger en lignende sekvens af trin til udførelse. Processorer, der har komplekse instruktioner, hvor hver instruktion opfører sig forskelligt fra den anden, er svære at pipeline. Processorer har rimelige redskaber med 3 eller 5 trin i rørledningen, da farer forbundet med den øges, når rørledningsdybden øges. Navngiv nogle af de rørledte processorer med deres pipeline-fase?