Det faselåst sløjfe er en af de grundlæggende blokke i moderne elektroniske systemer. Det bruges generelt i multimedie, kommunikation og i mange andre applikationer. Der er to forskellige typer PLL'er - lineære og ikke-lineære. Det ikke-lineære er vanskeligt og kompliceret at designe i den virkelige verden, men den lineære kontrolteori er godt modelleret i analoge PLL'er. PLL har bevist, at en lineær model er tilstrækkelig til de fleste elektroniske applikationer.

Hvad er en faselåst sløjfe?

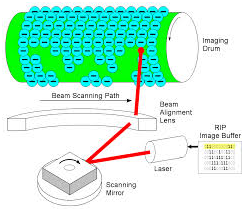

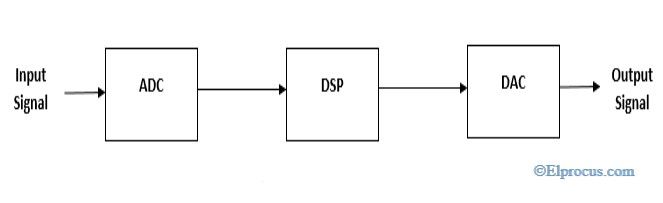

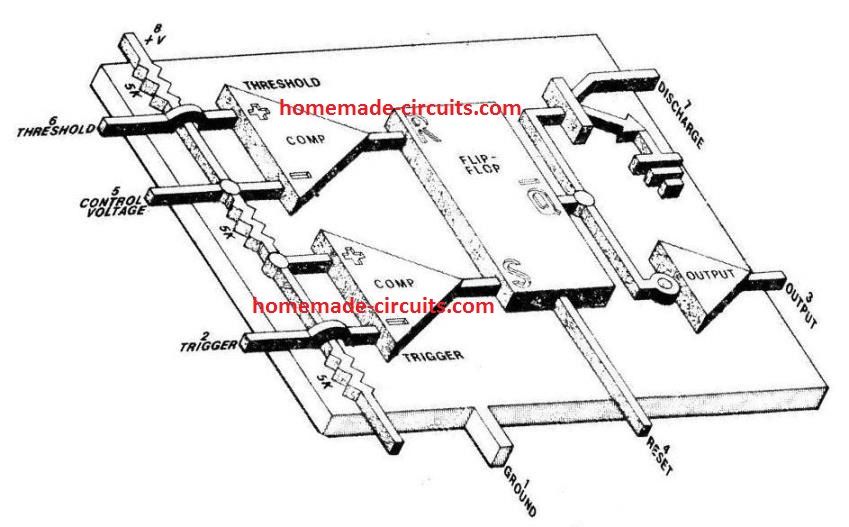

En faselåst sløjfe består af en fasedetektor og en spændingsstyret oscillator. Udgangen fra fasedetektoren er indgangen til den spændingsstyrede oscillator (VCO), og udgangen fra VCO er forbundet til en af indgangene til en fasedetektor, som er vist nedenfor i det grundlæggende blokdiagram. Når disse to enheder tilføres hinanden, dannes sløjfen.

GRUNDLÆGGENDE DIAGRAM FASELÅSET LØKKE

Blokdiagram og arbejdsprincip for PLL

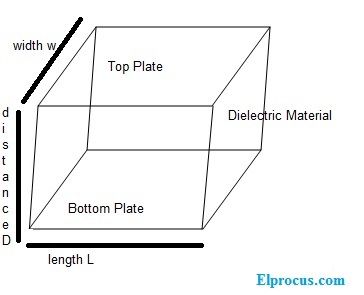

Den faselåste sløjfe består af en fasedetektor, a spændingsstyret oscillator og mellem dem er et lavpasfilter fastgjort. Indgangssignalet 'Vi' med en indgangsfrekvens 'Fi' indrømmes af en fasedetektor. Dybest set er fasedetektoren en komparator der sammenligner indgangsfrekvensen fi gennem feedbackfrekvensen fo. Udgangen fra fasedetektoren er (fi + fo), som er en jævnstrømsspænding. Uden af fasedetektoren, dvs. DC-spænding indføres i lavpasfilteret (LPF), den fjerner højfrekvent støj og producerer et konstant DC-niveau, dvs. Fi-Fo. Vf er også en dynamisk egenskab ved PLL.

PLL-blokdiagram

Outputtet fra lavpasfilteret, dvs. DC-niveauet videregives til VCO. Indgangssignalet er direkte proportionalt med udgangsfrekvensen for VCO (fo). Indgangs- og udgangsfrekvenserne sammenlignes og justeres gennem feedback-sløjfen, indtil udgangsfrekvensen er lig med indgangsfrekvensen. Derfor fungerer PLL som frit kørsel, capture og faselås.

Når der ikke er anvendt nogen indgangsspænding, siges det at være et fritløbende trin. Så snart indgangsfrekvensen, der anvendes på VOC'en, ændres og producerer en udgangsfrekvens til sammenligning, kaldes det et opsamlingsstadium. Nedenstående figur viser blokdiagrammet for PLL.

Faselåst sløjfedetektor

Den faselåste sløjfedetektor sammenligner indgangsfrekvensen og udgangsfrekvensen for VCO for at producere en jævnstrømsspænding, der er direkte proportional med faseadskillelsen mellem de to frekvenser. De analoge og digitale signaler bruges i den faselåste sløjfe. Det meste af den monolitiske PLL integrerede kredsløb brug en analog fasedetektor, og størstedelen af fasedetektorer er af den digitale type. Et dobbelt afbalanceret blandingskredsløb anvendes almindeligvis i analoge fasedetektorer. Nogle almindelige fasedetektorer er angivet nedenfor:

Eksklusiv ELLER fasedetektor

En eksklusiv ELLER fasedetektor er CMOS IC 4070-typen. Indgangs- og udgangsfrekvenserne påføres EX ELLER fasedetektoren. For at opnå output højt skal mindst en input være lav, og de andre betingelser for output er lave, hvilket er vist i nedenstående sandhedstabel. Lad os overveje bølgeformen, input og output frekvenser, dvs. fi og fo har en faseforskel på 0 grader. Derefter vil komparatorens DC-udgangsspænding være en funktion af faseforskellen mellem de to indgange.

| være | fo | Vdc |

lav | lav | lav |

lav | høj | høj |

høj | Lav | høj |

Høj | Høj | lav |

Faseforskelens funktioner mellem fi og fo er som vist i grafen for jævnstrømsudgangsspænding. Hvis fasedetektoren er 180 grader, er udgangsspændingen maksimal. Hvis både indgangs- og udgangsfrekvenserne er firkantede, anvendes denne type fasedetektorer.

Eksklusiv ELLER fasedetektor

Edge Trigger Phase Detector

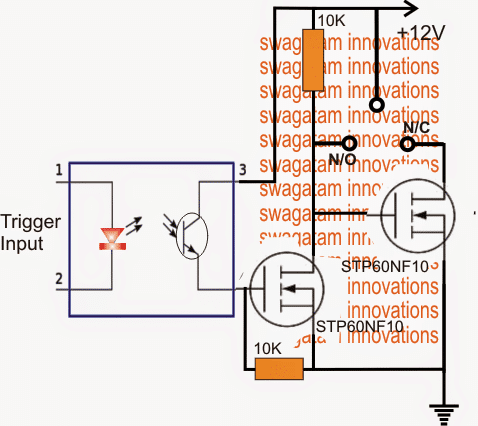

En kantudløsende fasedetektor bruges, når input- og outputfrekvenser er i pulsbølgeform, som er mindre end 50% arbejdscyklus. R-S flip flop bruges til fasedetektorerne, hvilket er vist i nedenstående figur. Til fra R-S klipklapper , er de to NOR-porte krydskoblet. Fasedetektorens output kan ændre sin logiske tilstand ved at udløse R-S flip flop. Den positive kant af indgangs- og udgangsfrekvenserne kan ændre fasedetektorens output.

Edge Trigger Phase Detector

Monolitisk fasedetektor

En monolitisk fasedetektor er af CMOS-type, dvs. IC 4044. Den er stærkt kompenseret fra den harmoniske følsomhed, og driftscyklusproblemerne opgives, da kredsløbet kun kan reagere på overgangen af indgangssignalet. I kritiske applikationer er det den mest feberede detektor. De uafhængige variationer af amplituden er fri for fasefejl, outputfejlspænding og driftscyklus for inputbølgeformerne.

Anvendelser af faselåst sløjfe

- FM-demodulationsnetværk til FM-operationer

- Det bruges i motorhastighedskontrol og sporingsfiltre.

- Det bruges i frekvensskiftende dekoder til demodulationsbærerfrekvenser.

- Det bruges i tide til digitale konvertere.

- Det bruges til reduktion af jitter, skæv undertrykkelse, urgendannelse.

Dette handler om den faselåste sløjfes funktions- og driftsprincip og dens applikationer. Vi håber, at oplysningerne i artiklen er nyttige for dig at vide noget om projektet og forstå det. Desuden, hvis du har spørgsmål vedrørende denne artikel og videre elektriske og elektroniske projekter du kan kommentere i nedenstående afsnit. Her er et spørgsmål til dig, hvad er den bedste måde at simulere PLL for stabilitet på?

Fotokreditter:

- Blokdiagram for PLL kredsløb i dag

- Eksklusiv ELLER fasedetektor sanfoundry

- Edge Trigger Phase Detector LEARNABOUT-ELEKTRONIK