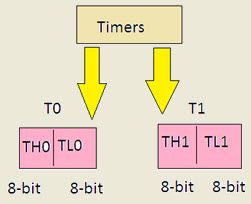

Tæller er en digital enhed, og udgangen fra tælleren inkluderer en foruddefineret tilstand baseret på urimpulsapplikationerne. Resultatet af tæller kan bruges til tæl antallet af impulser. Generelt består tællere af et flip-flop-arrangement, som kan være synkron tæller eller asynkron tæller. I synkron tæller gives kun et ur i / p til alle flip-flops, mens i asynkron tæller er o / p af flip flop er ursignalet fra det nærliggende. Anvendelserne af mikrokontrolleren har brug for optælling af udvendige begivenheder såsom nøjagtig intern tidsforsinkelse og frekvensen af pulstogene. Disse begivenheder bruges ofte i digitale systemer og computere. Begge disse begivenheder kan udføres ved hjælp af softwareteknikker, men softwareslynger til optælling giver ikke det nøjagtige resultat, lidt vigtigere funktioner udføres ikke. Disse problemer kan afhjælpes ved hjælp af timere og tællere i mikrokontrollerne, der bruges som afbrydelser.

Tællere

Typer af tællere

Tællere kan kategoriseres i forskellige typer alt efter den måde, de er uret på. De er

- Asynkrone tællere

- Synkrone tællere

- Asynkrone decennetællere

- Synkrone tiårstællere

- Asynkrone op-ned-tællere

- Synkron-op-ned-tællere

For bedre forståelse af denne type tællere diskuterer vi her nogle af tællerne.

Asynkrone tællere

Diagrammet for en 2-bit asynkron tæller er vist nedenfor. Det udvendige ur er kun forbundet med uret i / p på FF0 (første flip-flop). Så denne FF ændrer tilstanden ved den faldende kant for hver urpuls, men FF1 ændres kun, når den aktiveres af den faldende kant af Q o / p af FF0. På grund af den integrerede udbredelsesforsinkelse gennem en FF kan ændringen af i / p-urets puls og en ændring af Qo / p af FF0 aldrig forekomme nøjagtigt på samme tid. Så FF'erne kan ikke aktiveres samtidigt, hvilket genererer en asynkron operation.

Asynkrone tællere

Bemærk, at ændringerne af Q0, Q1 & CLK i ovenstående diagram for at lette er vist som samtidige, selvom dette er en asynkron tæller. Faktisk er der en lille forsinkelse b / n Q0, Q1 og CLK ændres.

Generelt er alle CLEAR i / ps forbundet, så før optællingen starter, kan en enkelt puls rydde alle FF'erne. Urpulsen, der føres ind i FF0, rippes gennem de nye tællere efter udbredelsesforsinkelser, såsom en krusning på vandet, deraf udtrykket Rippeltæller.

Kredsløbsdiagrammet for to bit krusningstælleren inkluderer fire forskellige tilstande, der hver består af en tællingsværdi. Ligeledes kan en tæller med n FF'er have 2N-tilstande. Antallet af stater i en tæller kaldes som dets modnummer. Derfor er en to-bit tæller en mod-4 tæller.

Asynkrone decennetællere

I den foregående tæller har 2n stater. Men tællere med tilstande mindre end 2n er også mulige. Disse er designet til at have nej. af stater i deres serie. Disse kaldes forkortede sekvenser, der opnås ved at køre tælleren til at genbruge, før de går gennem alle dens stater. En fælles modul for tællere med forkortet sekvens er 10. En tæller med 10-tilstande i sin serie kaldes en tiårstæller. Det implementerede tiårstællerkredsløb er angivet nedenfor.

Asynkront decennetællerdiagram

Når tælleren tæller til ti, vil alle FF'er blive ryddet. Bemærk, at kun Q1 og Q3 begge bruges til at afkode antallet af 10, der kaldes delvis afkodning. Samtidig har en af de andre stater fra 0-9 både Q1 og Q3 vil være høje. Serien med tiårstællertabellen er angivet nedenfor.

Sekvens af tiårstælleren

Asynkrone op-ned-tællere

I særlige applikationer skal en tæller kunne tælle både op og ned. Nedenstående kredsløb er en tre-bit op & ned-tæller, der tæller OP eller NED baseret på styresignalstatus. Når UP i / p er på 1 og NED i / p er på 0, vil NAND-porten mellem FF0 og FF1 gate den ikke-inverterede o / p (Q) af flip flop (FF0) ind i uret i / p af flip flop (FF1). Ligeledes vil den ikke-inverterede o / p af Flip Flop1 blive lukket gennem den anden NAND-port ind i uret i / p af flip-flop2. Derfor tæller tælleren op.

Asynkront op-ned-tællerkredsløbsdiagram

Når kontrol i / p (OP) er på 0 & NED er på 1, indgives den omvendte o / ps af flip-flop0 (FF0) og flip-flop1 (FF) separat i uret i / ps af FF1 & FF2 . Hvis FF'erne oprindeligt ændres til 0'er, vil tælleren gennemgå nedenstående serie, når i / p-impulser anvendes. Bemærk, at en asynkron op-ned-tæller er langsommere end en UP-tæller / ned-tæller på grund af en ekstra udbredelsesforsinkelse indført af NAND-portene.

Sekvens af den asynkrone op-ned-tæller

Synkrone tællere

I denne type tællere , er CLK i / ps for alle FF'erne forbundet sammen og aktiveres af i / p-impulser. Så alle FF'er skifter tilstand med det samme. Nedenstående kredsløbsdiagram er en tre-bit synkron tæller. Indgangene J og K på flip-flop0 er forbundet til HIGH. Flip-flop 1 har sin J & K i / ps tilsluttet o / p af flip-flop0 (FF0), og indgangene J & K til flip-flop2 (FF2) er forbundet til o / p af en AND-port, der tilføres ved o / ps af flip-flop0 og flip-flop1. Når begge udgangene fra FF0 & FF1 er HIGH. Den positive kant af den fjerde CLK-puls får FF2 til at ændre sin tilstand på grund af AND-porten.

Synkront tællerkredsløbsdiagram

Serien af tre-bit-tællertabellen er angivet nedenfor. Den største fordel ved disse tællere er, at der ikke er nogen stigende tidsforsinkelse, fordi alle FF'er er aktiveret parallelt. Den maksimale driftsfrekvens for denne synkron tæller vil således være betydeligt højere end for den ækvivalente ringtæller.

CLK Impulser af de synkrone tællere

Synkrone tiårstællere

Synkron tæller tæller fra 0-9 svarende til asynkron tæller og genbruger derefter igen nul. Denne proces udføres ved at køre 1010-staterne tilbage til 0000-tilstanden. Dette betegnes som trunkeret sekvens, der kan designes af nedenstående kredsløb.

Synkront tiårstællerdiagram

Fra serien på venstre bord kan vi observere det

- Q0 binder hver CLK-puls

- Q1 ændres ved den næste urpuls hver gang Q0 = 1 & Q3 = 0.

- Q2 ændres ved den næste urpuls hver gang Q0 = Q1 = 1.

- Q3 ændres ved den næste CLK-puls hver gang Q0 = 1, Q1 = 1 & Q2 = 1 (antal 7) eller når Q0 = 1 & Q3 = 1 (antal 9).

Sekvens af tælleren for synkron årti

Ovenstående egenskaber anvendes sammen med OG port eller ELLER port . Logikdiagrammet for dette er vist i ovenstående diagram.

Synkron-op-ned-tællere

En tre-bit synkron Up-Down-tæller, tabelform og serie er angivet nedenfor. Denne type tæller har en op-ned kontrol i / p svarende til asynkron op-ned tæller, der bruges til at styre tællerens retning gennem en bestemt serie.

Synkron kredsløbsdiagram for op-ned-tællere

Serien i tabellen viser

- Q0 binder på hver CLK-puls for både op- og ned-serier

- Når Q0 = 1 for op-serien, ændres tilstanden for Q1 på den næste CLK-puls.

- Når Q0 = 0 for down-serien, ændres tilstanden for Q1 på den næste CLK-puls.

- Når Q0 = Q1 = 1 for op-serien, ændres tilstanden for Q2 på den næste CLK-puls.

- Når Q0 = Q1 = 0 for down-serien, ændres tilstanden for Q2 på den næste CLK-puls.

Sekvensen af de synkrone årtællere

Ovenstående karakteristika anvendes med AND-porten, ELLER porten og IKKE-porten. Logikdiagrammet for dette er vist i ovenstående diagram.

Anvendelser af tællere

Anvendelserne på tællerne involverer hovedsageligt i digitale ure og i multiplexing. Det bedste eksempel på tælleren er parallel med seriel datakonverteringslogik, der diskuteres nedenfor.

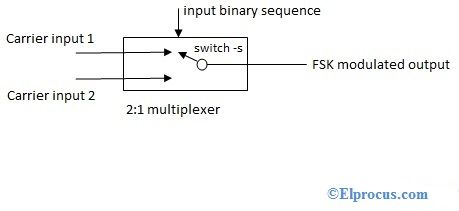

Et sæt bits, der udfører samtidigt på parallelle linjer, kaldes parallelle data. Et sæt bits, der udfører på en enkelt linje i en tidsserie, kaldes serielle data. Parallel-til-seriel datakonvertering udføres normalt ved hjælp af en tæller til at give en binær serie af dataene, vælg i / ps af en MUX som forklaret i nedenstående kredsløb.

Parallel-til-seriel datakonvertering

I ovenstående kredsløb består modulo-8-tæller af Q o / ps, der er forbundet til dataene, vælg i / ps af en 8-bit MUX . Den første 8-bit gruppe af parallelle data anvendes til input af MUX. Når tælleren gennemgår en binær serie fra 0-7, starter hver bit med D0, vælges serielt og føres gennem MUX til o / p-linjen. Efter 8-CLK impulser er databyte blevet ændret til et serielt format og sendt ud via transmissionslinjen. Derefter behandler tælleren tilbage til 0 og ændrer en anden parallelbyte serielt igen i den lignende proces.

Således handler dette om tællere og typer af tællere, som inkluderer asynkrone tællere, synkrontællere, asynkrone tiårtællere, synkrone tiårtællere, asynkrone op-ned-tællere og synkron op-ned-tællere. Desuden er enhver tvivl om dette emne eller timere og tællere i 8051 mikrokontroller bedes du kommentere i kommentarfeltet nedenfor.