ARM (Advanced RISC Machine) har lanceret flere processorer, der har forskellige funktioner såvel som de forskellige kerner til en lang række applikationer. Det første ARM-arkitekturdesign har 26-bit processorer, men nu nåede det 64-bit processorer. Den generelle udvidelse af ARM-produkter kan ikke kategoriseres i visse oplysninger. Men ARM-produkter kan forstås ud fra dens arkitektur. Standard ARM-serieprocessorer, der er tilgængelige på markedet, starter fra ARM7 til ARM11. Disse processorer har flere funktioner som cache, datatæt koblet hukommelse, MPU, MMU osv. Nogle af de vidt kendte ARM-processorserier er ARM926EJ-S, ARM7TDMI og ARM11 MPCore. Denne artikel er især beregnet til ARM7-baseret LPC2148 mikrokontroller arkitekturoversigt, som giver dig kort information om mikrokontrolleren arkitektur.

ARM7-baseret LPC2148 mikrokontrollerarkitektur

ARM7 er et 32-bit generelt formål mikroprocessor , og det tilbyder nogle af funktionerne som lidt strømforbrug og høj ydeevne. Arkitekturen for en ARM afhænger af principper for RISC . Den tilknyttede dekodningsmekanisme såvel som RISC-instruktionssættet er meget let, når vi sammenligner med mikroprogrammeret CISC -Kompleks instruktions sæt computere.

Pipeline-metoden bruges til behandling af alle blokke i arkitekturen. Generelt udføres et enkelt instruktions sæt, hvorefter dets efterkommer oversættes, & a 3rd-instruktion fås fra hukommelsen.

En eksklusiv arkitektonisk plan for ARM7 kaldes Thumb, og den er perfekt egnet til applikationer med høj lydstyrke, hvor kodens kompaktitet er et spørgsmål. ARM7 bruger også en eksklusiv arkitektur, nemlig Thumb. Det gør det perfekt egnet til forskellige applikationer ved hukommelsesbegrænsninger, hvor tætheden af kode er et spørgsmål.

ARM7-baseret mikrokontroller (LPC2148) Arkitektur

Afbryd kilder

Hver perifer enhed består af en enkelt afbrydelseslinie tilknyttet VIC (vektorafbrydelsescontroller), selvom den kan have forskellige afbrydelsesflag indeni. Individuelle interruptflag kan også betegne en eller flere afbrydelsesressourcer.

Flash-hukommelse på chip

Mikrocontrolleren LPC2141 / 42/44/46/48 inkluderer en flashhukommelse som henholdsvis 32 kilobyte, kilobyte, 128 kilobyte og 256 kilobyte. Denne flashhukommelse kan bruges til både datalagring og kode. Flashhukommelsesprogrammeringen kan udføres i systemet via den serielle port.

Programapplikationen kan også slettes, mens applikationen kører, hvilket tillader fleksibilitet med forbedring af datalagringsfelt firmware osv. På grund af valget af en arkitektonisk løsning til en on-chip bootloader er den tilgængelige hukommelse til mikrokontrollerne LPC2141 / 42 / 44/46/48 er 32 kilobyte, kilobyte, 128 kilobyte, 256 kilobyte og 500 kilobyte. Flashhukommelsen fra disse mikrokontrollere tilbyder 1, 00.000 sletning pr. Cyklus og databevarelse i mange år.

Pin Connect-blok

Denne blok tillader valgte stifter på den ARM7-baserede LPC2148 mikrokontroller til at have flere funktioner. Multiplexerne kan styres af konfigurationsregistrene til at tillade forbindelsen mellem stiften og perifere enheder på chip.

Periferiudstyr skal være koblet med de passende stifter, før de udløses, og før eventuelle tilsluttede afbrydelser er tilladt. Microcontroller-funktionaliteten kan defineres af pin-kontrolmodulet ved dets pin-valg af registre i et givet hardwaremiljø.

Efter omarrangering er alle porte i porte (port 0 og port 1) arrangeret som i / p ved de givne undtagelser. Hvis fejlretning er tilladt

Hvis fejlretning er tilladt, vil JTAG-stifterne gætte funktionaliteten af JTAG. Hvis et spor er tilladt, gætter sporingsnålene funktionens funktion. Stifterne, der er forbundet til I2C0- og I2C1-stifterne, er åbne.

GPIO- Generelt formål Parallel input / output

GPIO-registre styrer enhedens ben, der ikke er knyttet til en bestemt perifer funktion. Enhedens ben kan arrangeres som i / p [s eller o / ps. Individuelle registre giver mulighed for at rydde et hvilket som helst antal o / p'er samtidigt. Outputregistreringsværdien kan aflæses, og den aktuelle tilstand for portstifterne. Disse mikrocontrollere begynder en accelereret funktion over LPC200-enheder.

Generelle input / output-registre flyttes til processorbussen, der bruges til den bedst mulige I / O-tid.

- Disse registre er adresserbare byte.

- Den samlede værdi af en port kan være

- Den samlede værdi af porten kan skrives i den eneste instruktion

10-bit ADC (analog til digital konverter)

Mikrocontrollerne som LPC2141 eller 42 inkluderer to ADC-konvertere , og disse er kun 10-bit har en, og LPC2144 / 46/48 har to ADC'er, og disse er kun 10-bit lige tilnærmelses-ADC'er. Selvom ADC0 inkluderer 6-kanaler, og ADC1 har 8-kanaler. Antallet af tilgængelig ADC i / ps for LPC2141 eller 42 er således 6 & 14 for LPC2141 eller 42.

10-bit DAC (digital til analog konverter)

DAC giver disse mikrokontrollere mulighed for at producere en udskiftelig analog o / p og VREFer den største output af a digital til en analog spænding.

Device Controller-USB 2.0

Den universelle serielle bus består af 4-ledninger, og det giver support til kommunikation mellem et antal perifere enheder og værter. Denne controller tillader USB-båndbredden til tilslutning af enheder ved hjælp af en protokol baseret på tokenet.

Bussen understøtter frakobling af hot plugging og dynamisk samling af enhederne. Enhver kommunikation startes gennem værtscontrolleren. Disse mikrocontrollere er designet med en universal seriel busapparatcontroller, der tillader 12 Mbit / sek data erstattet af en USB-værtscontroller.

UART'er

Disse mikrocontrollere inkluderer to UART'er til standard transmittere og få datalinjer. I modsætning til tidligere mikrokontrollere (LPC2000) starter UART'er i mikrokontrollere LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 en delvis baudhastighedsgenerator, der bruges til begge UART'er, hvilket giver disse typer mikrokontroller mulighed for at opnå typiske baudhastigheder som 115200 ved hver krystalfrekvens over 2 MHz . Derudover udføres kontrolfunktionerne som CTS / RTS fuldstændigt i hardware.

Seriel I / O-controller til I2C-bus

Hver mikrokontroller fra LPC2141 / LPC2142 / LPC2144 / LPC2146 / LPC2148 inkluderer to I2C buscontrollere, og dette er tovejs. Inter-IC-styringen kan udføres ved hjælp af to ledninger, nemlig en SCL og SDA. Her er SDA & SCL seriel urlinie og seriel datalinje

Hvert apparat identificeres af en individuel adresse. Her kan sendere og modtagere arbejde i to tilstande som master mode / slave mode. Dette er en multi-master bus, og den kan administreres af en eller flere busmastere, der er knyttet til den. Disse mikrocontrollere understøtter op til 400 kbit / s bithastigheder.

SPI Seriel input / output-controller

Disse mikrocontrollere inkluderer en enkelt SPI-controller og beregnet til at håndtere adskillige mestre og slaver tilknyttet en bestemt bus.

Simpelthen en mester og en slave kan samtale over grænsefladen gennem hele specificeret datatransmission. I løbet af dette transmitterer masteren konstant en byte-af-data mod slaven, såvel som slaven konstant sender data til masteren.

SSP Seriel input / output-controller

Disse mikrocontrollere indeholder enkelt SSP, og denne controller er i stand til at behandle på en SPI, Microwire-bus eller 4-leder SSI. Det kan kommunikere med bussen fra flere mestre såvel som slaver

Men simpelthen en bestemt mester såvel som slave kan tale på bussen gennem en bestemt dataoverførsel. Denne mikrocontroller understøtter overførsel af fuld duplex med 4-16 bits datarammer, der bruges til datastrømmen fra master-slave såvel som fra slave-master.

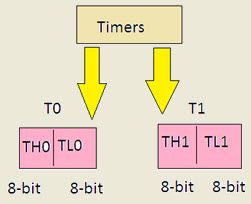

Timere / tællere

Timere og tællere er designet til at tælle PCLK-cyklusser (perifert ur) og producerer eventuelt afbrydelser baseret på 4-matchsregistre.

Og det består af fire capture i / ps for at fange værdien af en timer, når et i / p-signal ændrer sig. Der kunne vælges flere ben til at udføre en bestemt fangst. Disse mikrokontrollere kan beregne udvendige hændelser på indgangene til optagelse, hvis den mindste udvendige puls er ækvivalent. I dette arrangement kan ledige indfangningslinjer vælges som sædvanlig timeroptagelse i / ps.

Watchdog Timer

Watchdog-timeren bruges til at nulstille mikrocontrolleren på en rimelig tid. Når det er tilladt, vil timeren producere en nulstilling af et system, hvis forbrugerprogrammet ikke lykkes at genindlæse timeren på et fast tidsrum.

RTC-realtidsur

RTC er beregnet til at levere tællere til at beregne det tidspunkt, hvor tomgang eller normal driftsmetode vælges. RTC bruger en lille mængde strøm og er designet til passende batteridrevne arrangementer, hvor den centrale behandlingsenhed ikke fungerer konstant

Strømstyring

Disse mikrocontrollere understøtter to kondenserede strømtilstande som f.eks. Nedlukningstilstand og inaktiv tilstand. I inaktiv tilstand er udførelsen af instruktioner afbalanceret, indtil en afbrydelse eller RST opstår. Funktionerne i perifert udstyr opretholder drift gennem inaktiv tilstand og kan producere afbrydelser for at få CPU'en til at genstarte efterbehandling. Inaktiv tilstand fjerner den strøm, der bruges af CPU'en, controllere, hukommelsessystemer og indre busser.

I slukningstilstand deaktiveres oscillatoren, og IC'en får ingen indre ure. De perifere registre, processortilstand med registre, indre SRAM-værdier konserveres under sluk-tilstand, og chiplogikniveauerne udgangsstifter forbliver faste.

Denne tilstand kan afsluttes, og den fælles proces genstartes ved specifikke afbrydelser, der er i stand til at arbejde uden ure. Fordi chipdriften er afbalanceret, reducerer Power-down-tilstand chipudnyttelsen til næsten nul.

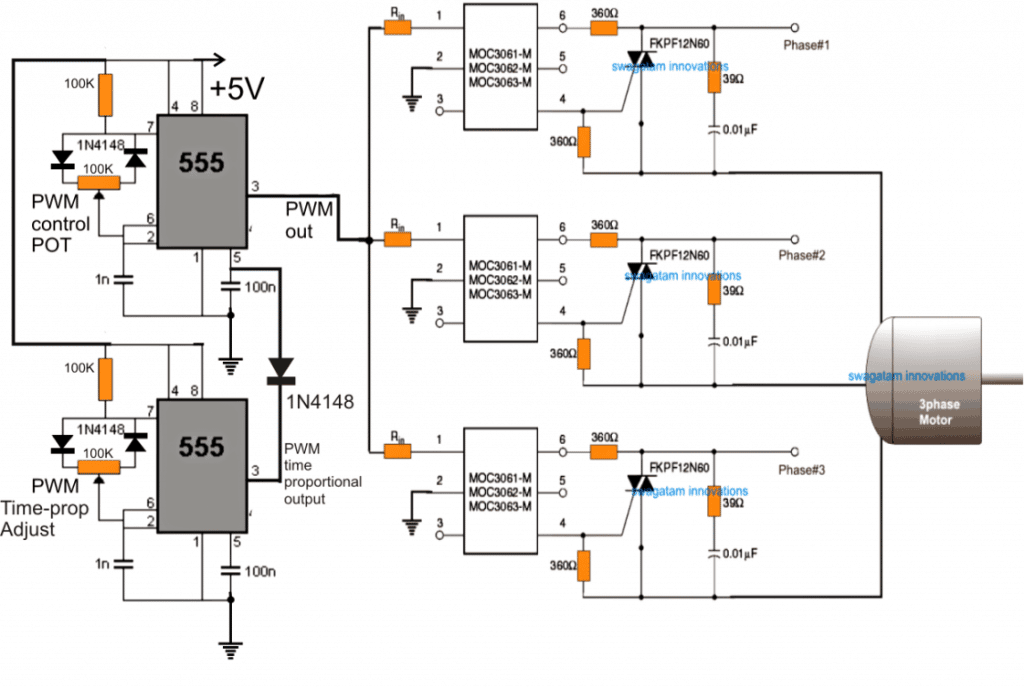

PWM-pulsbreddemodulator

PWM'erne er baseret på den normale timerblok og kommer også ind i alle funktionerne, selvom pulsbreddemodulatorfunktionen simpelthen er fastgjort på mikrokontrollere som LPC2141 / 42/44/46/48.

Timeren er beregnet til at beregne PCLK (perifert ur) cyklusser og producerer eventuelt afbrydelser, når bestemte timerværdier opstår baseret på 7-match-registre, og PWM-funktion afhænger også af matchregistreringshændelser.

Evnen til individuelt at styre stigende og faldende grænsepositioner gør det muligt at bruge pulsbreddemodulationen til flere applikationer. For eksempel bruger den typiske motorstyring med flerfase 3-ikke-overlappende udgange af PWM ved separat kontrol af hver pulsbredde såvel som positioner.

VPB-bus

VPB-skillelinjen løser sammenhængen mellem CCLK (processorur) og PCLK (ur, der bruges af perifere enheder). Denne skillevæg bruges til to formål. Den første anvendelse er at levere periferiudstyr med den foretrukne PCLK ved hjælp af VPB-bus, så de kan arbejde med den valgte hastighed på ARM-processoren. For at opnå dette kan denne bushastighed reduceres processorens urhastighed fra 1⁄ 2 -1⁄4.

Fordi denne bus skal fungere nøjagtigt ved opstart, og standardtilstanden ved RST (nulstilling) er, at bussen fungerer ved 1⁄4 af processorens urthastighed. Den anden anvendelse af dette er at tillade strømbesparelser, når en applikation ikke har brug for periferiudstyr for at arbejde med den samlede processorhastighed. Da VPB-skillelinjen er forbundet med output fra PLL, forbliver denne aktiv gennem en inaktiv tilstand.

Emulering og fejlretning

Mikrocontrolleren (LPC2141 / 42/44/46/48) holder emulering og debugging gennem seriel port-JTAG. En sporingsport tillader sporing af programmets udførelse. Sporingsfunktioner og fejlfindingskoncepter multiplexes med port1 og GPIO'er.

Kodesikkerhed

Kodesikkerhedsfunktionen i disse mikrokontrollere LPC2141 / 42/44/46/48 tillader en funktion at kontrollere, om den kan beskyttes eller fejles fra inspektion.

Således handler alt om ARM7-baseret LPC2148 mikrokontrollerarkitektur. Fra ovenstående artikel kan vi endelig konkludere, at ARM er en arkitektur, der bruges i mange processorer såvel som mikrokontrollere. Her er et spørgsmål til dig, hvad er arkitekturen for en ARM-processor?