I vores daglige liv støder vi på forskellige typer elektroniske gadgets. En af de teknologier, der fremkaldte en revolution i produktionen af elektronik, er “ Integreret kredsløb “. Denne teknologi reducerede størrelsen på elektroniske produkter ved at øge densiteten af logiske porte pr. chip. I dag har vi forskellige typer og konfigurationer af IC'er. Som vi observerer rundt, finder vi ud af, at nogle IC'er kun kan bruges til en bestemt applikation, mens nogle IC'er kan omprogrammeres og bruges til forskellige applikationer. Disse typer IC'er er navngivet som ASIC'er. Men hvordan adskiller de sig? Hvordan er det muligt at omprogrammere dem? Hvorfor kan nogle IC'er ikke omprogrammeres? Hop videre for at finde svar på disse spørgsmål.

Hvad er en ASIC (Application Specific Integrated Circuit)?

ASIC fuld form er Applikationsspecifik integreret kredsløb. Disse kredsløb er applikationsspecifikke, dvs. skræddersyede IC'er til en bestemt applikation. Disse er normalt designet fra rodniveau baseret på kravet til den bestemte applikation. Nogle af de grundlæggende applikationsspecifikke eksempler på integreret kredsløb er chips, der bruges i legetøj, den chip, der bruges til grænseflade mellem hukommelse og mikroprocessor osv ... Disse chips kan kun bruges til den ene applikation, som disse er designet til. Formentlig disse typer IC'er foretrækkes kun for de produkter, der har en stor produktionskørsel. Da ASIC'er er designet fra rodniveauet, har de høje omkostninger og anbefales kun til produktioner med stort volumen.

Den største fordel ved ASIC er reduceret chipstørrelse, da et stort antal funktionelle enheder i et kredsløb er konstrueret over en enkelt chip. Moderne ASIC inkluderer generelt en 32-bit mikroprocessor , hukommelsesblokke, netværkskredsløb osv ... En sådan type ASIC'er er kendt som System på chip . Med udviklingen inden for produktionsteknologi og øget forskning inden for designmetoder udvikles ASIC'er med forskellige niveauer af tilpasning.

Typer af ASIC

ASIC'er kategoriseres baseret på den tilpasningsmængde, som en programmør må udføre på en chip.

Typer af ASIC'er

Fuld brugerdefineret

I denne type design er alle logiske celler skræddersyet til specifik anvendelse, dvs. designeren skal specielt fremstille de logiske celler til kredsløbene. Alle masklag til samtrafik er tilpasset. Så programmør kan ikke ændre interconnections af chippen, og under programmering skal han være opmærksom på kredsløbets layout.

Et af de bedste eksempler på fuld tilpasset ASIC er en mikroprocessor. Denne type tilpasning giver designere mulighed for at bygge forskellige analoge kredsløb, optimerede hukommelsesceller eller mekaniske strukturer på en enkelt IC. Denne ASIC er dyr og meget tidskrævende at fremstille og designe. Det tager tid at designe disse IC'er er omkring otte uger.

Disse er normalt beregnet til applikationer på højt niveau. Maksimal ydelse, minimeret areal og højeste grad af fleksibilitet er vigtige funktioner i fuldt tilpasset design. Til sidst er risikoen høj i design, da de anvendte logiske celler, modstand osv ... kredsløbselementer ikke testes.

Semi-brugerdefineret

I denne type design er logiske celler taget fra standardbiblioteker, dvs. de er ikke håndlavede som i fuldt tilpasset design. Nogle masker er tilpasset, mens nogle er taget fra det foruddesignede bibliotek. Baseret på typen af logiske celler taget fra biblioteket og den tilladte mængde tilpasning til sammenkoblinger er disse ASIC'er opdelt i to typer - Standardcellebaseret ASIC og Gate Array-baseret ASIC.

1). Standard cellebaseret ASIC

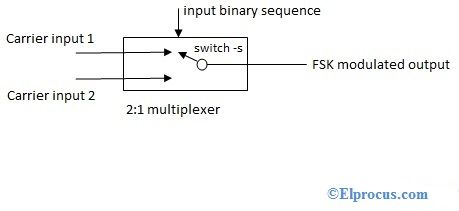

For at kende disse IC, lad os først forstå, hvad et standardcellebibliotek står for. Nogle af de logiske celler som f.eks OG porte ELLER porte , multiplexere, klipklapper er forud designet af designere ved hjælp af forskellige konfigurationer, standardiseret og gemt i form af et bibliotek. Denne samling er kendt som standardcellebibliotek.

Standard cellebaseret ASIC

I standardcellebaserede anvendes ASIC-logiske celler fra disse standardbiblioteker. På ASIC-chip består standardcelleområde eller fleksibel blok af standardceller arrangeret i form af rækker. Sammen med disse fleksible blokke anvendes megaceller som mikrokontroller eller endda mikroprocessorer on-chip. Disse megaceller er også kendt som megafunktioner, systemniveaumakroer, faste blokke, funktionelle standardblokke.

Ovenstående figur repræsenterer en standardcelle-ASIC med et enkelt standardcelleområde og fire faste blokke. Maskelag er tilpasset. Her kan designer placere standardceller hvor som helst på matricen. Disse er også kendt som C-BIC.

2). Gate Array-baseret ASIC

Denne type semi-brugerdefinerede ASIC er foruddefineret transistorer på siliciumskiven, dvs. designeren kan ikke ændre placeringen af transistorer til stede på matricen. Base array er det foruddefinerede mønster af gate array, og basis cellen er den mindste gentagne celle i base array.

Designeren har kun ansvar for at ændre sammenkobling mellem transistorer ved hjælp af de første par metallag i matricen. Designeren vælger fra gate array-biblioteket. Disse kaldes ofte som Masked Gate Array. Gate Array Baseret ASIC er af tre typer. De er Channeled Gate Array, Channel less gate array og en struktureret gate array.

a) Kanalport-array

I denne type gate-array er ledningspladsen tilbage mellem rækker af transistorer. Disse svarer til CBIC, da der er plads til sammenkobling mellem blokke, men i kanaliserede gate-array-cellerækker er faste i højden, mens dette rum i CBIC kan justeres.

Channeled Gate Array

Nogle af hovedfunktionerne i denne gate array er - denne gate array bruger foruddefinerede mellemrum mellem rækker til samtrafik. Produktionstiden er to dage til to uger.

b). Kanalmindre portarray

Der er ikke mere ledig plads tilbage til routing mellem cellerækker som set i den kanaliserede gate-array. Her foretages routing ovenfra gate array cellerne, da vi kan tilpasse forbindelsen mellem metal 1 og transistorer. Til routing lader vi transistorer ligge i vejen for routing ubrugte. Produktionstiden er cirka to uger.

Kanalmindre portarray

c). Structured Gate Array

Denne type gate array har en indlejret blok sammen med gate array rækker som vist ovenfor. Struktureret gate-array har en højere arealeffektivitet på CBIC. Ligesom Masked gate array har disse lavere omkostninger og hurtigere turnaround. Her udgør den faste størrelse af den integrerede funktion en begrænsning for det strukturerede gate array. For eksempel er dette gate-array et område, der er forbeholdt 32k bit controller, men hvis vi i en applikation kun kræver et område til 16k bit controller, bliver det resterende område spildt. Alle gate-arrayet har en behandlingstid på to dage til to uger og alle har tilpasset samtrafik.

Structured Gate Array

Programmerbar ASIC

Der er to typer programmerbare ASIC'er. De er PLD og FPGA

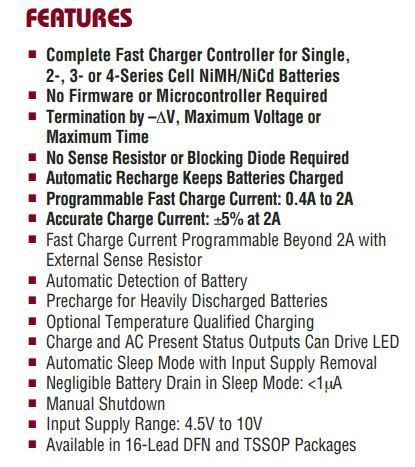

PLD'er (programmerbare logiske enheder)

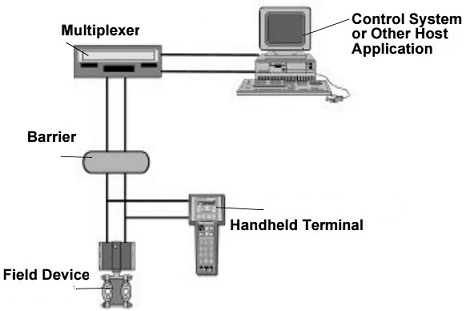

Dette er de standardceller, der er let tilgængelige. Vi kan programmere en PLD til at tilpasse en del af applikationen, så de betragtes som ASIC. Vi kan bruge forskellige metoder og software til at programmere en PLD. Disse indeholder en regelmæssig matrix af logiske celler, som normalt er programmerbar array-logik sammen med flip-flops eller låse. Her er sammenkoblinger til stede som en enkelt stor blok.

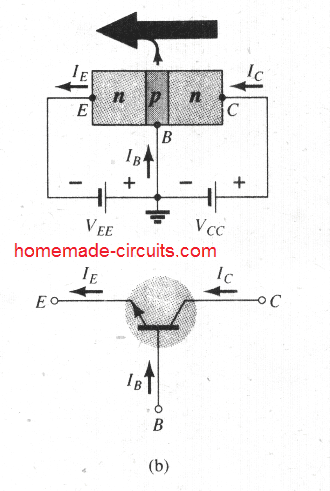

PROM er et almindeligt eksempel på denne IC. EPROM bruger MOS-transistorer som sammenkobling, så ved at anvende højspænding kan vi programmere det. PLD'er har ingen tilpassede logiske celler eller sammenkobling. Disse har en hurtig designomgang.

Programmerbare logiske enheder

FPGA'er (Field Programmable Gate Array)

Hvor PLD'er har programmerbar matrixlogik som logiske celler FPGA har gate array-lignende arrangement. PLD'er er mindre og mindre komplekse end FPGA'er. På grund af sin fleksibilitet og egenskaber erstatter FPGA TTL i mikroelektroniske systemer. Vending i design er kun et par timer.

Feltprogrammerbar portarray

Kernen består af programmerbare grundlæggende logiske celler, som kan udføre begge dele kombinerende og sekventiel logik . Vi kan programmere logiske celler og sammenkoble ved hjælp af nogle metoder. Grundlæggende logiske celler er omgivet af matricen af programmerbare sammenkoblinger, og kernen er omgivet af programmerbare I / O-celler.

FPGA består normalt af konfigurerbare logiske blokke, konfigurerbare I / O-blokke, programmerbare sammenkoblinger, urkredsløb, ALU, hukommelse, dekodere.

Vi har set de forskellige typer ASIC til rådighed. Lad os nu forstå, når alle disse tilpasninger og sammenkoblinger udføres under fremstillingen.

Applikationsspecifikt integreret kredsløb (ASIC) Design Flow

Design af en ASIC udføres trin for trin. Denne rækkefølge af trin er kendt som ASIC Design Flyde. Trin for designflow er angivet i nedenstående flowdiagram.

ASIC Design Flow

Designindgang: På dette trin implementeres designens mikroarkitektur ved hjælp af hardwarebeskrivelsessprog som VHDL, Verilog og System Verilog.

Logisk syntese: På dette trin udarbejdes en netliste over logiske celler, der skal bruges, typer af sammenkoblinger og alle andre dele, der kræves til applikationen, ved hjælp af HDL.

Systempartitionering: På dette trin opdeler vi den dyse, der er stort i størrelse, i stykker i ASIC-størrelse.

Pre-Layout Simulation: På dette trin udføres en simuleringstest for at kontrollere, om designet indeholder fejl.

Gulvplanlægning: Ved dette trin er blokke af netlist arrangeret på chippen.

Placering: På dette trin bestemmes placeringen af celler inde i blokken.

Routing: På dette trin trækkes forbindelser mellem blokke og celler. Ekstraktion: På dette trin bestemmer vi de elektriske egenskaber som modstandsværdi og kapacitansværdien af sammenkobling.

Simulation efter layout: Før indsendelsen af modellen til fremstilling foretages denne simulering for at kontrollere, om systemet fungerer korrekt sammen med en masse sammenkobling.

Eksempler på ASIC

Efter at have kendt de forskellige egenskaber ved ASIC, lad os nu se nogle eksempler på ASIC.

Standard cellebaseret ASIC: LCB 300k, 500k fra LSI Logic Company, SIG1, 2, 3 familier fra ABB Hafo Inc., GCS90K fra GCS Plessey.

Gate Array-produkter: AUA20K fra Harris Semiconductor, SCX6Bxx fra National Semiconductors, TGC / TEC-familier fra Texas Instruments.

PLD-produkter: PAL-familie med avancerede mikroenheder, GAL-familie fra Philips Semiconductors, XC7300 og EPLD fra XILINX.

FPGA-produkter: XC2000, XC3000, XC4000, XC5000-serien fra XILINX, pASIC1 fra QuickLogic, MAX5000 fra Altera.

Anvendelser af ASIC

Det unikke ved ASIC har revolutioneret måden, hvorpå elektronik fremstilles. Disse reducerede formstørrelserne, mens de øger densiteten af logiske porte pr. chip. ASIC'er foretrækkes normalt til applikationer på højt niveau. ASIC-chip bruges som IP-kerner til satellitter, ROM-produktion, Mikrocontroller og forskellige typer applikationer inden for medicin og forskning. En af de mest populære applikationer fra ASIC er BITCOIN MINER.

Bitcoin Miner

Minedrift af kryptokurrency kræver større strøm og højhastighedshardware. En generel CPU kan ikke levere en så højere computerkapacitet ved høj hastighed. ASIC bitcoin minearbejdere er chips indbygget i specialdesignede bundkort og strømforsyninger , konstrueret i en enkelt enhed. Det er en bevidst designet hardware helt ned til chipniveauet til bitcoin-minedrift. Disse enheder kan kun udføre algoritmen for kun en enkelt kryptovaluta. For en anden type kryptokurrency har vi sandsynligvis brug for en anden minearbejder.

Fordele og ulemper ved ASIC

Det fordelene ved ASIC inkluderer følgende.

- Den lille størrelse af ASIC gør det til et stort valg til sofistikerede større systemer.

- Da et stort antal kredsløb er bygget over en enkelt chip, forårsager dette applikationer med høj hastighed.

- ASIC har lavt strømforbrug.

- Da de er systemet på chippen, er kredsløb til stede side om side. Så der kræves meget minimal routing for at forbinde forskellige kredsløb.

- ASIC har ingen timingproblemer og konfiguration efter produktion.

Det ulemper ved ASIC inkluderer følgende.

- Da disse er tilpassede chips, giver de lav fleksibilitet til programmering.

- Da disse chips skal designes fra rodniveauet, koster de pr. Enhed.

- ASIC har større tid til markedsmargen.

ASIC vs FPGA

Forskellen mellem ASIC og FPGA inkluderer følgende.

ASIC | FPGA |

| Ikke omprogrammerbar | Omprogrammerbar |

| Foretrukket til højvolumenproduktioner | Foretrukket til produktioner med lavt volumen |

| Disse er applikationsspecifikke | Anvendes som prototyper af et system |

| Energieffektiv kræver mindre strøm | Mindre energieffektiv kræver mere strøm |

| Disse er permanente kredsløb, der ikke kan opgraderes fra tid til anden. | Meget velegnet til applikationer, hvor kredsløbet skal opgraderes fra tid til anden, såsom mobiltelefonchips, basestationer osv |

Således handler alt om en oversigt over Applikationsspecifik integreret kredsløb . Opfindelsen af ASIC har forårsaget en enorm ændring i den måde, elektronik bruges på. Vi bruger ASIC i vores daglige liv i form af forskellige applikationer. Hvilke applikationer af ASIC er du stødt på? Hvilken type ASIC har du arbejdet med?