De mest kraftfulde og vigtige funktioner er afbrydelser i 8051 mikrokontroller . I de fleste af realtidsprocesserne skal den faktiske opgave standses i et stykke tid - for at håndtere visse forhold korrekt - det tager den nødvendige handling - og skal derefter vende tilbage til hovedopgaven. For at udføre en sådan type programmer er afbrydelser nødvendige. Det adskiller sig fuldstændigt fra afstemningsmetoden, hvor processoren skal kontrollere sekventielt hver enhed og spørge, om tjenesten er påkrævet eller ej, mens den bruger mere processortid.

Afbryder i 8051 mikrokontroller

Afbrydelser i 8051-mikrocontroller er mere ønskelige for at reducere den regelmæssige statuskontrol af interface-enheder eller indbyggede enheder. Interrupt er en begivenhed, der midlertidigt suspenderer hovedprogrammet, overfører kontrollen til et specielt kodeafsnit, udfører den hændelsesrelaterede funktion og genoptager hovedprogrammets flow, hvor det var sluttet.

Interrupts er af forskellige typer som software og hardware, maskerbare og ikke-maskerbare, faste og vektorafbrydelser og så videre. Interrupt Service Routine (ISR) kommer ind i billedet, når der opstår afbrydelse, og beder derefter processoren om at tage passende handling for afbrydelsen, og efter ISR-udførelse springer controlleren ind i hovedprogrammet.

Typer af afbrydelser i 8051 mikrokontroller

8051-mikrocontrolleren kan genkende fem forskellige begivenheder, der får hovedprogrammet til at afbryde fra den normale udførelse. Disse fem kilder til afbrydelser i 8051 er:

- Timer 0 overløbsafbrydelse - TF0

- Timer 1 overløbsafbrydelse - TF1

- Ekstern hardwareafbrydelse - INT0

- Ekstern hardwareafbrydelse - INT1

- Seriel kommunikationsafbrydelse - RI / TI

Timer og serielle afbrydelser genereres internt af mikrocontrolleren, mens de eksterne afbrydelser genereres af yderligere interface enheder eller kontakter, der er tilsluttet eksternt til mikrokontrolleren. Disse eksterne afbrydelser kan kantudløses eller niveauudløses. Når der opstår en afbrydelse, udfører mikrocontrolleren afbrydelsesrutinen, så hukommelsesplaceringen svarer til den afbrydelse, der muliggør den. Afbrydelsen svarende til hukommelsesplaceringen er angivet i nedenstående afbrydelsesvektortabel.

Afbryd vektor tabel

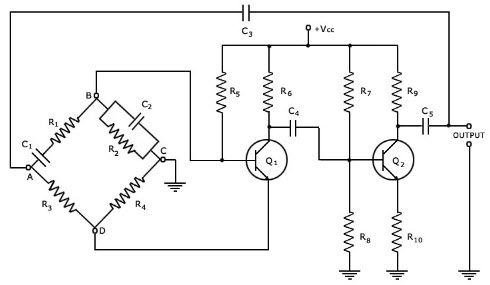

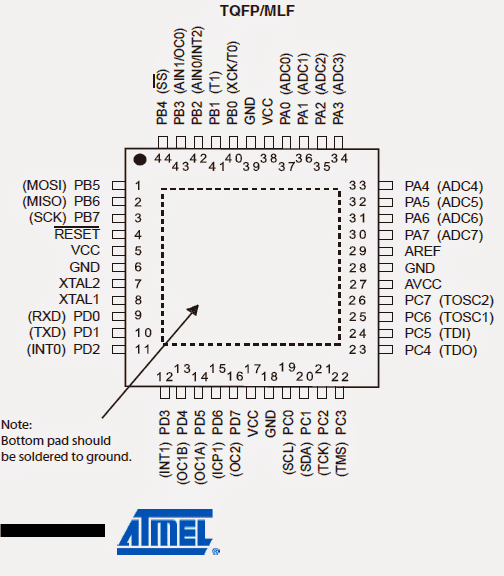

Interrupt Structure of 8051 Micro controller

Ved 'RESET' deaktiveres alle afbrydelser, og derfor skal alle disse afbrydelser aktiveres af en software. I alle disse fem afbrydelser, hvis nogen eller alle er aktiveret, indstiller dette de tilsvarende afbrydelsesflag som vist i figuren. Alle disse afbrydelser kan indstilles eller ryddes bitvis i et specielt funktionsregister, der er Interrupt Enabled (IE), og dette afhænger igen af prioriteten, som udføres af IP-interruptprioritetsregisteret.

Afbryd struktur af 8051 mikrokontroller

Interrupt Enable (IE) Register: Dette register er ansvarlig for at aktivere og deaktivere afbrydelsen. Det er et bit adresserbart register, hvor EA skal indstilles til et for at muliggøre afbrydelser. Den tilsvarende bit i dette register muliggør særlig afbrydelse som timer, eksterne og serielle indgange. I nedenstående IE-register aktiverer bit svarende til 1 afbrydelsen og 0 deaktiverer afbrydelsen.

Interrupt Enable (IE) Register

Interrupt Priority Register (IP): Det er også muligt at ændre interruptsprioritetsniveauerne ved at indstille eller rydde den tilsvarende bit i Interrupt Priority (IP) -registret som vist i figuren. Dette gør det muligt for afbrydelsen med lav prioritet at afbryde afbrydelsen med høj prioritet, men forbyder afbrydelsen ved en anden afbrydelse med lav prioritet. Tilsvarende kan afbrydelsen med høj prioritet ikke afbrydes. Hvis disse afbrydelsesprioriteter ikke er programmeret, udfører mikrokontrolleren på foruddefineret måde, og dens rækkefølge er INT0, TF0, INT1, TF1 og SI.

IP-register

TCON-register: Ud over de to ovennævnte registre specificerer TCON-registret typen af ekstern afbrydelse til 8051-mikrocontrolleren, som vist i figuren. De to eksterne afbrydelser, hvad enten kant eller niveau udløses, specificerer ved dette register af et sæt eller ryddes af passende bits i det. Og det er også et lidt adresserbart register.

TCON-register

Afbryd programmering i 8051

1. Timer Interrupt Programmering

Timer 0 og Timer 1-afbrydelser genereres af timeregistreringsbitene TF0 og TF1. Disse afbryder programmering med C-kode involverer:

- Valg af timeren ved at konfigurere TMOD-registeret og dets funktion.

- Valg og indlæsning af startværdierne for TLx og THx til passende tilstande.

- Aktivering af IE-registre og tilsvarende timerbit i den.

- Indstilling af timer-kørselsbit for at starte timeren.

- Skrivning af underrutinen til timeren i den krævede tid og klar timerværdi TRx i slutningen af subrutinen.

Timer Interrupt Programmering

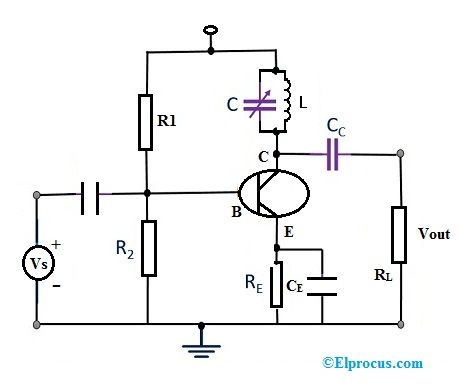

2. ekstern hardware afbrydelse programmering

8051 mikrocontrollere består af to eksterne hardwareafbrydelser: INT0 og INT1 som diskuteret tidligere. Disse aktiveres ved pin 3.2 og pin 3.3. Disse kan kantudløses eller niveauudløses. I niveauudløsning muliggør lav ved pin 3.2 afbrydelse, mens ved pin 3.2 - høj til lav overgang muliggør kantudløst interrupt. Denne kantudløsning eller niveauudløsning bestemmes af TCON-registret, der er blevet diskuteret ovenfor. Det programmeringsprocedure i 8051 er som følgende:

- Aktivér den tilsvarende bit af ekstern afbrydelse i IE-registeret.

- Hvis det er niveauudløsende, skal du bare skrive den underrutine, der passer til denne afbrydelse, ellers aktiver TCON-registerbiten, der svarer til den kantudløste afbrydelse - hvad enten det er INT0 eller INT1.

Programmering af ekstern hardwareafbrydelse

3. seriel kommunikation afbryde programmering

Serielle kommunikationsafbrydelser kommer i billedet, når der er behov for at sende eller modtage data. Da der er indstillet en interruptbit til både TI (Transfer Interrupt) og RI (Receiver Interrupt) -flag, skal Interrupt Service-rutinen undersøge disse flag for at kende den aktuelle afbrydelse.

Den logiske ELLER-operation af disse to flag (RI og TI) forårsager denne afbrydelse, og den ryddes kun af softwaren. Her bruges et specielt register SCON til styring meddelelse ved at aktivere de tilsvarende bits i den.

- Konfigurer IE-registeret for at muliggøre seriel afbrydelse

- Konfigurer SCON-registret til modtagelse eller overførsel

- Skriv subrutine til denne afbrydelse med passende funktion og ryd TI- eller RI-flag med i denne rutine.

Seriel interrupt programmering

Dette handler om afbrydelser i 8051 mikrocontroller, typer, deres struktur og programmering. Håber du måske har modtaget gode oplysninger fra denne artikel. Du kan også skrive til os i nedenstående kommentarsektion for realtidsimplementering af mikrokontroller projekter så vi kan hjælpe dig med en bedre praktisk oplevelse.

Fotokreditter

- Afbryder i 8051 mikrokontroller af ingeniørgarage

- Afbryd vektor tabel ved 8051projekter

- Afbryd struktur af 8051 mikrokontroller af børste

- Interrupt Enable (IE) Register via elektroner

- IP-register ved kredsløb i dag

- TCON Tilmeld dig ved kredsløb i dag