Der var en æra, hvor computere var så enorme i størrelse, at det nemt var nødvendigt at få plads til at installere dem. Men i dag er de så udviklede, at vi endda let kan bære dem som notesbøger. Innovationen, der gjorde dette muligt, var konceptet med integrerede kredsløb. I Integrerede kredsløb , et stort antal aktive og passive elementer sammen med deres forbindelser er udviklet over en lille siliciumplade, typisk 50 x 50 mil i tværsnit. De grundlæggende processer, der følges til produktion af sådanne kredsløb, inkluderer epitaksial vækst, maskeret urenhedsdiffusion, oxidvækst og oxidetsning ved anvendelse af fotolitografi til fremstilling af mønster.

Komponenterne over waferen inkluderer modstande, transistorer, dioder, kondensatorer osv ... Det mest komplicerede element at fremstille over IC'er er transistorer. Transistorer er af forskellige typer såsom CMOS, BJT, FET. Vi vælger den type transistorteknologi, der skal implementeres over en IC baseret på krav. Lad os i denne artikel blive fortrolig med begrebet CMOS fabrikation (eller) fabrikation af transistorer som CMOS.

CMOS fabrikation

For mindre strømforsyningskrav CMOS-teknologi bruges til implementering af transistorer. Hvis vi har brug for et hurtigere kredsløb, implementeres transistorer igen IC bruger BJT . Fabrikation af CMOS-transistorer da IC kan udføres i tre forskellige metoder.

N-brønd / P-brøndsteknologien, hvor n-type diffusion udføres over et p-type substrat eller p-type diffusion udføres over henholdsvis n-type substrat.

Det Twin brønd teknologi , hvor NMOS og PMOS transistor udvikles over waferen ved samtidig diffusion over en epitaksial vækstbase snarere end et substrat.

Processen med silicium på isolator, hvor i stedet for at bruge silicium som substrat, anvendes et isoleringsmateriale til at forbedre hastigheden og følsomheden for lås-op.

N- well / P- well Technology

CMOS kan opnås ved at integrere begge dele NMOS og PMOS transistorer over den samme siliciumskive. I N – brøndteknologi diffunderes en n-type brønd på et p-type substrat, mens det i P-brønd er omvendt.

Trin til fremstilling af CMOS

Det CMOS fabrikationsproces flyde udføres ved hjælp af tyve grundlæggende fabrikationstrin, mens de fremstilles ved hjælp af N-well / P-well-teknologi.

Oprettelse af CMOS ved hjælp af N-brønd

Trin 1: Først vælger vi et substrat som basis for fabrikation. For N-brønd vælges et P-type siliciumsubstrat.

Underlag

Trin 2 - Oxidation: Den selektive diffusion af urenheder af n-typen opnås ved anvendelse af SiO2 som en barriere, der beskytter dele af skiven mod kontaminering af substratet. SiOtoer lagt ud ved oxidationsproces, der udsættes for substratet for ilt og brint af høj kvalitet i et oxidationskammer ved ca. 10000c

Oxidation

Trin 3 - Dyrkning af fotoresist: På dette trin for at tillade selektiv ætsning udsættes SiO2-laget for fotolitografiprocessen. I denne proces coates waferen med en ensartet film af en lysfølsom emulsion.

Dyrkning af fotoresist

Trin 4 - Maskering: Dette trin er fortsættelsen af fotolitografiprocessen. I dette trin laves et ønsket mønster af åbenhed ved hjælp af en stencil. Denne stencil bruges som en maske over fotoresist. Underlaget udsættes nu for UV-stråler fotoresist til stede under de eksponerede maskeregioner bliver polymeriseret.

Maskering af fotoresist

Trin 5 - Fjernelse af ikke-eksponeret fotoresist: Masken fjernes, og det ueksponerede område af fotoresist opløses ved at udvikle wafer under anvendelse af et kemikalie, såsom trichlorethylen.

Fjernelse af fotoresist

Trin 6 - ætsning: Waferen nedsænkes i en ætsningsopløsning af flussyre, som fjerner oxiden fra de områder, gennem hvilke dopanter skal diffundere.

Ætsning af SiO2

Trin 7 - Fjernelse af hele fotoresistlag: Under ætsningsproces , de dele af SiO2, der er beskyttet af fotoresistlaget, påvirkes ikke. Fotoresistmasken fjernes nu med et kemisk opløsningsmiddel (varmt H2SO4).

Fjernelse af fotoresistlag

Trin 8 - Dannelse af N-brønd: Urenheder af n-typen diffunderes ind i p-typen substrat gennem det eksponerede område og danner således en N-brønd.

Dannelse af N-brønd

Trin 9 - Fjernelse af SiO2: Laget af SiO2 fjernes nu ved anvendelse af flussyre.

Fjernelse af SiO2

Trin 10 - Afsætning af polysilikon: Fejljusteringen af porten til en CMOS transistor ville føre til den uønskede kapacitans, som kunne skade kredsløbet. Så for at forhindre denne 'Selvjusterede portproces' foretrækkes, hvor gateområder dannes inden dannelsen af kilde og afløb ved hjælp af ionimplantation.

Afsætning af polysilikon

Polysilicon bruges til dannelse af porten, fordi den kan modstå den høje temperatur, der er større end 80000c når en wafer udsættes for udglødningsmetoder til dannelse af kilde og afløb. Polysilicon deponeres ved hjælp af Kemisk deponeringsproces over et tyndt lag gateoxid. Denne tynde gateoxid under Polysilicon-laget forhindrer yderligere doping under gateområdet.

Trin 11 - Dannelse af portregion: Bortset fra de to regioner, der kræves til dannelse af porten til NMOS og PMOS transistorer den resterende del af Polysilicon fjernes.

Dannelse af portregion

Trin 12 - Oxidationsproces: Et oxidationslag aflejres over waferen, der fungerer som et skjold til videre diffusions- og metalliseringsprocesser .

Oxidationsproces

Trin 13 - Maskering og diffusion: Til fremstilling af regioner til diffusion af n-urenheder ved hjælp af maskeringsproces laves der små huller.

Maskering

Ved hjælp af diffusionsproces er der udviklet tre n + regioner til dannelse af terminaler af NMOS.

N-diffusion

Trin 14 - Fjernelse af oxid: Oxidlaget fjernes.

Fjernelse af oxid

Trin 15 - P-type diffusion: Svarende til n-typen diffusion til dannelse af terminaler af PMOS p-type diffusion udføres.

P-type diffusion

Trin 16 - Lægning af tykt feltoxid: Før der dannes metalterminaler, lægges der et tykt feltoxid ud for at danne et beskyttende lag for de områder af skiven, hvor der ikke kræves nogen terminaler.

Tykt feltoxidlag

Trin 17 - Metallisering: Dette trin bruges til dannelse af metalterminaler, som kan tilvejebringe sammenkoblinger. Aluminium spredes på hele skiven.

Metallisering

Trin 18 - Fjernelse af overskydende metal: Det overskydende metal fjernes fra skiven.

Trin 19 - Dannelse af terminaler: I hullerne dannet efter fjernelse af overskydende metalterminaler dannes til sammenkoblingerne.

Dannelse af terminaler

Trin 20 - Tildeling af terminalnavne: Navne tildeles terminalerne på NMOS og PMOS transistorer .

Tildeling af terminalnavne

Fremstilling af CMOS ved hjælp af P well Technology

P-brøndsprocessen svarer til N-brøndsprocessen bortset fra at her anvendes n-type substrat, og der udføres p-type diffusioner. For enkelheds skyld foretrækkes N-brøndsprocessen.

Twin Tube fabrikation af CMOS

Ved hjælp af Twin-tube-processen kan man kontrollere forstærkningen af P- og N-type enheder. Forskellige trin involveret i fabrikation af CMOS ved hjælp af metoden med to rør er som følgende

- Et let doteret n- eller p-type substrat tages, og det epitaksiale lag anvendes. Epitaksial lag beskytter låseproblemet i chippen.

- De siliciumlag med høj renhed med målt tykkelse og nøjagtig dopantkoncentration dyrkes.

- Dannelse af rør til P og N brønd.

- Tynd oxidkonstruktion til beskyttelse mod forurening under diffusionsprocesser.

- Kilde og afløb dannes ved hjælp af ionimplantationsmetoder.

- Udskæringer er lavet til fremstilling af portioner til metalkontakter.

- Metallisering udføres til tegning af metalkontakter

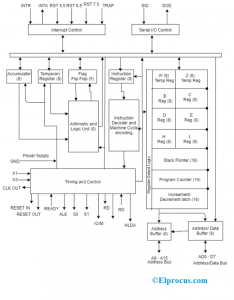

CMOS IC-layout

Det øverste billede af til CMOS fabrikation og layout er givet. Her kan forskellige metalkontakter og N-brønds diffusioner ses tydeligt.

CMOS IC-layout

Således handler det hele om CMOS fabrikationsteknikker . Lad os overveje en 1-i-kvadratisk wafer opdelt i 400 chips overfladeareal 50 mil med 50 mils. Det tager et areal på 50 mil2 at fremstille en transistor. Derfor indeholder hver IC 2 transistorer, så der er 2 x 400 = 800 transistorer bygget på hver wafer. Hvis der behandles 10 skiver hver batch, kan der produceres 8000 transistorer samtidigt. Hvilke komponenter har du observeret på en IC?