Forskellige typer digitale systemer er konstrueret af meget få typer grundlæggende netværkskonfigurationer såsom AND gate, NAND gate, Eller gate osv ... Disse elementære kredsløb bruges igen og igen i forskellige topologiske kombinationer. Ud over at udføre logik skal digitale systemer også gemme binære tal. For disse hukommelsesceller, også kendt som KLIPKLAPPER' s er designet. At udføre nogle funktioner såsom binær tilføjelse. Derfor at udføre sådanne funktioner, kombinationer af logiske porte og FLIP-FLOP'er er designet over en enkelt chip IC. Disse IC'er udgør de praktiske byggesten i de digitale systemer. En af sådanne byggesten, der bruges til binær tilføjelse, er Carry Look-ahead Adder.

Hvad er en Carry Look-ahead Adder?

En digital computer skal indeholde kredsløb, der kan udføre aritmetiske operationer såsom addition, subtraktion, multiplikation og division. Blandt disse er addition og subtraktion de grundlæggende operationer, mens multiplikation og division er henholdsvis den gentagne addition og subtraktion.

For at udføre disse operationer implementeres 'Adder-kredsløb' ved hjælp af grundlæggende logiske porte. Adder kredsløb udvikles som Half-adder, Full-adder, Ripple-carry Adder og Carry Look-ahead Adder.

Blandt disse Carry Look-ahead Adder er det hurtigere adder-kredsløb. Det reducerer udbredelsesforsinkelsen, som opstår under tilsætning, ved at bruge mere komplekse hardwarekredsløb. Det er designet ved at omdanne krusningsbærende Adder-kredsløb, således at bærerens logik ændres til to-niveau-logik.

4-bit Carry Look-ahead Adder

I parallelle tilføjere gives bæreoutputtet for hver fulde adder som en bæreindgang til den næste højere ordens tilstand. Derfor er disse tilføjere det ikke muligt at producere bære- og summeoutput fra en hvilken som helst tilstand, medmindre en bæreindgang er tilgængelig for denne tilstand.

Så for beregning at forekomme, skal kredsløbet vente, indtil bærebiten spredes til alle stater. Dette inducerer forsinkelse af bæreformering i kredsløbet.

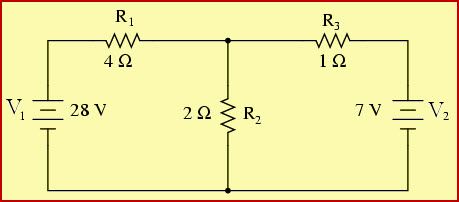

4-bit-Ripple-Carry-Adder

Overvej 4-bit krusningsbæreradderkredsløbet ovenfor. Her kan summen S3 produceres så snart input A3 og B3 er givet. Men bære C3 kan ikke beregnes, før bærebiten C2 anvendes, mens C2 afhænger af C1. Derfor, for at producere endelige steady-state-resultater, skal bærer sig til at sprede sig gennem alle staterne. Dette øger bæreudbredelsesforsinkelsen af kredsløbet.

Fortplantningsforsinkelsen af addereren beregnes som 'udbredelsesforsinkelsen for hver gate gange antallet af trin i kredsløbet'. Til beregning af et stort antal bits skal der tilføjes flere trin, hvilket gør forsinkelsen meget værre. Derfor blev Carry Look-ahead Adder introduceret for at løse denne situation.

For at forstå funktionen af en Carry Look-ahead Adder, er en 4-bit Carry Look-ahead Adder beskrevet nedenfor.

4-bit-Carry-Look-ahead-Adder-Logic-Diagram

I denne adderer er bæreindgangen på et hvilket som helst trin i adderen uafhængig af de bærebiter, der genereres i de uafhængige trin. Her afhænger output fra et hvilket som helst trin kun af de bits, der tilføjes i de foregående trin, og den bærende input, der blev leveret i begyndelsestrinet. Derfor behøver kredsløbet på ethvert trin ikke at vente på generering af bærebit fra det forrige trin, og bærebit kan evalueres på et hvilket som helst tidspunkt.

Sandhedstabel over Carry Look-ahead Adder

For at udlede sandhedstabellen for denne adder introduceres to nye udtryk - Carry generer og bær propagate. Carry generer Gi = 1, når der genereres en bærer Ci + 1. Det afhænger af Ai og Bi-indgange. Gi er 1, når både Ai og Bi er 1. Derfor beregnes Gi som Gi = Ai. Bi.

Carry propagated Pi er forbundet med forplantningen af carry fra Ci til Ci + 1. Det beregnes som Pi = Ai ⊕ Bi. Sandhedstabellen for denne adder kan udledes ved at ændre sandhedstabellen for en fuld adder.

Ved hjælp af Gi- og Pi-udtrykkene er Sum Si og Carry Ci + 1 angivet som nedenfor -

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Derfor kan bærebitene C1, C2, C3 og C4 beregnes som

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0). P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1). P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Det kan observeres ud fra ligningerne, der bærer Ci + 1, afhænger kun af bæringen C0, ikke af de mellemliggende bærebit.

Carry-Look-ahead-Adder-Truth-Table

Kredsløbsdiagram

Ovenstående ligninger er implementeret ved hjælp af to-niveau kombinations kredsløb sammen med AND, ELLER porte, hvor porte antages at have flere indgange.

Carry-Output-Generation-Circuit-of-Carry-Look-ahead-Adder

Carry Look-ahead Adder-kredsløbet fra 4-bit er angivet nedenfor.

4-bit-Carry-Look-ahead-Adder-Circuit-Diagram

8-bit og 16-bit Carry Look-ahead Adder kredsløb kan designes ved at kaskade 4-bit adder kredsløbet med bærelogik.

Fordele ved Carry Look-ahead Adder

I denne adder reduceres udbredelsesforsinkelsen. Bæreoutputtet på ethvert trin er kun afhængig af den indledende bærebit i begyndelsestrinet. Ved hjælp af denne adder er det muligt at beregne de mellemliggende resultater. Denne adder er den hurtigste adder, der bruges til beregning.

Ansøgninger

High-speed Carry Look-ahead Adders bruges som implementeret som IC'er. Derfor er det let at integrere huggeren i kredsløb. Ved at kombinere to eller flere tilføjere kan beregninger af højere boolske funktioner gøres let. Her er stigningen i antallet af porte også moderat, når den bruges til højere bits.

For denne Adder er der en afvejning mellem område og hastighed. Når det bruges til højere bitberegninger, giver det høj hastighed, men kredsløbets kompleksitet øges også, hvilket øger det område, der er optaget af kredsløbet. Denne adder implementeres normalt som 4-bit moduler, som kaskaderes sammen, når de bruges til højere beregninger. Denne adder er dyrere sammenlignet med andre tilføjere.

Til boolsk beregning på computere bruges addere regelmæssigt. Charles Babbage implementerede en mekanisme til at foregribe bærebit i computere for at reducere forsinkelsen forårsaget af krusningsbærere . Under design af et system er beregningshastigheden den højeste afgørende faktor for en designer. I 1957 patenterede Gerald B. Rosenberger den moderne Binary Carry Look-ahead Adder. Baseret på analysen af gate forsinkelse og simulering, udføres eksperimenter for at ændre kredsløbet for denne addder for at gøre det endnu hurtigere. For en n-bit bærer blik fremad adderer, hvad er udbredelsesforsinkelsen, når en forsinkelse for hver port er 20?

Billedkredit