På nuværende tidspunkt består alle elektriske og elektroniske enheder, som vi bruger i vores daglige liv, af integrerede kredsløb, der er fremstillet ved at anvende fremstillingsprocessen for halvlederenheder. Det elektroniske kredsløb er skabt på en wafer, der består af rene halvledermaterialer såsom silicium og anden halvleder forbindelser med flere trin, der involverer fotolithografi og kemiske processer.

Processen med produktion af halvleder blev startet fra Texas i begyndelsen af 1960'erne og strakte sig derefter over hele verden.

BiCMOS-teknologi

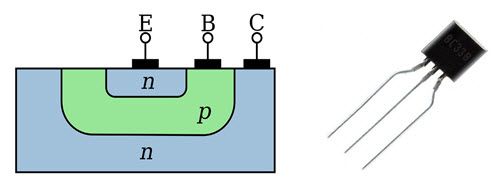

Dette er en af de største halvlederteknologier og er en højt udviklet teknologi, der i 1990'erne inkorporerer to separate teknologier, nemlig bipolar junction transistor og CMOS transistor i et enkelt moderne integreret kredsløb. Så for at give denne teknologi bedre, kan vi kort se på CMOS-teknologi og bipolar teknologi.

BiCMOS CME8000

Den viste figur er den første analog / digital modtager IC og er en BiCMOS integreret modtager med meget høj følsomhed.

CMOS-teknologi

Det er et supplement til MOS-teknologi eller CSG (Commodore Semiconductor Group), som blev startet som kilde til fremstilling af elektroniske regnemaskiner. Derefter bruges komplementær MOS-teknologi kaldet CMOS-teknologi til at udvikle de integrerede kredsløb såsom digital logiske kredsløb sammen med mikrokontroller s og mikroprocessorer. CMOS-teknologi giver fordel ved mindre strømforsyning og lav støjmargen med høj pakningstæthed.

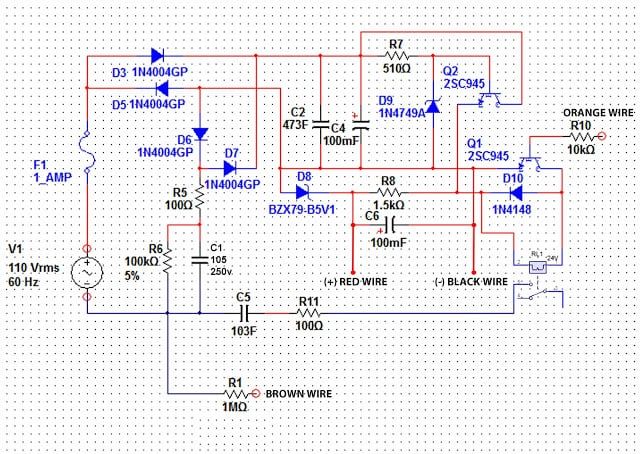

CMOS CD74HC4067

Figuren viser brugen af CMOS-teknologi til fremstilling af digitalstyrede switch-enheder.

Bipolar teknologi

Bipolære transistorer er en del af integrerede kredsløb, og deres drift er baseret på to typer halvledermateriale eller afhænger af begge typer ladebærerhuller og elektroner.Disse er generelt klassificeret i to typer som PNP og NPN , klassificeret baseret på doping af dets tre terminaler og deres polariteter. Det giver høj skifte samt input / output hastighed med god støjydelse.

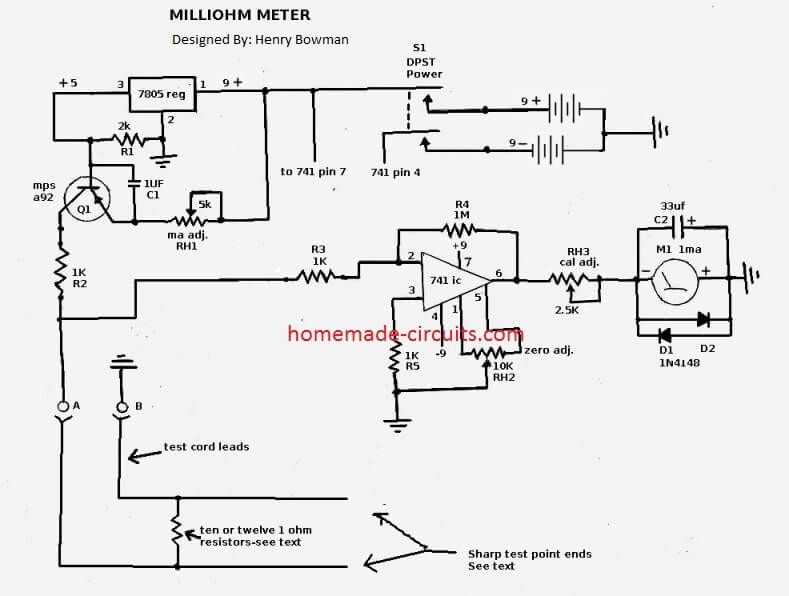

Bipolar AM2901CPC

Figuren viser brugen af bipolar teknologi i RISC-processor AM2901CPC.

BiCMOS Logic

Det er en kompleks behandlingsteknologi, der giver NMOS- og PMOS-teknologier, der er sammensmeltede hinanden med fordelene ved at have et meget lavt strømforbrug, bipolar teknologi og høj hastighed i forhold til CMOS-teknologi.

14 trin til BiCMOS fabrikation

BiCMOS-fabrikationen kombinerer fremstillingen af BJT og CMOS, men blot variation er en realisering af basen. De følgende trin viser BiCMOS-fabrikationsprocessen.

Trin 1: P-substrat er taget som vist i nedenstående figur

P-substrat

Trin 2: P-substratet er dækket med oxidlaget

P-substrat med oxidlag

Trin 3: En lille åbning er lavet på oxidlaget

Åbning foretages på oxidlaget

Trin 4: N-type urenheder er stærkt doteret gennem åbningen

N-type urenheder er stærkt doteret gennem åbningen

Trin 5: P - Epitaxy-laget dyrkes på hele overfladen

Epitaxy-laget dyrkes på hele overfladen

Trin 6 : Igen er hele laget dækket af oxidlaget, og der laves to åbninger gennem dette oxidlag.

to åbninger er lavet gennem oxidlaget

Trin 7 : Fra åbningerne lavet gennem oxidlag diffunderer n-type urenheder til dannelse af n-brønde

urenheder af n-typen diffunderes til dannelse af n-brønde

Trin 8: Tre åbninger laves gennem oxidlaget for at danne tre aktive enheder.

Tre åbninger laves gennem oxidlaget for at danne tre aktive enheder

Trin 9: Portterminalerne til NMOS og PMOS er dannet ved at dække og mønstre hele overfladen med Thinox og Polysilicon.

Portterminalerne til NMOS og PMOS er dannet med Thinox og Polysilicon

Trin 10: P-urenhederne tilsættes for at danne BJT-baseterminalen og lignende, N-type urenheder er stærkt doteret for at danne emitterterminal for BJT, kilde og afløb af NMOS og til kontaktformål doteres N-type urenheder i N-brønden samler.

P-urenheder tilsættes for at danne BJT's basisterminal

Trin 11: For at danne kilde- og afløbsregioner af PMOS og for at komme i kontakt i P-baseregionen er urenheder af P-typen stærkt doteret.

P-type urenheder er stærkt doteret for at danne kilde- og dræningsområder for PMOS

Trin 12: Derefter dækkes hele overfladen med det tykke oxidlag.

Hele overfladen er dækket af det tykke oxidlag

Trin 13: Gennem det tykke oxidlag er snitene mønstrede til at danne metalkontakterne.

Udskæringerne er mønstrede til at danne metalkontakterne

Trin 14 : Metalkontakterne er lavet gennem de udskæringer, der er lavet på oxidlaget, og terminalerne er navngivet som vist i nedenstående figur.

Metalkontakter skabes gennem snit og terminaler navngives

Fremstillingen af BICMOS er vist i ovenstående figur med en kombination af NMOS, PMOS og BJT. I fremstillingsprocessen anvendes nogle lag, såsom kanalstopimplantat, tykt lagoxidation og beskyttelsesringe.

Fremstillingen vil være teoretisk vanskelig for at inkludere både teknologierne CMOS og bipolar. Parasitisk bipolære transistorer produceres utilsigtet er et problem med fabrikation under behandling af p-brønd og n-brønd CMOS. Til fremstilling af BiCMOS tilføjes mange yderligere trin til finjustering af bipolære og CMOS-komponenter. Derfor stiger omkostningerne ved den samlede fabrikation.

Kanalstop implanteres i halvlederindretninger som vist i ovenstående figur ved hjælp af implantation eller diffusion eller andre metoder for at begrænse spredning af kanalareal eller for at undgå dannelse af parasitiske kanaler.

Eventuelle høje impedansnoder kan forårsage overfladelækstrømme og for at undgå strømmen på steder, hvor strømmen er begrænset, anvendes disse beskyttelsesringe.

Fordele ved BiCMOS-teknologi

- Analog forstærkerdesign letter og forbedres ved anvendelse af CMOS-kredsløb med høj impedans, da input og resterende realiseres ved hjælp af bipolære transistorer.

- BiCMOS er i det væsentlige energisk over for temperatur- og procesvariationer, der giver gode økonomiske overvejelser (høj procentdel af primeenheder) med mindre variation i elektriske parametre.

- Høj belastningsstrømssænkning og sourcing kan leveres af BiCMOS-enheder efter behov.

- Da det er en gruppe af bipolare og CMOS-teknologier, kan vi bruge BJT, hvis hastighed er en kritisk parameter, og vi kan bruge MOS, hvis strøm er en kritisk parameter, og den kan drive høje kapacitansbelastninger med reduceret cyklustid.

- Det har lav strømforsyning end bipolar teknologi alene.

- Denne teknologi fandt hyppige anvendelser i analoge strømstyrings kredsløb og forstærker kredsløb såsom BiCMOS forstærker.

- Det er velegnet til input / udgangsintensive applikationer, tilbyder fleksible input / output (TTL, CMOS og ECL).

- Det har fordelen ved forbedret hastighedsydelse sammenlignet med CMOS-teknologi alene.

- Lås usårbarhed.

- Den har tovejs kapacitet (kilde og afløb kan udskiftes efter behov).

Ulemper ved BiCMOS-teknologi

- Fremstillingsprocessen for denne teknologi består af både CMOS og bipolære teknologier, der øger kompleksiteten.

- På grund af stigning i fabrikationsprocessens kompleksitet øges også fremstillingsomkostningerne.

- Da der er flere enheder, dermed mindre litografi.

BiCMOS teknologi og applikationer

- Det kan analyseres som OG funktion af høj densitet og hastighed.

- Denne teknologi bruges som en alternativ af de tidligere bipolare, ECL og CMOS på markedet.

- I nogle applikationer (hvor der er et begrænset budget til strøm) er BiCMOS-hastighedens ydeevne bedre end bipolar.

- Denne teknologi er velegnet til intensive input / output applikationer.

- Anvendelserne af BiCMOS var oprindeligt i RISC-mikroprocessorer snarere end traditionelle CISC-mikroprocessorer.

- Denne teknologi udmærker sig i sine applikationer, hovedsageligt inden for to områder af mikroprocessorer såsom hukommelse og input / output.

- Det har en række applikationer i analoge og digitale systemer, hvilket resulterer i, at den enkelte chip spænder over den analog-digitale grænse.

- Det overgår hullet, der muliggør krydsning af handlingsforløb og kredsløbsmargener.

- Det kan bruges til prøve- og hold-applikationer, da det giver højimpedansindgange.

- Dette bruges også i applikationer som adders, mixere, ADC og DAC.

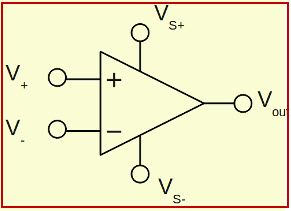

- At erobre begrænsningerne ved bipolar og CMOS operationelle forstærkere BiCMOS-processerne bruges til at designe de operationelle forstærkere. I operationelle forstærkere ønskes egenskaber med høj forstærkning og høj frekvens. Alle disse ønskede egenskaber kan opnås ved at bruge disse BiCMOS forstærkere.

BiCMOS-teknologien sammen med fabrikation, fordele, ulemper og anvendelser diskuteres kort i denne artikel. For bedre forståelse af denne teknologi, bedes du sende dine forespørgsler som dine kommentarer nedenfor.

Fotokreditter: